基于FPGA的IMU数据同步采集系统的制作方法

基于fpga的imu数据同步采集系统

技术领域

1.本实用新型属于数据采集技术领域,具体涉及一种基于fpga的imu数据同步采集系统。

背景技术:

2.一般的imu包含了3个陀螺仪和3个加速度计,测量物体在三维空间中的角速度和加速度,同时采集各自的温度和环境温度。目前捷联惯导系统要求启动速度快,对准时间短,需要确保imu数据采集实时性。同时,为了实现高精度导航解算,需要包含陀螺数据、加速度计数据、温度数据和卫星等多种数据融合,且各类数据通道较多和通讯速率较快,因此imu数据采集方法必须具有丰富的接口能力,支持可扩展和重构。传统的imu数据采集方法通过dsp和cpld实现,虽然该设计具有多通道的收发能力,但是数据采集接口能力不足,不具有可扩展性。另外dsp与cpld数据通讯时会占用dsp过多的外部中断,容易造成通讯冲突,引起数据丢失;数据采集一般通过定时循环查询方式,接口通过模拟开关复选复用,需要定时设置软件循环采集;采集数据存储和读取依靠外部扩展flash存储器实现,存储速度受flash速度限制,传输数据位宽较低,因此,针对上述问题,有必要进行改进。

技术实现要素:

3.本实用新型解决的技术问题:提供一种基于fpga的imu数据同步采集系统,采用精准的时钟控制模块生成的时钟信号,确保信号逻辑采集及处理模块信号和数据处理通讯模对各路数据采集与处理的同步性和完整性,利用fpga并行采集特点,实现3路rs422接口、3路正负脉冲接口和6路a/d转换接口同步、并行、实时和高速采集,并将采集数据自动存储,适用于对imu数据采集实时性及同步性要求较高和具有扩展性要求的应用场合。

4.本实用新型采用的技术方案:基于fpga的imu数据同步采集系统,包括信号输入模块、信号逻辑采集及处理模块、时钟控制模块和数据处理通讯模块,所述信号输入模块包括光纤陀螺仪输出的3路陀螺串口信号、石英加速度计输出的3路加速度脉冲信号和数字温度传感器输出的6路a/d模拟温度信号,所述信号逻辑采集及处理模块、时钟控制模块和数据处理通讯模块均嵌入fpga芯片上,所述3路陀螺串口信号、3路加速度脉冲信号和6路a/d模拟温度信号分别与信号逻辑采集及处理模块上对应的3路rs422接口、3路正负脉冲接口和6路a/d转换接口连接,所述时钟控制模块分别与信号逻辑采集及处理模块和数据处理通讯模块连接并由时钟控制模块为信号逻辑采集及处理模块和数据处理通讯模块提供各路数据同步采集与处理的时钟信号。

5.其中,所述信号逻辑采集及处理模块包括3路rs422串口可编辑逻辑电路、3路正负脉冲计数可编辑逻辑电路、6路a/d转换可编辑逻辑电路和双口ram存储器,所述数据处理通讯模块包括微处理器,3路所述rs422串口可编辑逻辑电路的第一输入端通过3路rs422接口与光纤陀螺仪连接,3路所述正负脉冲计数可编辑逻辑电路的第一输入端通过3路正负脉冲接口与石英加速度计连接,6路所述a/d转换可编辑逻辑电路的第一输入端通过6路a/d转换

接口与数字温度传感器连接,3路所述rs422串口可编辑逻辑电路、3路正负脉冲计数可编辑逻辑电路、6路a/d转换可编辑逻辑电路的输出端与双口ram存储器的输入端连接,并通过3路rs422串口可编辑逻辑电路、3路正负脉冲计数可编辑逻辑电路、6路a/d转换可编辑逻辑电路控制双口ram存储器的地址线、数据线和读写控制线完成采样数据存储及存储地址的自动切换;所述双口ram存储器的输出端通过数据总线与微处理器的输入端连接实现微处理器对双口ram存储器内采集数据的读取,所述微处理器通过总线与目标机连接实现目标机与微处理器的数据交互通讯。

6.进一步地,3路所述rs422串口可编辑逻辑电路包括接收逻辑电路和发送逻辑电路,3路所述rs422串口可编辑逻辑电路的串口设置为握手通讯方式,3路所述rs422串口可编辑逻辑电路定时发送命令字到发送通道并由串口响应后接收数据。

7.进一步地,3路所述正负脉冲计数可编辑逻辑电路包括去抖、计数及采样逻辑电路,3路所述正负脉冲计数可编辑逻辑电路接收到正负脉冲后在时钟控制模块生成的采样时钟信号控制下对采样数据进行去抖逻辑后消除噪声引起的数据误判,3路所述正负脉冲计数可编辑逻辑电路处理后的有效脉冲数据存储到双口ram存储器中。

8.进一步地,6路所述a/d转换可编辑逻辑电路包括a/d转换控制逻辑电路、通道自动切换逻辑电路和数据采样存储逻辑电路,所述时钟控制模块生成的a/d时钟信号控制6路a/d转换可编辑逻辑电路将各通道串并转换得到的并行数据存储到双口ram存储器中。

9.进一步地,所述时钟控制模块包括时钟控制器,所述时钟控制器为时钟发生器逻辑电路,所述时钟控制器的输入端与高精度晶振连接,所述时钟控制器以高精度晶振生成的系统时钟为基准,通过时钟控制器生成采样时钟信号、数据读取中断时钟信号、a/d时钟信号和串口时钟控制信号。

10.进一步地,所述时钟控制器的第一输出端输出通过中断控制器与微处理器连接,并为微处理器提供用于读取双口ram存储器内数据的数据读取中断时钟信号,所述中断时钟信号为延迟采集时钟信号;所述时钟控制器的第二输出端与3路rs422串口可编辑逻辑电路和3路正负脉冲计数可编辑逻辑电路的第二输入端连接,并为3路rs422串口可编辑逻辑电路和3路正负脉冲计数可编辑逻辑电路提供采样时钟信号,所述时钟控制器的第三输出端与3路rs422串口可编辑逻辑电路的第三输入端连接,并为3路rs422串口可编辑逻辑电路提供串口时钟控制信号,所述时钟控制器的第四输出端与6路a/d转换可编辑逻辑电路的第二输入端连接,并为6路a/d转换可编辑逻辑电路提供a/d时钟信号。

11.本实用新型与现有技术相比的优点:

12.1、本技术方案采用精准的时钟控制模块生成的时钟信号,确保信号逻辑采集及处理模块信号和数据处理通讯模对各路数据采集与处理的同步性和完整性;

13.2、本技术方案利用fpga并行采集特点,实现3路rs422接口、3路正负脉冲接口和6路a/d转换接口同步、并行、实时和高速采集,并将采集数据自动存储,适用于对imu数据采集实时性及同步性要求较高和具有扩展性要求的应用场合;

14.3、本技术方案采用在fpga芯片上嵌入微处理器和双口ram存储器,用于和导航计算机通过数据总线进行数据交互,并采用高精度晶振作为时钟输入源,在fpga中通过时钟控制器生成其它模块所需的时钟信号,保证时钟信号的精度和同源,从而保证时间同步性;

15.4、本技术方案采用fpga芯片上的中断管理器控制微处理器的数据读取,读取数据

的中断时钟信号与采样时钟信号相差固定时间,保证数据采集完整性及实时性,通过1路中断实现采样数据读取,减少中断次数;

16.5、本技术方案采用fpga芯片上嵌入可编程逻辑电路,实现数据的采集,可编程逻辑电路执行速度快,指令周期为纳秒级,可满足高速数据采集要求,具有可扩展性和复用性,可实现3路rs422接口、3路正负脉冲接口和6路a/d转换接口并行采集,保证多通道之间同步性。

附图说明

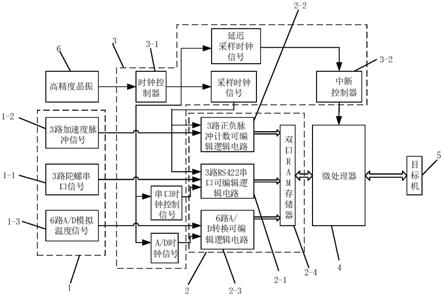

17.图1为本实用新型原理框图。

具体实施方式

18.下面结合附图1描述本实用新型的一种实施例,从而对技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。

19.在本实用新型的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位,以特定的方位构造和操作,因此,不能理解为对本实用新型的限制。

20.基于fpga的imu数据同步采集系统,包括信号输入模块1、信号逻辑采集及处理模块2、时钟控制模块3和数据处理通讯模块4,所述信号输入模块包括光纤陀螺仪输出的3路陀螺串口信号1

‑

1、石英加速度计输出的3路加速度脉冲信号1

‑

2和数字温度传感器输出的6路a/d模拟温度信号1

‑

3,所述信号逻辑采集及处理模块2、时钟控制模块3和数据处理通讯模块4均嵌入fpga芯片上,所述3路陀螺串口信号1

‑

1、3路加速度脉冲信号1

‑

2和6路a/d模拟温度信号1

‑

3分别与信号逻辑采集及处理模块2上对应的3路rs422接口、3路正负脉冲接口和6路a/d转换接口连接,所述时钟控制模块3分别与信号逻辑采集及处理模块2和数据处理通讯模块4连接并由时钟控制模块3为信号逻辑采集及处理模块2和数据处理通讯模块4提供各路数据同步采集与处理的时钟信号。

21.信号逻辑采集及处理模块具体如下所示:所述信号逻辑采集及处理模块2包括3路rs422串口可编辑逻辑电路2

‑

1、3路正负脉冲计数可编辑逻辑电路2

‑

2、6路a/d转换可编辑逻辑电路2

‑

3和双口ram存储器2

‑

4,所述数据处理通讯模块4包括微处理器,3路所述rs422串口可编辑逻辑电路2

‑

1的第一输入端通过3路rs422接口与光纤陀螺仪连接,3路所述正负脉冲计数可编辑逻辑电路2

‑

2的第一输入端通过3路正负脉冲接口与石英加速度计连接,6路所述a/d转换可编辑逻辑电路2

‑

3的第一输入端通过6路a/d转换接口与数字温度传感器连接,3路所述rs422串口可编辑逻辑电路2

‑

1、3路正负脉冲计数可编辑逻辑电路2

‑

2、6路a/d转换可编辑逻辑电路2

‑

3的输出端与双口ram存储器2

‑

4的输入端连接,并通过3路rs422串口可编辑逻辑电路2

‑

1、3路正负脉冲计数可编辑逻辑电路2

‑

2、6路a/d转换可编辑逻辑电路2

‑

3控制双口ram存储器2

‑

4的地址线、数据线和读写控制线完成采样数据存储及存储地址的自动切换;所述双口ram存储器2

‑

4的输出端通过数据总线与微处理器的输入端连接实现微处理器对双口ram存储器2

‑

4内采集数据的读取,所述微处理器通过总线与目标机5连接实现目标机5与微处理器的数据交互通讯。

22.上述结构中,在fpga芯片中嵌入microblaze处理器作为微处理器用于读取和解析数据、同目标机5通过32位总线实现数据交互,嵌入双口ram存储器2

‑

4用于数据存储。

23.其中,3路rs422串口可编辑逻辑电路2

‑

1具体如下:3路所述rs422串口可编辑逻辑电路2

‑

1包括接收逻辑电路和发送逻辑电路,3路所述rs422串口可编辑逻辑电路2

‑

1的串口设置为握手通讯方式,3路所述rs422串口可编辑逻辑电路2

‑

1定时发送命令字到发送通道并由串口响应后接收数据。

24.3路正负脉冲计数可编辑逻辑电路2

‑

2具体如下:3路所述正负脉冲计数可编辑逻辑电路2

‑

2包括去抖、计数及采样逻辑电路,3路所述正负脉冲计数可编辑逻辑电路2

‑

2接收到正负脉冲后在时钟控制模块3生成的采样时钟信号控制下对采样数据进行去抖逻辑后消除噪声引起的数据误判,3路所述正负脉冲计数可编辑逻辑电路2

‑

2处理后的有效脉冲数据存储到双口ram存储器2

‑

4中。

25.6路a/d转换可编辑逻辑电路2

‑

3具体如下:6路所述a/d转换可编辑逻辑电路2

‑

3包括a/d转换控制逻辑电路、通道自动切换逻辑电路和数据采样存储逻辑电路,所述时钟控制模块3生成的a/d时钟信号控制6路a/d转换可编辑逻辑电路2

‑

3将各通道串并转换得到的并行数据存储到双口ram存储器2

‑

4中,一个通道接收完成后由逻辑电路控制自动切换下一通道。

26.时钟控制模块3具体如下:所述时钟控制模块3包括时钟控制器3

‑

1,所述时钟控制器3

‑

1为时钟发生器逻辑电路,所述时钟控制器3

‑

1的输入端与高精度晶振6连接,所述时钟控制器3

‑

1以高精度晶振6生成的系统时钟为基准,通过时钟控制器3

‑

1生成采样时钟信号、数据读取中断时钟信号、a/d时钟信号和串口时钟控制信号;采用高精度晶振6提供时钟基准信号,时钟信号输入fpga芯片内部时钟控制器3

‑

1,经倍频生成系统时钟信号;

27.时钟控制模块3与信号逻辑采集及处理模块2的连接具体如下:所述时钟控制器3

‑

1的第一输出端输出通过中断控制器3

‑

2与微处理器连接,并为微处理器提供用于读取双口ram存储器2

‑

4内数据的数据读取中断时钟信号,所述中断时钟信号为延迟采集时钟信号;所述时钟控制器3

‑

1的第二输出端与3路rs422串口可编辑逻辑电路2

‑

1和3路正负脉冲计数可编辑逻辑电路2

‑

2的第二输入端连接,并为3路rs422串口可编辑逻辑电路2

‑

1和3路正负脉冲计数可编辑逻辑电路2

‑

2提供采样时钟信号,所述时钟控制器3

‑

1的第三输出端与3路rs422串口可编辑逻辑电路2

‑

1的第三输入端连接,并为3路rs422串口可编辑逻辑电路2

‑

1提供串口时钟控制信号,所述时钟控制器3

‑

1的第四输出端与6路a/d转换可编辑逻辑电路2

‑

3的第二输入端连接,并为6路a/d转换可编辑逻辑电路2

‑

3提供a/d时钟信号。

28.具体实施步骤如下:

29.第一步:配置微处理器,时钟控制模块3和双口ram存储器2

‑430.首先建立系统工程,嵌入microblaze微处理器,配置最小系统,生成系统顶层文件;然后在工程开发界面进入edk开发套件,依次加入时钟控制器3

‑

1和双口ram存储器2

‑

4;最后将时钟控制器3

‑

1与微处理器总线连接,配置系统时钟频率为100mhz,生成系统时钟输出端口,依次将各部件时钟信号与系统时钟端口连接;将双口ram存储器2

‑

4端口a与微处理器连接,双口ram存储器2

‑

4端口b作为输入端口与可编辑逻辑电路连接;双口ram存储器2

‑

4容量配置为16k,总线位宽配置为32位;

31.第二步:编写可编辑逻辑电路

32.1)时钟发生器逻辑电路

33.使用verilog hdl语言设计时钟发生器逻辑电路,以系统时钟作为参考基准,设计生成1ms采样时钟信号,串口时钟控制信号和4.1mhz a/d时钟信号;以系统时钟和系统复位信号作为输入,设计4个时钟计数寄存器,当寄存器计数值达到设定值时,输出时钟信号作为其它可编程逻辑电路控制时钟输入;

34.时钟发生器逻辑电路的程序源代码如下:

35.reg[16:0]counter_1ms_period;

[0036]

reg[3∶0]counter_10ms_period;

[0037]

reg[31∶0]timer_1ms;

[0038]

wire lock_1khz;

[0039]

wire clk_1mhz;

[0040]

always@(posedge sysclk or posedge sysrst)

[0041]

if(sysrst)counter_1ms_period<=#117

′

h0;

[0042]

else if(counter_1ms_period==79999)counter_1ms_period<=#117

′

h0;

[0043]

else counter_1ms_period<=#1counter_1ms_period+1

′

b1;

[0044]

assign#1 external_ims_intr_to_cpu1=(counter_1ms_period[3∶0]==13

′

h0);//0~15

[0045]

assign#1lock_1khz=(counter_1ms_period==13

′

h9c40);//80000超前0.5ms40000

[0046]

assign#1clk_1mhz=(counter_1ms_period==13

′

h50);//80

[0047]

always@(posedge sysclk or posedge sysrst)

[0048]

if(sysrst)counter_10ms_period<=#14

′

h0;

[0049]

else if(counter_1ms_period==79999)begin

[0050]

if(counter_10ms_period==4

′

h9)counter_10ms_period<=#14

′

h0;

[0051]

else counter_10ms_period<=#1c。unter_10ms_period+1

′

b1;

[0052]

end

[0053]

assign#1 external_10ms_intr_to_cpu2=(counter_10ms_period==4

′

h9)&(counter_1ms_period[3∶0]==13

′

h0)always@(posedge sysclk or posedge sysrst)

[0054]

if(sysrst)timer_1ms<=#132

′

h0;

[0055]

else if(counter_1ms_period==79999timer_1ms<=#1timer_1ms+1

′

b1;

[0056]

2)3路rs422串口可编辑逻辑电路21

[0057]

使用verilog hdl语言设计3路rs422串口可编辑逻辑电路21,分为接收逻辑电路和发送逻辑电路;串口波特率可配置,通过操作波特率寄存器完成波特率实时配置;串口发送逻辑电路设计发送状态机控制,以串口发送控制时钟为起始信号,将要发送的数据写入数据发送寄存器,触发状态机开始工作转换;发送数据经过并串转换,以固定波特率依次发送到串口发送端,发送完成后再重新读取发送寄存器状态,循环进行数据发送;串口接收逻辑电路设计接收状态机控制,串口接收端口收到有效数据后,触发状态机接收数据,有效数据通过防错判断、位数判断后,转换为1位有效数据,存入移位寄存器,依次完成11位串行数据接收,最终得到有效字节数据,将该数据自动存入指定的双口ram存储器24地址中,存储

地址自动进位切换,串口接收逻辑电路包含数据防错判断、空数据检测、串并转换和数据自动存储等模块;串口接收逻辑电路和发送逻辑电路都以系统时钟生成的串口时钟信号为基准,保证时钟一致性;串口工作方式是串口发送逻辑电路发送命令字到下位机,下位机接收命令字返回有效数据;串口发送逻辑电路起始信号以1ms采样时钟信号(start信号)为基准,保证数据采样1ms周期同步;3路串口逻辑使用相同时钟信号控制,且通过fpga实现可并行执行,保证3路串口同步;

[0058]

3路rs422串口可编辑逻辑电路21的程序源代码如下:

[0059]

wire[7∶0]addra_to_myuart;

[0060]

wire[7∶0]dina_from_uart;

[0061]

wire wea_from_uart;

[0062]

reg write_length_state,high_address_flag,high_address_flag_i;

[0063]

find_rx_falling use_find_rx_falling(

[0064]

.clk29_4912mhz(clk29_4912mhz),

[0065]

.sysrst(sysrst),

[0066]

.rx(rx),

[0067]

.rx_reg(rx_reg),

[0068]

.rx_falling(rx_falling));

[0069]

gen_clk16x use_gen_clk16x(

[0070]

.clk29_4912mhz(clk294912mhz),

[0071]

.sysrst(sysrst),

[0072]

.rxcnt_reset(rxcnt_reset),

[0073]

.baudrate_nco(baudrate_nco),

[0074]

.clk_16x(clk_16x));

[0075]

assign receive_start=rx_falling&long_time_idle;

[0076]

assign rxcnt_reset=rx_falling&(long_time_idlelone_byte_rdy);

[0077]

always@(posedge c1k29_4912mhz or posedge sysrst)

[0078]

if(sysrst)rxcnt<=#18

′

b0;

[0079]

else if(rxcnt_reset)rxcnt<=#18

′

b0;

[0080]

3)3路正负脉冲计数可编程逻辑电路22

[0081]

使用verilog hdl语言设计3路正负脉冲计数可编程逻辑电路22,正负脉冲计数逻辑由计数状态机控制,以1ms采样时钟信号(lock_1khz信号)触发状态机工作,保证时钟一致性和同步性;状态机触发后,接收到有效数据时开始防抖判断,防抖判断时钟与系统时钟同步,当判断数据有效后将数据存入寄存器并累加计数,计数到下一个采样时钟到达;此时寄存器中计数值与前一时钟周期计数值差值即为当前1ms周期内正负脉冲计数值;正负脉冲计数逻辑以1ms采样时钟为基准,采样数据与1ms采样时钟同步,保证系统采样同步;3路正负脉冲计数可编程逻辑电路22使用相同的时钟信号控制,且通过fpga实现可并行执行,保证3路通道同步。

[0082]

3路正负脉冲计数可编程逻辑电路22的源程序代码如下:

[0083]

wire[15:0]ccunter_acc_z;

[0084]

wire[31:0]counter_one_pps;

[0085]

anti_dither_all use_anti_dither_all(

[0086]

.sysclk(sysclk),

[0087]

.sysrst(sysrst),

[0088]

.acc_upx(acc_upx),

[0089]

.acc_downx(acc_downx),

[0090]

.acc_upy(acc_upy),

[0091]

.acc_downy(acc_downy),

[0092]

.acc_upz(acc_upz),

[0093]

.acc_downz(acc_downz),

[0094]

.one_pps(one_pps),

[0095]

.acc_upx_pf(acc_upx_f),

[0096]

.acc_downx_pf(acc_downx_pf),

[0097]

.acc_upy_pf(acc_upy_pf),

[0098]

.acc_downy_pf(acc_downy_pf),

[0099]

.acc_upz_pf(acc_upz_pf),

[0100]

.acc_downz_pf(acc_downz_pf),

[0101]

.one_pps_pf(one_pps_pf)

[0102]

);

[0103]

4)6路a/d转换可编程逻辑电路23

[0104]

使用verilog hdl语言设计6路a/d转换可编程逻辑电路23;a/d转换逻辑由ad状态机控制,由系统时钟生成的a/d时钟信号控制a/d转换状态机工作;接收到a/d转换完成信号后,状态机控制接收a/d转换串行数据,将串行数据转换为并行数据存储到双口ram存储器24固定地址中,数据结构包括a/d转换通道号、a/d转换数据和数据状态等信息,当前通道数据接收完成后自动切换到下一通道,循环采集6个a/d转换通道数据,a/d转换可编程逻辑电路23以a/d时钟信号为基准,保证a/d转换与其它逻辑同步,保证采样数据同步,6路a/d转换通道使用相同时钟信号控制,保证6路通道间同步。

[0105]

6路a/d转换可编程逻辑电路23的源程序代码如下:

[0106]

receive_fifo_12receive_fifo_12(

[0107]

.clk(sysclk),

[0108]

.rst(1

′

b0),

[0109]

.din(data_from_ad),//bus[11∶0]

[0110]

.wr_en(counter_state2==12),

[0111]

.rd_en(read_local_fifo_en),

[0112]

.dout(read_data_from_local_fifo),//bus[11:0]

[0113]

.full(),

[0114]

.empty(receive_fifo_empty));

[0115]

assign#1read_fifo_cs=bram_en_pin&(bram_addr_pin==15

′

h6054);//6054

[0116]

assign#1bram_din_pin=read_fifo_cs?{16

′

b0,idle_state,read_data_from_

local_fifo}:32

′

hzzz;assign#1read_local_fifo_en=read_fifo_cs;

[0117]

//ad_clk

[0118]

always@(posedgesysclk or posedge sysrst)

[0119]

if(sysrst)ad_clk_counter<=#19

′

b0;

[0120]

else if(ad_clk_counter==409)ad_clk_counter<=#19

′

b0;

[0121]

else ad_clk_counter<=#1ad_clk_counter+1

′

b1;

[0122]

always@(posedge sysclk or posedge sysrst)

[0123]

if(sysrst)ad_clk<=#11

′

b0;

[0124]

else if(ad_clk_counter==204)ad_clk<=#11

′

b0;

[0125]

else if(ad_clk_counter==409)ad_clk<=#11

′

b1;

[0126]

endmodule

[0127]

逻辑综合验证

[0128]

在ise工程文件中创建硬件平台,生成顶层文件system_stub;在开发平台中嵌入microblaze微处理器24、时钟控制器31和双口ram存储器24等ip核并完成配置,将设计完成的各通道逻辑转换成网表文件与顶层文件关联,配置接入时钟及外部接口信号,将双口ram存储器24端口b控制总线、数据总线和地址总线与各可编程逻辑电路模块连接,经过综合时序分析、isim仿真及在线调试,3路rs422串口可编辑逻辑电路21、3路正负脉冲计数可编程逻辑电路22和6路a/d转换可编程逻辑电路23数据采集时钟实时同步,可实现各通道并行采样。

[0129]

为验证本结构的有效性即各采样通道实时性和同步性,设计一块imu数据采集板,数据采集板包括时钟发生器逻辑电路、3路rs422串口可编辑逻辑电路2

‑

1、3路正负脉冲计数可编程逻辑电路2

‑

2和6路a/d转换可编程逻辑电路2

‑

3、fpga配置电路和接口隔离电路等;fpga中启动工作,采集各通道数据验证数据采集方法有效性,实验结果表明,本方法实现了imu各通道数据实时、同步和并行采集。

[0130]

本技术方案采用精准的时钟控制模块生成的时钟信号,确保信号逻辑采集及处理模块信号和数据处理通讯模对各路数据采集与处理的同步性和完整性;利用fpga并行采集特点,实现3路rs422接口、3路正负脉冲接口和6路a/d转换接口同步、并行、实时和高速采集,并将采集数据自动存储,适用于对imu数据采集实时性及同步性要求较高和具有扩展性要求的应用场合,尤其可应用于多通道多种类实时信号同步采集处理;采用在fpga芯片上嵌入微处理器和双口ram存储器,用于和导航计算机通过数据总线进行数据交互,并采用高精度晶振作为时钟输入源,在fpga中通过时钟控制器生成其它模块所需的时钟信号,保证时钟信号的精度和同源,从而保证时间同步性;采用fpga芯片上的中断管理器控制微处理器的数据读取,读取数据的中断时钟信号与采样时钟信号相差固定时间,保证数据采集完整性及实时性,通过1路中断实现采样数据读取,减少中断次数;采用fpga芯片上嵌入可编程逻辑电路,实现数据的采集,可编程逻辑电路执行速度快,指令周期为纳秒级,可满足高速数据采集要求,具有可扩展性和复用性,可实现3路rs422接口、3路正负脉冲接口和6路a/d转换接口并行采集,保证多通道之间同步性。

[0131]

上述实施例,只是本实用新型的较佳实施例,并非用来限制本实用新型实施范围,故凡以本实用新型权利要求所述内容所做的等效变化,均应包括在本实用新型权利要求范

围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1