一种高速连续整数分频电路的制作方法

1.本实用新型属于集成电路架构领域,尤其涉及一种高速连续整数分频电路。

背景技术:

2.高速连续整数分频电路应用非常广泛,尤其是在时钟电路,锁相环路中。它的具体应用主要体现在以下三个方面:

3.第一:在射频收发机的本振电路中,载波频率通常是由高精度锁相环实现的。高速分频电路的功能主要体现在两个方面:一是将低频的输入参考信号通过反馈机制倍频到射频信号;二是通过改变分频比可以改变本振的输出频率。此外,分频器的参数与性能影响影响着锁相环的许多重要性能。提高分频电路的工作速度可以提高本振的输出频率,连续的整数分频可以提高本振的频率精度。

4.第二:高速的数据转换器需要高速高精度的时钟芯片。随着通信电子产品的工作频率不断提高,对时钟速度与精度的要求也越来越高。同时伴随着数字信号处理技术的不断突破,利用高速高精度的模数转换器将模拟信号转换成数字信号进行处理已经得到广泛应用。时钟的精度与速度直接影响adc的性能,尤其在上gbps的高速adc应用场合,因此设计高速精度的分频电路显得尤其重要。

5.第三:在大规模高速数字系统中,通常需要一个同源的时钟网络,因此分频电路需要兼顾高速与低频两个频段。分频比的增加会在一定程度上限制电路的工作速率,因此设计一个高速连续的高频比电路显得尤为重要。

技术实现要素:

6.本实用新型的目的旨在提出一种高速的连续整数分频电路,解决现有数字方案实现连续整数分频电路工作速率低的问题,在提高电路工作速度的同时,提高分频比。

7.为解决上述技术问题,本实用新型的技术方案为:

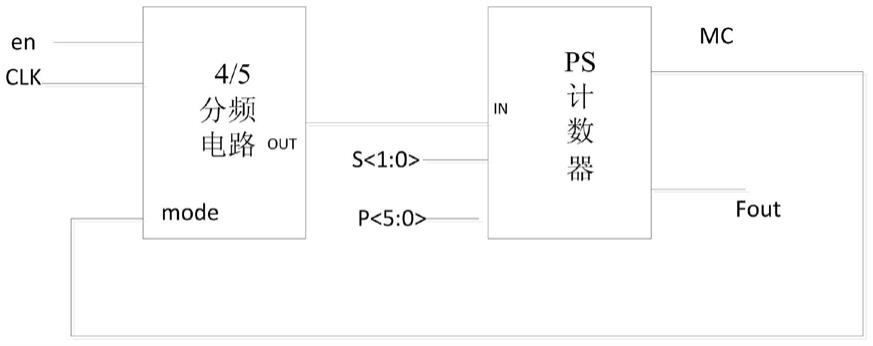

8.一种高速连续整数分频电路,包括高速4/5分频电路与ps计数器;

9.时钟信号传输进入4/5分频电路的时钟clk端口,使能信号进入 4/5分频电路的使能en端口,4/5分频电路的输出out端口连接ps 计数器的输入in端口,ps计数器的p预置数端口和s预置数端口分别连接预置数set信号,ps计数器的输出mc端口连接4/5分频电路的mode端口,ps计数器的输出fout端口输出分频信号;其中,ps 计数器包括p计数器与s计数器,p计数器与s计数器同时工作,记数值p大于s,4/5分频电路先进行5分频,记s个数后,进行4分频,当p记满时,复位s计数器,4/5分频电路再次进行5分频,如此周而复始的工作,5分频累计进行s次,4分频累计4(p

‑

s)次,完成4p+s分频。

10.其中,p计数器包括6个高速tspc触发器构成的6bit counter 模块、d触发器以及6输入或门;第1个高速tspc触发器的时钟clk 端口连接4/5分频电路的输出out端口,反向数据nq端口连接自己的数据端口d,输出同相q<0>端口连接第2个高速tspc触发器的时钟clk端口;第2个高速tspc触发器的反向数据nq端口连接自己的数据端口d,输出同相q<1>端口

连接第3个高速tspc触发器的时钟 clk端口;第3个高速tspc触发器的反向数据nq端口连接自己的数据端口d,输出同相q<2>端口连接第4个高速tspc触发器的时钟clk 端口;第4个高速tspc触发器的反向数据nq端口连接自己的数据端口d,输出同相q<3>端口连接第5个高速tspc触发器的时钟clk端口;第5个高速tspc触发器的反向数据nq端口连接自己的数据端口 d,输出同相q<4>端口连接第6个高速tspc触发器的时钟clk端口;第6个高速tspc触发器的反向数据nq端口连接自己的数据端口d; 6个高速tspc触发器的异步置数端口连接在一起构成6bit counter 模块的异步置数端口load,6个高速tspc触发器的预置数set端口构成6bit数据端口p<5:0>,第1个高速tspc触发器预置数set信号代表最低位p<0>,第6个高速tspc触发器预置数set信号代表 p<5>,6bit counter模块的6位输出同相q<5:0>数据端口分别连接 6输入的或门,或门的输出连接d触发器的数据端口d,d触发器的时钟端口连接4/5分频电路的输出out端口,d触发器的同相位数据 q输出端口连接6bit counter模块的异步置数端口load,并作为输出fout端。

11.其中,s计数器包括2个高速tspc触发器构成的2bit counter 模块、d触发器、2输入或门以及带反相结构的与门;第1个高速tspc 触发器的时钟clk端口连接4/5分频电路的输出out端口,反向数据 nq端口连接自己的数据端口d,输出同相q<0>端口连接第2个高速tspc触发器的时钟clk端口;第2个高速tspc触发器的反向数据nq 端口连接自己的数据端口d,输出同相端构成q<1>;2个高速tspc 触发器的异步置数端口连接在一起构成2bit counter模块的异步置数端口load,连接p计数器的同相位数据q输出端口,2个高速tspc 触发器的set端口构成s<1:0>,第1个高速tspc触发器set信号代表最低位s<0>,第2个代表s<1>,两个高速tspc触发器的输出同相 q<0>与q<1>分别连接一个或门,或门的输出端连接与门的正向输入端口,与门的反相输入端口连接p计数器的异步置数端口load,与门的输出端连接d触发器的同相数据输入端口以及2个高速tspc触发器级联构成的停止计数sp端口,d触发器的时钟端口连接4/5分频电路的输出out端口,d触发器同相位数据q输出端口输出mc信号。

12.其中,p计数器的高速tspc触发器包括数据端口d、异步置数端口load、时钟端口clk、同相位数据q输出端口、反向数据端口nq 和预置数端口set;晶体管m1的栅极连接load信号,源极连接电源电压vdd,漏极连接晶体管m2的源极;晶体管m2的栅极连接晶体管 m4的栅极与数据端口d端,漏极连接晶体管m3的漏极;晶体管m3 的栅极连接时钟clk信号,源极连接晶体管m4与晶体管m5的漏极;晶体管m4与晶体管m5的源极连接gnd;晶体管m6的源极连接vdd,漏极连接晶体管m7的漏极,栅极连接load信号;晶体管m7的栅极连接m2的漏极,源极连接晶体管m8的漏极;晶体管m8栅极连接clk 信号,源极连接gnd;晶体管m9的源极连接vdd,漏极连接晶体管m10的源极,栅极连接load信号;晶体管m10的栅极连接clk,漏极连接晶体管m11的漏极与同相位数据q输出端口;晶体管m11的栅极连接晶体管m8的漏极,源极连接晶体管m12漏极;晶体管m12的栅极连接nload信号,源极连接gnd;晶体管m13的源极连接vdd,栅极连接晶体管m16的栅极与预置数set信号,漏极连接晶体管m14的源极;晶体管m14的栅极连接nload信号,漏极连接晶体管m15与晶体管m11的漏极与同相位数据q输出端口;晶体管m15的栅极连接 load信号与m19的栅极,源极连接晶体管m16的漏极;晶体管m16 的源极连接gnd;晶体管m17的栅极连接nload信号,源极连接vdd,漏极连接晶体管m18的源极;晶体管m18的栅极连接晶体管m20的栅极与同相位数据q输出端口,漏极连接晶体管m19的漏

极与晶体管 m7的源极;晶体管m19的栅极连接晶体管m15的栅极,源极连接晶体管m20的漏极;晶体管m20的源极连接gnd。

13.其中,s计数器的高速tspc触发器包括数据端口d、异步置数端口load、时钟端口clk、同相位数据q输出端口、反向数据端口nq、停止计数sp端口和预置数端口set;晶体管m1的栅极连接load信号,源极连接电源电压vdd,漏极连接晶体管m21的源极;晶体管m21 的漏极连接晶体管m2的源极,晶体管m21的栅极连接停止计数sp信号;晶体管m2的栅极连接晶体管m4的栅极与数据端口d端,漏极连接晶体管m3的漏极;晶体管m3的栅极连接时钟clk信号,源极连接晶体管m4与晶体管m5的漏极;晶体管m4与晶体管m5的源极连接 gnd;晶体管m6的源极连接vdd,漏极连接晶体管m7的漏极,栅极连接load信号;晶体管m7的栅极连接m2的漏极,源极连接晶体管 m8的漏极;晶体管m8栅极连接clk信号,源极连接gnd;晶体管m9 的源极连接vdd,漏极连接晶体管m10的源极,栅极连接load信号;晶体管m10的栅极连接clk,漏极连接晶体管m11的漏极与同相位数据q输出端口;晶体管m11的栅极连接晶体管m8的漏极,源极连接晶体管m12漏极;晶体管m12的栅极连接nload信号,源极连接gnd;晶体管m13的源极连接vdd,栅极连接晶体管m16的栅极与预置数set 信号,漏极连接晶体管m14的源极;晶体管m14的栅极连接nload信号,漏极连接晶体管m15与晶体管m11的漏极与同相位数据q输出端口;晶体管m15的栅极连接load信号与m19的栅极,源极连接晶体管m16的漏极;晶体管m16的源极连接gnd;晶体管m17的栅极连接 nload信号,源极连接vdd,漏极连接晶体管m18的源极;晶体管m18 的栅极连接晶体管m20的栅极与同相位数据q输出端口,漏极连接晶体管m19的漏极与晶体管m7的源极;晶体管m19的栅极连接晶体管 m15的栅极,源极连接晶体管m20的漏极;晶体管m20的源极连接gnd。

14.与现有技术相比,本实用新型的优点及显著效果为:

15.1)本实用新型不需要外部触发置数信号,简化了系统的设计逻辑。

16.2)本实用新型改进的触发器结构具有置数与停止功能,满足高速ps计数器设计的基本要求

17.3)本实用新型异步计数器逻辑结构的应用,解除同步逻辑对时钟速率的要求,异步逻辑结构在位数增加时,会出现中间状态错误,但是此应用只需要确保最后一个周期信号的准确性,经过仿真确认此架构在最后三个周期将错误计数状态纠正,因此异步架构更适用于高速的场合。

18.4)本实用新型缓解了时钟的时序紧张,提高了电路的工作速率。

附图说明

19.图1是本实用新型的整体电路结构图;

20.图2是本实用新型带自置数逻辑产生电路的6位p计数器电路结构图;

21.图3是本实用新型的时序提前检测s计数器电路结构图;

22.图4是本实用新型带置数功能的高速tspc触发器电路结构图。

23.图5是本实用新型带置数、停止记数功能的高速tspc触发器电路结构图。

具体实施方式

24.下面结合附图和具体实施方式对本实用新型做进一步详细的说明。

25.如图1所示,本实用新型由高速4/5分频与ps计数器实现。

26.时钟信号传输进入4/5分频电路的时钟clk端口,使能信号进入4/5分频电路的使能en端口,4/5分频电路的输出out端口连接ps 计数器的输入in端口,ps计数器的p预置数端口和s预置数端口分别连接预置数set信号,ps计数器的输出mc端口连接4/5分频电路的mode端口,ps计数器的输出fout端口输出分频信号;其中,ps 计数器包括p计数器与s计数器,p计数器与s计数器同时工作,记数值p大于s,4/5分频电路先进行5分频,记s个数后,进行4分频,当p记满时,复位s计数器,4/5分频电路再次进行5分频,如此周而复始的工作,5分频累计进行s次,4分频累计4(p

‑

s)次,完成4p+s分频。

27.带自建置数信号的p计数器如图2所示。上电后,计数器从111111 开始进行减法置数,直到计数器输出000010,逻辑门产生信号“1”,下个时钟周期,load信号为“1”,计数器开始把预置数加载到输出端,p计数器从预置数开始减法记数,直到000010状态出现,重新置数。因为d触发器的插入可以将置数保留一个周期,因此p计数器累计p

‑

2+1+1=p个周期。

28.p计数器包括6个高速tspc触发器构成的6bit counter模块、 d触发器以及6输入或门;第1个高速tspc触发器的时钟clk端口连接4/5分频电路的输出out端口,反向数据nq端口连接自己的数据端口d,输出同相q<0>端口连接第2个高速tspc触发器的时钟clk 端口;第2个高速tspc触发器的反向数据nq端口连接自己的数据端口d,输出同相q<1>端口连接第3个高速tspc触发器的时钟clk端口;第3个高速tspc触发器的反向数据nq端口连接自己的数据端口 d,输出同相q<2>端口连接第4个高速tspc触发器的时钟clk端口;第4个高速tspc触发器的反向数据nq端口连接自己的数据端口d,输出同相q<3>端口连接第5个高速tspc触发器的时钟clk端口;第 5个高速tspc触发器的反向数据nq端口连接自己的数据端口d,输出同相q<4>端口连接第6个高速tspc触发器的时钟clk端口;第6 个高速tspc触发器的反向数据nq端口连接自己的数据端口d;6个高速tspc触发器的异步置数端口连接在一起构成6bit counter模块的异步置数端口load,6个高速tspc触发器的预置数set端口构成6bit数据端口p<5:0>,第1个高速tspc触发器预置数set信号代表最低位p<0>,第6个高速tspc触发器预置数set信号代表p<5>, 6bit counter模块的6位输出同相q<5:0>数据端口分别连接6输入的或门,或门的输出连接d触发器的数据端口d,d触发器的时钟端口连接4/5分频电路的输出out端口,d触发器的同相位数据q输出端口连接6bit counter模块的异步置数端口load,并作为输出fout 端。

29.带检测电路的s计数器如图3所示,此逻辑同时兼容s=0记数功能。当s计数器预置数为0时,sp=“1”,s计数器停止记数,mc=0,分频器实现分频比为4p;当s预置数不等于0时,s计数器从预置数减法记数到00。s计数器累计s个数。

30.s计数器包括2个高速tspc触发器构成的2bit counter模块、 d触发器、2输入或门以及带反相结构的与门;第1个高速tspc触发器的时钟clk端口连接4/5分频电路的输出out端口,反向数据nq 端口连接自己的数据端口d,输出同相q<0>端口连接第2个高速tspc 触发器的时钟clk端口;第2个高速tspc触发器的反向数据nq端口连接自己的数据端口d,输出同相端构成q<1>;2个高速tspc触发器的异步置数端口连接在一起构成2bit counter模块的异步置数端口load,连接p计数器的同相位数据q输出端口,2个高速tspc触发器的set端口构成s<1:0>,第1个高速tspc触发器set信号代表最低位s<0>,第2个代表s<1>,两个高速tspc触发器的输出同相 q<0>与q<1>分别连接一个或门,或门的输出端连接与门的正向输

入端口,与门的反相输入端口连接p计数器的异步置数端口load,与门的输出端连接d触发器的同相数据输入端口以及2个高速tspc触发器级联构成的停止计数sp端口,d触发器的时钟端口连接4/5分频电路的输出out端口,d触发器同相位数据q输出端口输出mc信号。

31.如图4所示,本实用新型提出了带异步置数功能的高速tspc触发器结构,当load=1,实现异步置数。当load=0时,clk低电平输出跟随输入信号d变化,clk高电平,输出保持,因此此结构为上升沿d触发器。用此结构组成异步逻辑的p计数器与s计数器。

32.p计数器的高速tspc触发器包括数据端口d、异步置数端口load、时钟端口clk、同相位数据q输出端口、反向数据端口nq和预置数端口set;晶体管m1的栅极连接load信号,源极连接电源电压vdd,漏极连接晶体管m2的源极;晶体管m2的栅极连接晶体管m4的栅极与数据端口d端,漏极连接晶体管m3的漏极;晶体管m3的栅极连接时钟clk信号,源极连接晶体管m4与晶体管m5的漏极;晶体管m4 与晶体管m5的源极连接gnd;晶体管m6的源极连接vdd,漏极连接晶体管m7的漏极,栅极连接load信号;晶体管m7的栅极连接m2的漏极,源极连接晶体管m8的漏极;晶体管m8栅极连接clk信号,源极连接gnd;晶体管m9的源极连接vdd,漏极连接晶体管m10的源极,栅极连接load信号;晶体管m10的栅极连接clk,漏极连接晶体管m11的漏极与同相位数据q输出端口;晶体管m11的栅极连接晶体管 m8的漏极,源极连接晶体管m12漏极;晶体管m12的栅极连接nload 信号,源极连接gnd;晶体管m13的源极连接vdd,栅极连接晶体管 m16的栅极与预置数set信号,漏极连接晶体管m14的源极;晶体管 m14的栅极连接nload信号,漏极连接晶体管m15与晶体管m11的漏极与同相位数据q输出端口;晶体管m15的栅极连接load信号与m19 的栅极,源极连接晶体管m16的漏极;晶体管m16的源极连接gnd;晶体管m17的栅极连接nload信号,源极连接vdd,漏极连接晶体管 m18的源极;晶体管m18的栅极连接晶体管m20的栅极与同相位数据 q输出端口,漏极连接晶体管m19的漏极与晶体管m7的源极;晶体管m19的栅极连接晶体管m15的栅极,源极连接晶体管m20的漏极;晶体管m20的源极连接gnd。同相位数据q输出端口经过一个反相器形成反向数据端口nq。

33.如图5所示,本实用新型提出了带异步置数、停止记数功能的高速tspc触发器结构,当load=1,实现异步置数。当sp=1时,停止记数当load=0且sp=0时,clk低电平输出跟随输入信号d变化,clk 高电平,输出保持,因此此结构为上升沿d触发器。用此结构组成异步s计数器。

34.s计数器的高速tspc触发器包括数据端口d、异步置数端口load、时钟端口clk、同相位数据q输出端口、反向数据端口nq和预置数端口set;晶体管m1的栅极连接load信号,源极连接电源电压vdd,漏极连接晶体管m21的源极;m21的漏极连接m2的源极,m21的栅极连接sp信号,晶体管m2的栅极连接晶体管m4的栅极与数据端口d 端,漏极连接晶体管m3的漏极;晶体管m3的栅极连接时钟clk信号,源极连接晶体管m4与晶体管m5的漏极;晶体管m4与晶体管m5的源极连接gnd;晶体管m6的源极连接vdd,漏极连接晶体管m7的漏极,栅极连接load信号;晶体管m7的栅极连接m2的漏极,源极连接晶体管m8的漏极;晶体管m8栅极连接clk信号,源极连接gnd;晶体管m9的源极连接vdd,漏极连接晶体管m10的源极,栅极连接load 信号;晶体管m10的栅极连接clk,漏极连接晶体管m11的漏极与q 端;晶体管m11的栅极连接晶体管m8的漏极,源极连接晶体管m12 漏极;晶体管m12的栅极连接nload信号,源极连接gnd;晶体管m13 的源极连接vdd,栅极连接晶体管m16的栅极与预置数set信号,漏极连接晶体管m14的源极;晶体管m14的栅极连接nload信号,漏极连接晶体管m15与晶体管m11的漏极与q

信号;晶体管m15的栅极连接load信号与m19的栅极,源极连接晶体管m16的漏极;晶体管m16 的源极连接gnd;晶体管m17的栅极连接nload信号,源极连接vdd,漏极连接晶体管m18的源极;晶体管m18的栅极连接晶体管m20的栅极与q信号,漏极连接晶体管m19的漏极与晶体管m7的源极;晶体管m19的栅极连接晶体管m15的栅极,源极连接晶体管m20的漏极;晶体管m20的源极连接gnd。

35.本实用新型工作原理为:芯片上电后,自动产生置数信号,p与 s计数器自动置数为p与s。mc=0时,4/5分频工作在5分频状态,p 与s计数器同时开始计数,计数器采用异步逻辑结构,消除了同步逻辑对时钟频率的依赖性,计数器位数增加会限制异步结构的工作速率,但是此计数器只需要最后一个周期,计数器输出了一个准确的脉冲信号,不用确保每个周期计数状态值得正确性,利用上述特点,异步架构的计数器提高了分频电路的工作速率。当s计满s个数后停止,输出mc=1,4/5分频进行4分频,直到p计数器记满p个数,复位s 计数器,s计数器继续工作,可编程分频器实现分频比为5s+4(p

‑

s) =4p+s。如此状态实现可编程分频器的一个周期,重复上述过程。

36.本实用新型改进了传统的tspc触发器结构,使它具有异步置数功能。用设计的触发器分别设计了6位的p计数器和2位的s计数器。自动检测逻辑可以判别p计数器的记数值,同时可以自动产生复位信号,过2检测电路可以检测s计数器的记数值,同时加速电路的工作速率。用cml结构实现高速的4/5分频电路。最终实现4p+s分频比 (其中p为p计数器的记数值,s位s计数器的记数值)。

37.利用本实用新型所提方案设计的分频器可以实现:s=0时的特殊分频,并且当输入信号为4ghz,该分频器进行20分频,输出频率为 200mhz。分频器在输入4ghz时,进行21分频,输出频率为190.476mhz。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1