混合多尔蒂功率放大器模块和包括该模块的基站的制作方法

1.本发明涉及一种混合多尔蒂(doherty)功率放大器模块。本发明还涉及一种包括这种模块的用于移动通信的基站。本发明特别涉及一种用于5g蜂窝网络的混合多尔蒂功率放大器模块和相应的基站,例如,大规模多输入多输出(m-mimo)基站。

背景技术:

2.过去,用于移动通信的基站例如,4g基站中使用的功率放大器基于横向扩散金属氧化物半导体(ldmos)晶体管,其被配置为以高达2ghz的频率输出高功率。功率放大器通常基于多尔蒂概念。在这个概念中,要放大的信号首先被多尔蒂分离器分离成各种信号部分。然后,这些部分被馈送到主放大器和一个或多个峰值放大器。放大后,各种信号部分使用多尔蒂组合器进行组合。在多尔蒂概念中,主放大器和峰值放大器以不同的输入功率水平开始工作。更具体地,主放大器通常被偏置为ab类或b类,一个或多个峰值放大器被偏置为c类。此外,如果使用多个峰值放大器,则不同的偏置设置可以用于峰值放大器中的每个,使得它们在不同的输入功率水平下工作。此外,多尔蒂组合器使用一个或多个阻抗反相器。这些反相器确保在低输入功率下,当峰值放大器中的一个或多个关闭时,主放大器的输出处呈现比高输入功率下更高的阻抗。这样,主放大器看到的负载被一个或多个峰值放大器调制。这允许在功率回退中工作时获得高效率。

3.通常,ldmos晶体管是封装器件。然后,使用其上安装有ldmos晶体管封装的印刷电路板来实现多尔蒂放大器。使用传输线和/或分立元件(例如,表面安装器件smd)在印刷电路板上实现多尔蒂组合器和分离器。在下文称为分立解决方案的这些实施例中,印刷电路板形成其他电路(例如,基站的其他电路)的一部分。

4.在其他实施例中,多尔蒂放大器以模块形式实现。在这些实施例中,ldmos晶体管管芯安装在印刷电路板上。多尔蒂组合器和分离器也实现在该印刷电路板上。印刷电路板、ldmos晶体管管芯和印刷电路板上的电路的组合被封装为模块。这种模块(以下称为模块解决方案)随后被设置在印刷电路板上,作为单个放大单元。

5.在模块和分立解决方案中,多尔蒂组合器和分离器的至少一部分可以在与ldmos晶体管本身相同的半导体管芯上实现。

6.诸如5g的通信领域的最新趋势对更高工作频率下的输出功率和效率提出了更严格的要求。诸如氮化镓的宽带隙材料已经成为满足这些需求的合适候选材料。然而,与ldmos技术相比,氮化镓高电子迁移率晶体管hemt技术不太可能以成本有效的方式将多尔蒂组合器和分离器的至少一部分集成在与功率晶体管相同的半导体管芯上。

技术实现要素:

7.本发明的一个目的是提供一种多尔蒂功率放大器模块,其提供了这个问题的解决方案。

8.根据本发明,使用根据权利要求1中定义的混合多尔蒂功率放大器模块来获得这

种解决方案。该模块包括印刷电路板,该印刷电路板具有输入rf端子和输出rf端子,并且在该印刷电路板上集成了初级多尔蒂放大器。初级多尔蒂放大器包括初级多尔蒂分离器、初级多尔蒂组合器和多个放大路径。

9.初级多尔蒂分离器被设置在印刷电路板上,并且被配置用于将在输入rf端子处接收的输入rf信号分离成多个rf信号分量。

10.每个放大路径部分集成在安装在印刷电路板上的第一种半导体管芯上,部分集成在安装在印刷电路板上的第二种半导体管芯上。每个放大路径包括设置在第二种半导体管芯上的相应放大路径输出端子和设置在第一种半导体管芯上的相应放大路径输入端子,其中,每个放大路径被配置为放大在其放大路径输入端子处从初级多尔蒂分离器接收的相应rf信号分量,并通过其放大路径输出端子输出放大的rf信号分量。多个放大路径中的一个放大路径形成初级多尔蒂放大器的主放大器,并且剩余的放大路径形成初级多尔蒂放大器的相应峰值放大器。

11.初级多尔蒂组合器设置在印刷电路板上,并且被配置用于组合从多个放大路径接收的多个放大的rf信号分量,并且通过输出rf端子输出组合的放大的rf信号分量。

12.每个放大路径包括集成在第一种半导体管芯上的次级多尔蒂放大器和集成在第二种半导体管芯上的末级放大器。此外,次级多尔蒂放大器基于硅ldmos技术,末级放大器基于gan hemt技术。

13.本发明提出了一种嵌套的多尔蒂放大器。更具体地,每个放大路径包括完全在驱动gan末级的硅ldmos管芯上实现的次级多尔蒂放大器。以这种方式,硅ldmos技术的优点和gan的优点最佳地组合。此外,多个放大路径组合,以形成初级多尔蒂放大器。使用这种拓扑结构,可以最小化不同组件的数量,特别是当每个放大路径基本相同时。

14.多个放大路径的次级多尔蒂放大器可以集成在相应的多个第一种半导体管芯上。在其他实施例中,相邻放大路径的次级多尔蒂放大器可以在单个第一种半导体管芯上组合。类似地,多个放大路径的末级放大器可以集成在相应的多个第二种半导体管芯上。同样在此处,多个末级放大器可以在单个第二种半导体管芯上组合。

15.每个次级多尔蒂放大器可以包括次级主放大器、次级峰值放大器、次级多尔蒂分离器和次级多尔蒂组合器。次级多尔蒂分离器可以被配置用于将在放大路径输入端子接收的rf信号分量分离成主部分和峰值部分,并将这些部分分别提供给次级主放大器和次级峰值放大器。次级多尔蒂组合器可以被配置用于在组合节点处组合放大的主部分和放大的峰值部分。

16.对于每个放大路径,第一种半导体管芯可以包括主管芯输出端子,该主管芯输出端子通过级间匹配网络连接到该放大路径的末级放大器的输入端子。第一种半导体管芯还可以包括设置在相应组合节点和主管芯输出端子之间的dc阻塞电容器。此外,第一种半导体管芯可以包括设置在组合节点和地之间的第一并联网络和设置在主管芯输出端子和地之间的第二并联网络。第一并联网络可以包括第一dc偏置输入,用于接收用于偏置次级多尔蒂放大器的dc信号。第二并联网络可以包括第二dc偏置输入,用于接收用于偏置末级放大器的dc信号。

17.第一并联网络可以包括第一电感器和第一电容器的串联连接,其中,第一dc偏置输入由将第一电感器连接到第一电容器的节点形成或者电连接到将第一电感器连接到第

一电容器的节点。另外或替代地,第二并联网络可以包括第二电感器和第二电容器的串联连接,其中,第二dc偏置输入由将第二电感器连接到第二电容器的节点形成或电连接到将第二电感器连接到第二电容器的节点。

18.此外,第一并联网络可以被配置为以在等于混合多尔蒂功率放大器模块的工作频率除以a和b中的一个的频率谐振,并且其中,第二并联网络被配置为以等于混合多尔蒂功率放大器模块的工作频率除以a和b中的另一个的频率谐振,其中,1.9《a《1.3,并且其中,0.5《b《0.8。使用第一并联网络和第二并联网络,可以为次级多尔蒂放大器和相应的末级之间的信号传输获得带通特性。通常,混合多尔蒂功率放大器模块被配置为放大具有位于给定频带内的载波频率的信号。然后,上述工作频率对应于这种频带的中心频率。

19.代替使用单个第二并联网络,每个第一种半导体管芯可以包括一对所述第二并联网络,每个第二并联网络连接在主管芯输出端子和地之间。类似地,可以使用一对第一并联网络。

20.级间匹配网络可以包括与第二低通匹配网络串联的第一低通匹配网络。每个低通匹配网络可以包括并联电容器和串联电感器,并且可以具有输入节点和输出节点。第一低通匹配网络的输入节点可以连接到主管芯输出端子,并且第一低通匹配网络的输出节点可以连接到第二低通匹配网络的输入节点。第二低通匹配网络的输出节点可以连接到末级的输入端子。

21.在一个实施例中,第一低通匹配网络的串联电感器由一条或多条接合线至少部分地形成。另外或替代地,第二低通匹配网络的串联电感器可以由一个或多个接合线至少部分地形成。

22.第一低通匹配网络的并联电容器可以集成在第一种半导体管芯上。

23.第二低通匹配网络的并联电容器可以集成在安装在印刷电路板上的第三种半导体管芯上。形成第一电感器的上述一个或多个接合线然后可以在第一种半导体管芯和第三种半导体管芯之间延伸。形成第二电感器的上述一个或多个接合线然后可以在第三种半导体管芯和第二种半导体管芯之间延伸。或者,第二低通匹配网络的并联电容器可以包括设置在印刷电路板上的表面安装器件。

24.第一低通网络和第二低通网络可以被设计成使得在工作频率下或接近工作频率下,从第一低通网络的输入节点到输出节点的第一低通网络的复阻抗变换比的绝对值是从第二低通网络的输入节点到输出节点的第二低通网络的阻抗变换比的至少4倍,优选10倍。此外,第一低通网络和第二低通网络可以被设计成使得在对应于工作频率的二次谐波频率处,在第二低通网络的并联电容器和串联电感器与第一低通网络的串联电感器连接的节点处朝向次级多尔蒂放大器看到的阻抗的绝对值是第二低通网络的并联电容器的阻抗的绝对值的至少3倍,并且更优选地至少10倍。此外,由第二低通网络的并联电容器和串联电感器确定的串联谐振频率可以在工作频率的1.6倍和2.4倍之间的范围内。

25.每个次级多尔蒂组合器可以包括由集成电感器(例如,螺旋电感器)或设置在次级主放大器的输出端子和次级峰值放大器的输出端子之间的一条或多条接合线形成的串联电感器。次级多尔蒂组合器还可以包括设置在次级主放大器的输出和地之间的第一并联电容器以及设置在次级峰值放大器的输出和地之间的第二并联电容器。第一并联电容器和第二并联电容器可以分别由次级主放大器和次级峰值放大器的寄生输出电容至少部分地形

成,其中,串联电感器和第一并联电容器和第二并联电容器共同形成以基频或接近基频操作的四分之一波长阻抗反相器的集总等效电路。以这种方式,可以在集总等效电路中吸收另外会降低性能的ldmos晶体管的寄生输出电容。

26.多个放大路径可以是相同的。类似地,多个放大路径的多个第一种半导体管芯可以是相同的,和/或多个放大路径的多个第二种半导体管芯可以是相同的。

27.根据第二方面,本发明提供了一种用于移动通信(例如,5g)的基站,包括根据前述权利要求中任一项所述的混合多尔蒂功率放大器模块。

附图说明

28.接下来,将参照附图描述本发明,在附图中:

29.图1示意性地示出了根据本发明的混合多尔蒂功率放大器模块的一般拓扑;

30.图2示意性地示出了在图1的拓扑中使用的放大路径的实施例;

31.图3示意性地示出了在图1的拓扑中使用的放大路径的另一实施例;以及

32.图4和图5示意性地示出了在图3和图4的放大路径中使用的级间匹配网络的示例性rf性能。

具体实施方式

33.图1示出了根据本发明的混合多尔蒂功率放大器模块的实施例。模块1包括印刷电路板pcb 100,其通常为多层层压板的形式。pcb 100包括输入rf端子101和输出rf端子102。

34.在pcb 100上,设置了初级多尔蒂分离器110和初级多尔蒂组合器120。初级多尔蒂分离器110被配置用于将在输入rf端子101处接收的rf信号分离成在端子112a、112b处输出的多个rf信号分量。在图1中,这些分量中的一个通过移相器111相对于另一分量延迟90

°

。

35.初级多尔蒂分离器110可以以各种方式来实现,例如,使用安装在pcb 100上的、可选地与形成在pcb 100上的传输线相结合的分立元件,例如,表面安装器件smd来实现。在其他实施例中,初级多尔蒂分离器110仅使用形成在pcb 100上的传输线来形成。

36.模块1还包括两个放大路径200a、200b。每个放大路径200a、200b部分集成在安装在pcb 100上的硅管芯210a、210b上,并且部分集成在安装在pcb 100上的氮化镓管芯230a、230b上。此外,放大路径200a、200b各自包括级间匹配网络220a、220b,将结合图2和图3讨论级间匹配网络220a、220b的两个示例。

37.每个放大路径200a、200b包括放大路径输入端子201a、201b和放大输出端子202a、202b。放大路径输入端子201a、201b通常形成在硅管芯210a、210b上,而放大路径输出端子202a、202b形成在氮化镓管芯230a、230b上。

38.每个硅管芯210a、210b包括次级主放大器211a、211b和次级峰值放大器212a、212b,每个放大器都被配置为si ldmos晶体管。每个硅管芯210a、210b还包括次级多尔蒂分离器,其在图1中体现为移相器213a、213b。此外,每个硅管芯210a、210b还包括次级多尔蒂组合器,其在图1中被体现为阻抗反相器214a、214b,所述阻抗反相器214a、214b设置在次级主放大器211a、211b的输出和次级峰值放大器212a、212b的输出之间。阻抗反相器214a、214b被配置为在组合节点215a、215b处组合由次级主放大器211a、211b和次级峰值放大器212a、212b放大的信号。将结合图2和图3更详细地讨论阻抗反相器214a、214b。

39.每个放大路径200a、200b还包括设置在氮化镓管芯230a、230b上的基于氮化镓的高电子迁移率晶体管hemt 232a、232b。在图1中,级间网络220a、220b将组合节点215a、215b连接到氮化镓管芯230a、230b上的输入端子231a、231b。

40.初级多尔蒂组合器120在rf输出端子102处组合在其输入121a、121b处从放大路径200a、200b的输出202a、202b接收的信号。更具体地,初级多尔蒂组合器120包括阻抗反相器122,该阻抗反相器122连接在放大路径200a的输出202a和rf输出端子102之间。由阻抗反相器122引入的通常等于90

°

的相位延迟等于由移相器111引入的相位延迟,使得由放大路径200a、200b放大的信号在rf输出端子102处同相相加。此外,阻抗反相器122根据基于gan的hemt 232b是接通还是断开来提供基于gan的hemt 232a所看到的负载的负载调制。

41.次级主放大器211a、211b通常在ab类或b类中偏置。次级峰值放大器212a、212b通常在c类中偏置。结果,在低输入功率下,次级峰值放大器212a、212b将处于关闭状态,并显示高输出阻抗。由于阻抗反相器214a、214b,在关闭状态期间的这种高输出阻抗将导致次级主放大器211a、211b在其输出处看到较高的输出阻抗。在高输入功率下,次级峰值放大器212a、212b将处于接通状态,并显示低输出阻抗。由于阻抗反相器214a、214b,该低输出阻抗将导致次级主放大器211a、211b在其输出处看到较低的输出阻抗。通过在功率回退下呈现更高的负载阻抗,可以提高放大路径200a、200b的效率。

42.放大路径200a、200b相对于彼此实现了类似的功能。更具体地,在图1中,放大路径200a作为初级主放大器工作,而放大路径200b作为初级峰值放大器工作。在低输入功率条件下,放大路径200b将处于关闭状态,而放大路径200a处于接通状态。在高输入功率条件下,两个放大路径200a、200b都将处于接通状态。由于阻抗反相器122,将调制基于gan的hemt 232a看到的负载,以允许在功率回退的情况下提高效率。放大路径200a、200b是作为初级主放大器还是初级峰值放大器取决于偏置设置,例如,基于gan的hemt 232a、232b的偏置设置,尽管通过另外或替代地偏置次级主放大器211a、211b和次级峰值放大器212a、212b同样可以获得类似的功能。

43.在特定实施例中,放大路径200a、200b是相同的。在此处,注意,每个放大路径200a、200b的偏置设置通常通过从模块外部馈送适当的信号来设置。换句话说,使用相同的放大路径200a、200b,但是不同地偏置这些路径,可以实现期望的嵌套多尔蒂功能。使用相同的放大路径200a、200b极大地简化了物流和成本。此外,模块1可以容易地扩展到n路多尔蒂配置,其中,n》2。在这种模块中,放大路径将相邻排列,类似于图1所示。初级多尔蒂分离器110和初级多尔蒂组合器120将不同地配置,以便分离和组合各种信号。另外或替代地,代替在硅管芯210a、210b上使用双路多尔蒂放大器,可以使用具有两个或更多个次级峰值放大器的多路多尔蒂放大器。此外,本发明不限于初级多尔蒂放大器和次级多尔蒂放大器的拓扑结构。例如,初级多尔蒂放大器和次级多尔蒂放大器中的每一个或两个都可以实现为反向多尔蒂放大器。

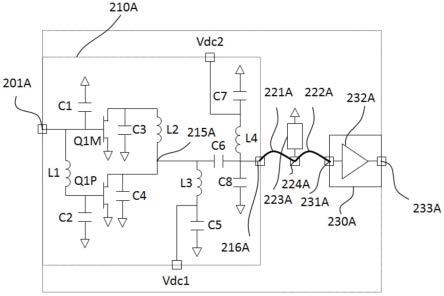

44.图2和图3示出了根据本发明的放大路径200a的实施例。在这些实施例的每一个中,硅管芯210a包括主ldmos晶体管q1m和峰值ldmos晶体管q1p。这些晶体管中的每一个都包括输出电容。在图2和图3中,在阻抗反相器中吸收这些输出电容,这将在下面讨论。

45.通常,使用四分之一波长传输线来实现阻抗反相器。这种线将传输线的输出处的高阻抗转换成传输线的输入处的低阻抗。使用四分之一波长传输线的缺点与所需的尺寸有

关。代替使用四分之一波长传输线,可以使用c-l-c等效电路。更具体地,在这种等效电路中,工作频率下的行为由第一并联电容器、串联电感器和第二并联电容器近似。然而,由于q1m和q1p已经具有固有输出电容,因此可以将这些输出电容用作第一并联电容器和第二并联电容器的一部分。在一些实施例中,第一并联电容器和第二并联电容器仅由这些输出电容形成。

46.在图2和图3中,电容器c3和c4被实现为金属-绝缘体-金属电容器、金属-氧化物-半导体电容器等,它们与q1m和q1p的输出电容一起提供c-l-c等效电路所需的电容。串联电感器l2可以使用集成电感器(例如,螺旋电感器)来形成,或者可以使用一个或多个接合线来形成。

47.在输入侧可以遵循类似的方法。在此处,所需的移相器也可以使用四分之一波长传输线来形成,该四分之一波长传输线同样可以用c-l-c网络来近似。在图2和图3中,与q1m和q1p的输入电容组合的电容器c1和c2以及串联电感器l1共同形成用于实现该c-l-c等效电路所需的并联电容。类似于l2,电感器l1可以使用集成电感器(例如,螺旋电感器)来形成,或者可以使用一个或多个接合线来形成。

48.在图2和图3中,硅管芯210a还包括并联网络,该并联网络包括电感器l3和电容器c5的串联连接。电感器l3和电容器c5相互连接的节点连接到端子vdc1。可以向该端子提供dc偏置,用于偏置q1m和q1p。

49.此外,在图2和图3中,硅管芯210a还包括并联网络,该并联网络包括电感器l4和电容器c7的串联连接。电感器l4和电容器c7相互连接的节点连接到端子vdc2。可以向该端子提供dc偏置,用于偏置基于gan的hemt 232a。dc阻塞电容器c6用于分隔上述偏置网络。在此处,dc阻塞电容器c6连接在组合节点215a和输出端子216a之间。

50.在图2和图3中,级间匹配网络包括两个低通匹配网络,每个低通匹配网络包括并联电容器和串联电感器。在图2和图3中,第一低通匹配网络的并联电容器c8被设置在硅管芯210a上,并且使用在输出端子216a和设置在pcb 100上的中间端子224a之间延伸的一个或多个接合线221a来形成相应的串联电感器。在图2中,使用设置在中间端子224a和地之间的smd电容器来形成第二低通匹配网络的并联电容器223a。在图3中,第二低通匹配网络的并联电容器223a集成在分立的半导体管芯225a上。中间端子224也设置在该管芯225a上。

51.在图2和图3中,使用中间端子224a和在基于gan的hemt 232a的输入端子231a之间延伸的一条或多条接合线222a形成第二低通匹配网络的串联电感器,基于gan的hemt 232a的端子设置在gan管芯230a上。

52.对于图2和图3中的两个实施例,因为至少两个组件可以相对快速地改变,即通过改变接合线的形状和高度来相对快速地改变,因此微调级间匹配网络是非常方便的。

53.在特定的实施例中,模块1在印刷电路板100的背面上设置有接点栅格阵列或类似的图案。硅管芯210a、210b可以具有允许q1m或q1p通过衬底接地的导电衬底。硅管芯210a、210b可以安装在pcb 100上形成的管芯焊盘上,所述管芯焊盘通过穿过pcb 100的一个或多个通孔连接到pcb 100的背面上形成的接地焊盘。信号焊盘可以设置在pcb 100的背面和边缘周围,与这种接地焊盘间隔开。通过这些信号焊盘,可以输出和输入rf信号,并且可以施加偏置电压。

54.gan管芯230a可以具有氮化镓衬底、碳化硅或硅衬底。根据衬底,穿过衬底的通孔

可以用于使得能够在gan管芯230a的背面上形成接地。以这种方式,gan管芯230a也可以安装在设置在pcb 100上的管芯焊盘上。

55.模块1可以设置有连接到pcb 100的盖子。或者,固化的模制化合物可以覆盖硅管芯210a、210b和gan管芯230a、230b以及pcb 100上的其他组件。在这样的实施例中,固化的模制化合物形成模块1的外部。在其他实施例中,模块1没有单独的盖子或模制化合物。

56.替代硅管芯210a、210b和gan管芯230a、230b直接安装在pcb 100上,也可以在将这些管芯安装在pcb 100上之前封装这些管芯。

57.图4示出了这对图2的在组合节点215a和gan管芯230a上的输入端子231a之间的网络的s11参数和s21参数。如图所示,s21参数显示了带通特性。s21特性中大约1.7ghz和3.7ghz处的陷波归因于l3和c5的并联网络以及l4和c7的并联网络。

58.使用级间匹配拓扑的优点在于,如果由接合线221a、222a形成的串联电感器受到工艺容差的影响,例如,接合线相对于它们的高度、形状或长度发生变化,则仍然可以保持s21特性的形状。例如,与接合线221a相关联的电感的增加可以通过降低与接合线222a相关联的电感来补偿。通过保持s21特性的形状,带宽性能可以保持相对恒定。

59.为了提高基于gan的hemt 232a的效率和输出功率,重要的是,确保输入端子231a在二次谐波频率下呈现短路。在图2和图3中,这可以通过适当选择低通匹配网络的串联电感和并联电容来实现。在图2和图3的实施例中,与和接合线222a相关联的串联电感器(例如,第二低通匹配网络的串联电感器)和第二匹配网络的并联电容器的串联连接相关联的谐振频率等于或接近二次谐波频率。更具体地,在二次谐波频率下,中间端子224a处朝向次级多尔蒂放大器看到的阻抗是并联电容器223a的阻抗的至少c倍,更优选d倍。此外,由电容器223a和第二低通网络的串联电感器(即由接合线222a形成的电感器)确定的串联谐振频率位于工作频率的1.6倍和2.4倍之间的范围内。后者的谐振频率ω

res

可以使用已知的等式来找到,其中,l是与接合线222a相关联的电感,c是与电容器223a相关联的电容。此外,在工作频率下或接近工作频率下,从端子216a到中间端子224a的第一低通网络的复阻抗变换比的绝对值是从中间端子224a到输入端子231a的第二低通网络的阻抗变换比的至少4倍。换句话说,代替使用相等的阻抗变换比,第二低通网络主要用于在输入端子231a处在二次谐波频率下呈现低阻抗。

60.申请人已经发现,通过以上述方式结合并联网络l4、c7和l3、c5设计级间匹配网络,可以实现宽带宽,同时确保基于gan的hemt 232a的适当的二次谐波端接。在图5中更详细地示出了后一方面,图5示出了对于在组合节点215a处连接的各种阻抗,在输入端子231a获得的s11参数。后者的阻抗模拟了在各种输入信号条件下该节点上朝向q1m和q1p看的阻抗。更具体地,组合节点215a处呈现的阻抗对应于最大比率为4∶1的vswr全相位扫描,组合节点215a处的阻抗的复共轭朝向基于gan的hemt 232a,作为参考阻抗。从史密斯圆图中可以看出,不管组合节点215a处的阻抗如何,在二次谐波频率处呈现的有效阻抗接近rf短路。

61.在上文中,已经使用本发明的详细实施例解释了本发明。然而,本发明不限于这些实施例。相反,在不脱离由所附权利要求及其等同物限定的本发明的范围的情况下,各种修改是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1