一种收发合置低噪声放大电路的制作方法

1.本发明属于声呐设备领域,具体涉及一种高频收发合置声纳设备中的低噪声接收电路。

背景技术:

2.声纳设备,尤其是高频声纳,诸如adcp,往往采用收发合置的形式,而且发射电路只有一个,同时驱动多个换能器,这些换能器同时也作为接收信号的传感器。为了防止高压发射期间,大电压对前置电路的损坏,需要在发射和接收电路之间插入一个收发转接电路,而传统的收发转接电路方案是接入一个大功率电阻和保护二极管对将前置的输入电压限制在二极管的管压降,防止前置电路的损坏。但是收发转接电路的接入势必会引入各种噪声,从而增大前置电路的噪声,降低声纳的整机性能。因此如何对收发转接电路进行改进,降低前置电路的噪声,是目前亟待解决的技术问题。

技术实现要素:

3.本发明的目的在于解决现有技术中存在的问题,并提出一种收发合置低噪声放大电路,该电路不仅实现了发射期间对前置电路的保护,还可以进一步降低前置电路的噪声,实现收发合置声纳的低噪声接收。

4.为实现上述发明目的,本发明具体采用的技术方案如下:

5.一种收发合置低噪声放大电路,其用于收发合置声纳设备中在水下换能器发射期间对前置电路进行保护同时降低前置电路的噪声,其包括收发转接电容c1、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、二极管对d1、jfet对管q1、恒流源q2和运算放大器u1;

6.所述水下换能器一端与收发转接电容c1的一端相连,水下换能器的另一端接模拟地,收发转接电容c1的另一端与二极管对d1的一端、第一电阻r1的一端、jfet对管q1的第一个g极(栅极)相连,二极管对d1的另一端与模拟地相连,第一电阻r1的另一端与模拟地相连,第二电阻r2的一端与jfet对管q1的第一个d极(漏极)、运算放大器u1的反向输出端相连,第三电阻r3的一端与jfet对管q1的第二个d极、运算放大器u1的同向输入端相连,第二电阻r2和第三电阻r3的另一端与正电源相连,jfet对管q1的两个s极(源极)短接在一起后与恒流源q2的一端相连,恒流源q2的另一端与负电源相连,运算放大器u1的输出与第五电阻r5的一端相连,第五电阻r5的另一端与第四电阻r4的一端,jfet对管q1的第二个g极相连,第四电阻r4的另一端与模拟地相连。

7.作为优选,所述收发合置声纳设备为38khz的adcp。

8.作为优选,所述第一电阻r1的阻值为1mω,所述第二电阻r2的阻值为1.2kω,所述第三电阻r3的阻值为1.2kω,所述第四电阻r4的阻值为100ω,所述第五电阻r5的阻值为2kω,所述收发转接电容c1的容值为2.7nf。

9.作为优选,所述二极管对d1的型号为bav199。

10.作为优选,所述恒流源q2是由ls310构成的恒流源

11.作为优选,所述jfet对管q1的型号为lsk389。

12.作为优选,所述运算放大器u1的型号为opa209。

13.作为优选,所述收发转接电容c1的耐压值不小于水下换能器发射电压的2倍。

14.作为优选,所述收发转接电容c1采用陶瓷类电容。

15.作为优选,所述收发合置低噪声放大电路中的电阻器件选择金属膜电阻。

16.相对于现有技术而言,本发明的有益效果如下:

17.本发明提出了一个低噪声收发合置电路前置放大方案,该方案通过采用低esr、高耐压电容器替换传统收发转接电路中具有相同阻抗的功率电阻的方法,消除了收发转接电阻自身的热噪声,降低了接收电路的总体噪声;而对于接收电路的第一级放大电路(前置放大电路),则提出了采用低噪声jfet对管配合低噪声运放的放大电路拓扑方案,利用低噪声jfet对管的极低电流噪声特性,消除了由放大器件电流噪声和收发转接阻抗引起的电路噪声,进一步的降低了电路噪声。该路拓扑不仅减小了收发转接电路体积,还降低了前置电路的噪声,特别适合用于高内阻收发合置声纳设备的低噪声放大电路中,具有一定的推广价值。

附图说明

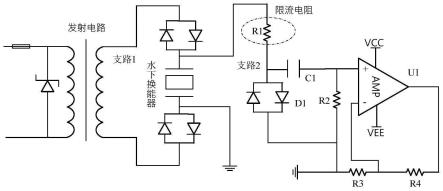

18.图1是改进前的收发转接及前置放大电路拓扑;

19.图2是改进后的收发转接及前置放大电路拓扑;

20.图3是收发合置换能器等效模型。

21.图4是改进前的接收电路等效电路;

22.图5是改进前的接收电路噪声模型;

23.图6是改进后的接收电路等效电路;

24.图7是改进后的接收电路噪声模型;

具体实施方式

25.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图对本发明的具体实施方式做详细的说明。在下面的描述中阐述了很多具体细节以便于充分理解本发明。但是本发明能够以很多不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本发明内涵的情况下做类似改进,因此本发明不受下面公开的具体实施例的限制。本发明各个实施例中的技术特征在没有相互冲突的前提下,均可进行相应组合。

26.在本发明的描述中,需要理解的是,术语“第一”、“第二”仅用于区分描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。

27.在本发明的一个较佳实施例中,针对传统的声纳设备收发转接及前置放大电路进行了改进,将收发转接电路的限流电阻替换为低esr、高耐压电容以减小电路体积,同时采用低噪声jfet对管加低噪声运放的前置电路拓扑以降低电路噪声,从而设计了一种改进后的收发转接及前置放大电路拓扑,即收发合置低噪声放大电路,该电路可用于收发合置声纳设备中在水下换能器发射期间对前置电路进行保护同时降低前置电路的噪声。下面对本

发明的具体实现方式进行详细展开描述,同时理论分析改进前后电路噪声性能。

28.1.收发合置低噪声放大电路拓扑的改进

29.传统的声纳设备收发转接及前置放大电路拓扑如图1所示,该电路拓扑选用功率电阻来实现对前置电路的限压限流保护功能。当声纳工作在发射模式下时,高压发射电源的支路1是直接加载在换能上实现电能和声能的转换,支路2则是通过限流电阻r1和保护二极管返回。为了减少限流电阻对发射效率的影响,需要串联一个较大的阻值,但与此同时,大的阻值就会带来很大的热噪声(1k电阻的典型热噪声为),同时前置接收电路中的运放本身的电流噪声经过该电阻也会带来很大的噪声。因此一般选择该功率电阻时需要在发射效率和前置电路噪声之间进行一个折中(一般选择电阻值为10倍的换能器等效电阻值)。

30.此外,传统的第一级放大电路一般选择集成运放,集成运放的优点是使用简单方便,性能稳定,但缺点是其噪声较高,在传感器高内阻高、传感器灵敏度低的应用场景下,难以满足越来越高的电路噪声要求。以传统的收发合置声纳设备为例,采用bjt集成运放可以实现极低的电压噪声(左右),但其电流噪声很大(几个),这些电流噪声流过传感器内阻及收发转接回路的电阻(或者电容)所产生的噪声将占据主导地位;同样的,采用fet型集成运放,虽然其电流噪声较低(一般为级别)但其电压噪声却很大。

31.因此,基于采用功率电阻和集成运放对电路整体噪声的不利影响分析,本成果提出了用电容替换电阻的收发转接电路拓扑,同时利用分立jfet低噪声、高输入阻抗、低寄生电容的优点,给出了优化后的收发转接及前置放大电路拓扑,改进后的收发转接及前置放大电路拓扑如图2所示。其中水下换能器与发射电路以及两者的组合关系属于换能器的常规结构,对此不再赘述。

32.在图2所示的收发合置低噪声放大电路中,具体组件包括收发转接电容c1、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、二极管对d1、jfet对管q1、恒流源q2和运算放大器u1。其中,水下换能器一端与收发转接电容c1的一端相连,水下换能器的另一端接模拟地,收发转接电容c1的另一端与二极管对d1的一端、第一电阻r1的一端、jfet对管q1的第一个g极(栅极)相连,二极管对d1的另一端与模拟地相连,第一电阻r1的另一端与模拟地相连,第二电阻r2的一端与jfet对管q1的第一个d极(漏极)、运算放大器u1的反向输出端相连,第三电阻r3的一端与jfet对管q1的第二个d极、运算放大器u1的同向输入端相连,第二电阻r2和第三电阻r3的另一端与正电源相连,jfet对管q1的两个s极(源极)短接在一起后与恒流源q2的一端相连,恒流源q2的另一端与负电源相连,运算放大器u1的输出与第五电阻r5的一端相连,第五电阻r5的另一端与第四电阻r4的一端,jfet对管q1的第二个g极相连,第四电阻r4的另一端与模拟地相连。

33.2.收发转接电路器件选型

34.2.1收发转接电容c1选型

35.1)容值选择

36.根据声纳设备换能器导纳曲线,得出换能器的等效电路模型,换能器等效模型如图3所示。计算出其等效内阻(动态电阻)。由换能器等效模型可知,在串联谐振点,换能器等

效为一个静态电容和一个动态电阻的并联。经过等效变换后,可等效成电容和电阻的串联模型如图5所示,经过变换后电阻基本不变(r≈r’),电容变大。为了减小收发转接电容带来的信号损失,同时不影响发射工作模式时的发射效率,收发转接电容的计算公式如下:

[0037][0038]

其中,ω=2*π*f0,f0为换能器的工作频率;

[0039]

r为换能器的等效动态电阻;

[0040]

g为换能器等效动态电导。

[0041]

2)耐压选择:收发转换电容额定耐压的选择需根据声纳工作时的最大输出来确定,考虑到发射电路变压器、匹配电感等感性参数的影响,一般选择电容的耐压值不小于发射电压的2倍。

[0042]

3)电容类型:由于收发转接电容在接收工作模式下要接收微弱信号,此外还考虑到多通道之间的一致性,尽量选择低esr、低温漂的陶瓷类电容。

[0043]

2.2jfet选型

[0044]

考虑到jfet器件的电流噪声一般都比较低,因此我们应当选择低电压噪声,高跨导,低寄生电容的器件,目前低噪声jfet器件的电压谱级噪声已经可以做到左右,寄生电容仅为5pf左右。

[0045]

2.3其他器件选型

[0046]

为了提高电路的噪声性能,电路拓扑中的电阻器件应选择低噪声的金属膜电阻,除收发转接电容以外的其他电容也尽量选择低温漂系数、低esr的陶瓷电容。

[0047]

3.噪声模型对比分析

[0048]

3.1改进前的电路拓扑噪声模型分析

[0049]

改进前的接收电路等效电路及其噪声模型分别如图4,5所示。

[0050]

从图5中可以看出,改进前的噪声源有:

[0051]

1)运放自身的电压噪声ev;

[0052]

2)运放电流噪声在正输入端引起的噪声e

a1

;(正输入端的等效阻抗r1'为收发转接电阻r1与输入电容c1串联后与r2并联的值,由于r2一般选择远远大于r1和c1的串联值,因此,r1'≈r1+z

c1

);

[0053]

3)运放电流噪声在负输入端引起的噪声e

a2

;(负输入端的等效阻抗为r2'≈r3//r4)

[0054]

4)正输入端电阻引起的热噪声e

r1'

;

[0055]

5)负输入端电阻引起的热噪声e

r2'

;

[0056]

改进前的总噪声

[0057]

3.2改进后的电路拓扑噪声模型分析

[0058]

改进后的接收电路等效电路及其噪声模型如图6,7所示。

[0059]

从图7中可以看出,改进之后主要的噪声源有:

[0060]

1)jfet对管的电压噪声e

j1

,e

j2

;

[0061]

2)jfet电流噪声在输入端引起的噪声e

a1

;(输入端的等效阻抗为收发转接电容c1

与r1并联的值,由于r1一般选择远远大于c1等效阻抗,所以输入端的等效阻抗为收发转接电容c1的容抗);

[0062]

3)输入端阻抗引起的噪声ei;

[0063]

4)jfet漏极电阻热噪声e

r2

,e

r3

;

[0064]

5)运放反馈电阻引起的电流噪声e

a2

(反馈电阻等效阻抗为r2'=r4//r5≈r4);

[0065]

6)运放反馈电阻引起的热噪声e

r2'

;

[0066]

7)恒流源电路引起的噪声e

q2

:由于电路对称性,该噪声忽略不计。

[0067]

改进之后的总噪声

[0068]

其中,由于采用了电容替换了电阻,改进后的信号输入端电阻热噪声是输入电容c1与电阻r1并联后的热噪声在工作频带内的噪声,这个噪声可用下面的公式计算:

[0069][0070]

其中,k为玻耳兹曼常数,k=1.38

×

10-23

j/k;温度t为绝对温度;fc是收发转接电容c1和r1构成的高通滤波器截止频点,即f0声纳的工作频点。由这个公式可以看出,要减小这个噪声的影响,就要选择较大的对地电阻r1。

[0071]

而jfet器件的电流噪声很小(一般为),在高频adcp设备中,换能器等效阻抗较低(一般为几十欧姆),而收发转接电容的阻抗一般不大于1kω,jfet电流噪声流过输入端阻抗引起的电压噪声为级别,对比器件本身的电压噪声,在换能器阻抗较低(不大于100kω)的情况下,由jfet引起的电流噪声可以忽略不计,即e

a1

可以忽略不计。

[0072]

此外,该电路拓扑的漏极电阻r2和r3的等效阻值计算公式为:

[0073][0074]

其中,gm是jfet的跨导参数,一般为几个至几十个ms(豪西门子)。

[0075]

4.实际电路计算分析

[0076]

以实际工作在38khz的adcp为例(中心频率为38khz,带宽为8khz)。利用低噪声运放opa209和1.5kω收发转接电阻设计图1所示的改进前的收发合置及放大电路。另外,利用低噪声jfet对管lsk389和低噪声运放opa209以及2.7nf(c1,电容的在中心频率处的容抗与改进前的收发转接电阻阻值相同)的收发转接电容设计图2所示的改进后的收发合置低噪声放大电路,并分别对两个电路进行噪声计算。

[0077]

4.1电路参数设计

[0078]

在该adcp中,选择系统的工作电压为

±

5v。

[0079]

第一电阻r1的阻值为1mω,第二电阻r2的阻值为1.2kω,第三电阻r3的阻值为1.2kω,第四电阻r4的阻值为100ω,第五电阻r5的阻值为2kω,收发转接电容c1的容值为2.7nf,二极管对d1的型号为bav199,恒流源q2是由型号为ls310的bjt对管构成的恒流源。改进前后的电路总放大倍数为21倍。jfet对管q1的型号为lsk389,运算放大器u1的型号为opa209。

[0080]

选择lsk389对管作为前级差分电流的放大器件时,lsk389b的噪声与其漏极电流有关,漏极电流越大,其噪声就越小。因此,源级采用低噪声三极管设计一个镜像电流源,设置其源级电流为4ma,lsk389b对管的漏极工作电流ids为2ma,漏极电阻选择1.2kω,使其直流偏置电压为2.4v左右。

[0081]

lsk389的电压噪声为电流噪声约为电流噪声约为跨导为20ms。

[0082]

opa209的电压噪声电流噪声

[0083]

4.2改进前电路噪声计算

[0084]

1)opa209的电压噪声:

[0085]

2)opa209电流噪声在正输入端引起的噪声2)opa209电流噪声在正输入端引起的噪声

[0086]

3)opa209电流噪声在负输入端引起的噪声3)opa209电流噪声在负输入端引起的噪声

[0087]

4)正输入端等效电阻热噪声:

[0088]

5)负输入端等效电阻热噪声:

[0089]

改进前的电路总噪声理论值为:改进前的电路总噪声理论值为:

[0090]

如果考虑将收发转接电阻换成同样容值的电容(2.7nf),则重新计算改进前的电路噪声为可以看到将电阻换为电容会大幅减小电路的噪声。

[0091]

4.3改进后电路噪声计算

[0092]

首先计算相关的等效参数:因此漏极电阻的噪声可以忽略不计;输入截止频率为fo=38000hz。

[0093]

1)lsk对管电压噪声:

[0094]

2)jfet电流噪声在输入端引起的噪声e

a1

:该噪声可以忽略不计;

[0095]

3)输入阻抗引起的热噪声:

[0096]

4)漏极电阻引起的噪声e

r2

:由于漏极等效电阻为4ω,该噪声可以忽略不计;

[0097]

5)电流噪声流过反馈电阻引起的噪声e

a2

:该噪声可以不略不计;

[0098]

6)反馈电阻的热噪声:

[0099]

改进后的电路总噪声理论值为:改进后的电路总噪声理论值为:

[0100]

对比改进前后的低噪声放大电路拓扑,可以发现改进后的电路去除了收发转接电阻引起的热噪声,去除了信号输入端、反馈端因电流噪声引起的噪声(jfet的电流噪声极低)。而低噪声jfet的使用,使得该电路拓扑放大器件的电压噪声也可以控制到与低噪声集成运放相当的水平。因此,改进后的放大电路噪声性能对比改进前的电路噪声(电阻换为电容),也可以改善1.5db。

[0101]

需要说明的是,本发明中主要提供了一种低噪声放大电路拓扑,但是上述电路中的器件选型及参数,可以根据实际的应用常见进行优化,上述具体参数及选型仅仅为针对38khz的adcp所设计的一种示例性方案。

[0102]

以上所述的实施例只是本发明的一种较佳的方案,然其并非用以限制本发明。有关技术领域的普通技术人员,在不脱离本发明的精神和范围的情况下,还可以做出各种变化和变型。因此凡采取等同替换或等效变换的方式所获得的技术方案,均落在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1