成像装置及成像方法与流程

1.下面描述的实施例涉及例如用于静止图像和/或电影的成像装置/方法。

背景技术:

2.用于静止图像和/或电影的成像装置和成像方法通常被广泛使用。成像装置例如数码相机、蜂窝电话、终端设备和汽车(车载相机),但不限于此。

技术实现要素:

3.包括下面所示的方面的本发明内容可以涉及例如用于静止图像和/或电影的成像装置/方法。应当理解,下面的公开内容并不限制或约束待决的申请/发明。

4.第一方面是一种成像装置,所述成像装置包括比较器、像素和控制电路,其中,所述比较器包括开关、第一晶体管和第一电容器,其中,当所述开关接通时,所述第一电容器被充电,并且其中,在所述开关断开之后,所述比较器使用在所述第一电容器中充入的电力,比较从所述像素输入的像素信号与从所述控制电路输入的斜坡信号,并输出输出信号。

5.第二方面是根据上述方面所述的成像装置,其中,所述斜坡信号包括第一斜坡信号和第二斜坡信号。

6.第三方面是根据上述方面所述的成像装置,其中,所述斜坡信号包括所述第一斜坡信号与所述第二斜坡信号之间的预定电压差。

7.第四方面是根据上述方面所述的成像装置,其中,当所述第一斜坡信号达到与所述像素信号相同的电平时,所述比较器使所述输出信号反转。

8.第五方面是根据上述方面所述的成像装置,其中,当将与所述预定电压差具有相同电压电平的电压施加到所述第一晶体管的栅极端子时,所述第一晶体管使偏置电流流过以驱动所述比较器。

9.第六方面是根据上述方面所述的成像装置,其中,所述第一电容器的电容足够大以驱动所述比较器。

10.第七方面是根据上述方面所述的成像装置,其中,当所述第二斜坡信号达到与所述像素信号相同的电平时,所述比较器完成其比较操作。

11.第八方面是根据上述方面所述的成像装置,其中,当所述开关断开时,所述比较器与所述成像装置的公用电源断开连接。

12.第九方面是根据上述方面所述的成像装置,其中,所述第一斜坡信号和所述第二斜坡信号是斜升信号。

13.第十方面是根据上述方面所述的成像装置,其中,所述第一斜坡信号和所述第二斜坡信号是斜降信号。

14.第十一方面是一种用于包括比较器、像素和控制电路的成像装置的成像方法,所述成像方法包括:当所述比较器的开关接通时,对所述比较器的第一电容器充电;在所述开关断开后,使用在所述第一电容器中充入的电力比较从所述像素输入的像素信号与从所述

控制电路输入的斜坡信号;输出输出信号。

15.第十二方面是根据上述方面所述的成像方法,其中,所述斜坡信号包括第一斜坡信号和第二斜坡信号。

16.第十三方面是根据上述方面所述的成像方法,其中,所述斜坡信号包括所述第一斜坡信号与所述第二斜坡信号之间的预定电压差。

17.第十四方面是根据上述方面所述的成像方法,其中,当所述第一斜坡信号达到与所述像素信号相同的电平时,所述比较器使所述输出信号反转。

18.第十五方面是根据上述方面所述的成像方法,其中,当将与所述预定电压差具有相同电压电平的电压施加到所述第一晶体管的栅极端子时,所述第一晶体管使偏置电流流过以驱动所述比较器。

19.第十六方面是根据上述方面所述的成像方法,其中,所述第一电容器的电容足够大以驱动所述比较器。

20.第十七方面是根据上述方面所述的成像方法,其中,当所述第二斜坡信号达到与所述像素信号相同的电平时,所述比较器完成其比较操作。

21.第十八方面是根据上述方面所述的成像方法,其中,当所述开关断开时,所述比较器与所述成像装置的公用电源断开连接。

22.第十九方面是根据上述方面所述的成像方法,其中,所述第一斜坡信号和所述第二斜坡信号是斜升信号。

23.第二十方面是根据上述方面所述的成像方法,其中,所述第一斜坡信号和所述第二斜坡信号是斜降信号。

24.上述公开内容并不限制或约束本技术/发明。

附图说明

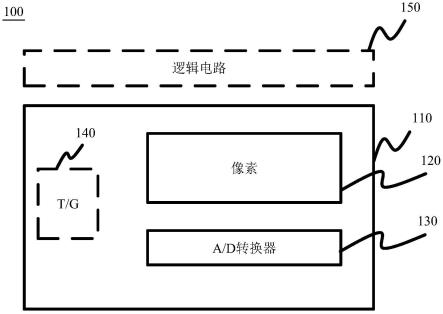

25.图1是在一个实施例中描述的成像装置的示意图。

26.图2是一个实施例的电路图。

27.图3是一个实施例的时序图。

28.图4是一个实施例的电路图。

29.图5是一个实施例的时序图。

具体实施方式

30.下面的公开内容仅包括示例。本发明和申请的范围不应被认为受到下面所示的实施例的限制。

31.图1示出了一个实施例的成像装置的示意图。成像装置100包括相机模块110、像素120、模数(analog to digital,ad)转换器130和定时发生器(timing generator,t/g)140。成像装置100可以包括替换t/g 140的逻辑电路150。成像装置100还可以包括一组透镜、电池、存储器和屏幕或面板等。成像装置100还可以包括处理器、硬盘、光盘驱动器、收发器、扬声器和麦克风等。

32.相机模块110包括像素120、ad转换器130和t/g 140。如上所述,t/g 140可以替换为相机模块110外部的逻辑电路150。相机模块110可以是图2中所示的图像传感器电路。

33.像素120可以是互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)图像传感器、电荷耦合器件(charge coupled device,ccd)图像传感器或其它器件。像素120可以由多个像素构成。像素120还可以包括滤色器。像素120通过图中未示出的透镜接收光,并输出与所接收的光的强度对应的模拟信号。

34.ad转换器130被输入来自像素120的模拟信号,并输出指示像素120所接收的光的强度的数字信号。图中未示出的处理器可以接收来自ad转换器130的数字信号并生成图像数据。该处理器可以将图像数据存储在例如存储器中。图像数据可以是静止图像或电影的一部分。

35.t/g 140(或逻辑电路150)输出指示操作时序的脉冲信号,成像装置100的构成元件基于该操作时序进行操作。例如,当从t/g 140(或逻辑电路150)输入定时信号时,ad转换器130可以比较从像素120输出的模拟信号的电压与图1中未示出的参考电压。

36.在下文中,参考附图解释ad转换器130的细节。

37.成像装置可以包括ad转换器,例如,单斜率ad转换器(single slope analog to digital converter,ss adc)。通常,期望在不造成副效应的情况下降低ss adc的功耗。

38.例如,可以仅通过减少ad转换器中包括的比较器的偏置电流来降低ad转换器(ss adc除外)的功耗。降低功耗的偏置电路的一个示例是使用动态偏置电路实现的。另一方面,更少的偏置电流可能会降低比较器的性能(例如模数转换性能):速度降低、噪声增大和/或ad精度降低。

39.如上所述,通常,期望降低adc的功耗。需要说明的是,将比较器的可以降低ad转换器的功耗的动态偏置电路应用于ss adc并不是最优选择。

40.因为通常,具有动态偏置电路的比较器可以比较与输入数字信号对应的输入信号,而在ss adc中,这些数字信号在ad转换操作期间无法生成。

41.通常,动态偏置比较器可能会引起大的“条带噪声”。这是因为动态偏置电路会引起比较器的电源电流发生大量变化。这可能会对图像质量产生负面影响。

42.在下文中,将解释第一实施例。图2示出了包括两个输入像素信号线(vpixel1和vpixel2)和两个单斜率adc的图像传感器电路。图2中所示的图像传感器电路示出了简化的结构,以便更容易地解释它们的操作。在实际的图像传感器中,需要放置更多的adc,这些adc通常是列式的,以适应像素信号输出的数量。图2中所示的图像传感器电路对应于图1中所示的相机模块。

43.输入像素信号线vpixel1和vpixel2包括在图1中所示的像素120中。输入像素信号线vpixel1和vpixel2中的每一个对应于一个像素。图2中所示的i1和i2是比较器。比较器i1通过输入像素信号线vpixel1接收来自图2中未示出的像素的信号。比较器i2通过输入像素信号线vpixel1输入来自图2中未示出的像素的信号。

44.图2中所示的vramp1和vramp2表示通过线提供的斜坡参考电压。比较器i1从端子3接收斜坡参考电压vramp1。比较器i1从端子2接收斜坡参考电压vramp2。比较器2具有与比较器i1相同的结构。斜坡参考电压vramp1和vramp2可以从图2中未示出的控制电路(例如,图1中所示的逻辑电路150)输出。

45.图2中所示的vdd_common是与所有或部分比较器共享的公用电源。比较器i1通过端子1接收公用电源vdd_common并进行其操作。比较器i2具有与比较器i1相同的结构。公用

电源vdd_common可以从附图中未示出的电源电路供电。

46.比较器i1接收斜坡参考电压vramp1/vramp2和输入像素电压(为了便于理解,在下文中为vpixel1),并进行比较操作。比较器i1从图2中所示的端子vout1输出指示其比较结果的信号。比较器i2从图2中所示的端子vout2输出指示其比较结果的信号。

47.比较器i1包括晶体管m1、m2、m3、m4、m6、m7、m8、m9和m10。比较器i1包括电容器cp、cg和cs。比较器i1包括开关sw1。比较器i1包括端子1至5。端子1连接到公用电源vdd_common。端子2接收斜坡参考电压vramp2。端子3接收斜坡参考电压vramp1。端子4连接到输入像素信号线vpixel1。来自比较器i1的输出信号从端子5输出并提供给计数器电路i3。

48.比较器i2具有与比较器i1基本相同的结构。它们之间有很小的区别。比较器i2的端子4连接到输入像素信号线vpixel2,比较器i2的输出信号通过端子5提供给计数器电路i4。

49.计数器电路i3接收来自端子vout1的输出信号。计数器电路i3接收时钟信号(clk)。在预定的时间段内,计数器电路i3对时钟信号中包括的时钟进行计数,同时计数器电路检测来自端子vout1的输出信号。时钟信号(clk)可以由附图中所示的控制电路(例如,图1的逻辑电路150)输出。

50.计数器电路i4接收来自端子vout2的输出信号。计数器电路i4接收时钟信号(clk)。在预定的时间段内,计数器电路4对包括在时钟信号中的时钟进行计数,同时计数器电路检测来自端子vout1的输出信号。时钟信号(clk)可以由附图中所示的控制电路(例如,图1的逻辑电路150)提供。

51.参考图3中所示的时序图描述图2中所示的图像传感器电路的操作。在图3中,假设与输入像素信号线vpixel1对应的第一像素信号电平(为了便于理解,在下文中为vpixel1)低于与输入像素信号线vpixel2对应的第二像素信号电平(为了便于理解,在下文中为vpixel2)。在实际使用中,第一像素信号电平vpixel1可以高于第二像素信号电平vpixel2或与第二像素信号电平vpixel2相同。图3的水平轴是时间轴。

52.在图3中,斜坡参考电压vramp2高于斜坡参考电压vramp1,并以预定的偏移电平(vth)精确跟踪斜坡参考电压vramp1。斜坡参考电压vramp1最初处于预定的初始电平(vinit)。在预定的时序下,斜坡参考电压vramp1开始以恒定速率从vinit斜升。例如,当用户操作成像装置拍摄照片或拍摄电影时,斜坡参考电压开始斜升。当斜坡参考电压vramp1开始斜升时,斜坡参考电压vramp2同时以与vramp 1相同的速率从高于vramp 1的预定电平(vinit+vth)开始斜升。斜坡参考电压vramp1和vramp2都在相同的时序暂停斜升,并将其保持在预定电平。

53.偏移电平vth是预定电压,并且可以设计成图2中所示的晶体管m5使目标偏置电流流过所使用的电压。晶体管m5具有接地的源极端子。当电压施加到晶体管m5的栅极端子时,晶体管m5充当比较器的电流源。

54.图2中所示的晶体管m5可以是mos晶体管。例如,晶体管m5的漏极电流(id)如下确定。

55.id=k*w/l*(vgs

–

vt)2ꢀꢀꢀ

(1)

56.在公式(1)中,k:常数,w:沟道宽度,l:沟道长度,vgs:栅极端子与源极端子之间的电压差,vt:阈值电压。

57.如果假设“k”、“w”、“l”和“vt”都是已知的,并且可以确定或预定目标漏极电流id,则可以使用公式(1)自动计算“vgs”。当源极端子接地且vth施加于栅极端子时,vth等于vgs。因此,将预定偏移电平vth施加到晶体管m5的栅极端子。

58.这里,目标漏极电流id可以考虑例如比较器i1和i2的功耗、随机噪声、电压增益、瞬态响应等来确定。

59.在图2中,每个像素信号(为了便于理解,vpixel1或vpixel2)被馈送到比较器i1(或i2)的负极输入端(端子4),比较器i1(或i2)将像素信号vpixel1(或vpixel2)与斜坡参考电压vramp1进行比较。另一个斜坡参考电压vramp2用于将电压施加到晶体管m5的栅极端子。该参考电压vramp2可通过附图中未示出的采样/保持电路提供。晶体管m5充当比较器i1(或i2)的偏置电流源。

60.在下文中,解释比较器i1/i2的基本操作。该实施例中的比较器i1、i2可以是差分放大器。比较器i1和i2具有相同的结构,包括晶体管m1至m5。晶体管m1和m2可以是由电流源晶体管m5驱动的nmos差分输入晶体管。晶体管m3和m4用作输入晶体管m1和m2的负载晶体管。晶体管m3和m4可以理解为电流镜电路。

61.在该实施例中,假设晶体管m1和m2的大小相同,晶体管m3和m4的大小相同。当晶体管m1的栅极端子电压高于晶体管m2的栅极端子电压时,晶体管m1的漏极电流(idm1)大于晶体管m2的漏极电流(idm2)。晶体管m1的漏极电流(idm1)等于晶体管m3的漏极电流(idm3)。由于晶体管m3和m4充当电流镜电路,因此晶体管m3的漏极电流被镜像到晶体管m4的漏极电流(idm3=idm4)。

62.比较器i1(或i2)的输出电流通过晶体管m2的漏极电流与晶体管m4的漏极电流之间的差(idm4

–

idm2)产生。由于来自晶体管m2的漏极电流小于晶体管m1的漏极电流,因此晶体管m1与m2之间的漏极电流差(idm1

–

idm2)超出端子5的比较器i1(或i2)的输出电流。输出端子阻抗可以设计为具有高值,因此,输出电压可以相应地升高。

63.在图2中,来自像素的每个信号(输入像素电压vpixel1/vpixel2)被馈送到比较器i1(或i2)的负极输入端(端子4)。比较器i1(或i2)将像素信号与斜坡参考电压(vramp1)进行比较。其它斜坡参考电压(vramp2)用于通过采样/保持电路向晶体管m5的栅极端子(通过晶体管m7)提供电压。晶体管m5充当比较器i1(或i2)的偏置电流源。

64.如上所述,预定偏移电平vth可以设计成偏置电流源晶体管m5以使目标偏置电流流向比较器i1(或i2)的电压电平。当斜坡参考信号vramp1达到与输入像素信号(vpixel1/vpixel2)相同的电平时,比较器i1(或i2)可以具有电压增益,该电压增益具有足以比较输入信号的电平。该情况发生的时序是图3中所示的“t5”。

65.如图2中所示,来自比较器i1(或i2)的输出通过端子vout1(或vout2)提供给计数器电路i3(或i4)。计数器电路i3(或i4)对从端子clk提供的脉冲数量进行计数,同时来自比较器i1(或i2)的输出的输出电压电平保持在低电平。该情况对应于图3中所示的“t1”至“t5”。以类似的方式,当斜坡参考电压vramp1低于输入像素电压vpixel2时,计数器电路i4对通过端子clk施加的脉冲数量进行计数。因此,来自计数器电路i3的输出值可以不同于计数器电路i4的输出值。例如,图1中所示的逻辑电路150可以接收来自计数器电路i3(或i4)的输出值,并使用输出数字值生成图像。

66.在图3中,在时序t1处,当脉冲φpw变为高电平时,开关sw1接通。公用电源vdd_

common通过开关sw1提供给比较器i1(或i2)的本地电源线vdd1(或vdd2)。对作为存储电容器的电容器cp充电,以便与公用电源vdd_common具有相同的电压。在“t1”之前,开关sw1保持断开,具有一个接地端子的电容器cp不充电。脉冲φpw和其它脉冲信号可以从例如逻辑电路150或t/g 140提供。

67.在时序t1处,脉冲φpw变为高电平,开关sw1相应地接通。然后,从时序t1至t2,对电容器cp充电。在时序t2处,脉冲φpw变为低电平,开关sw1断开,比较器i1(或i2)的本地电源线vdd1(或vdd2)与公用电源vdd_common断开连接。在t3之后,比较器i1(或i2)使用存储在电容器cp中的电力进行其操作。因此,例如,当比较器i1(或i2)进行比较功能时,可以将每个比较器的本地电源线彼此隔离,因此,可以减少由比较器(i1、i2)之间的电源线相关串扰引起的负面影响。由于电源线的串扰更少且电源线更稳定,因此这样可以促使提高通过成像装置100获得的图像的质量。此外,比较器i1(或i2)仅在需要进行比较操作时消耗功率,因此,可以降低成像装置100的功耗。需要说明的是,成像装置100可以包括数百万或更多的像素和比较器。这些整个电路的功耗可以显著降低,这对于获得高分辨率图像的设备十分有益。

68.在时序t3处,从逻辑电路150或t/g 140提供的脉冲φ1变为高电平,比较器i1(或i2)中的晶体管m8和m10导通。电容器cg的一个端子通过晶体管m8连接到端子4,并且输入像素电压vpixel1(或vpixel2)施加到端子4。电容器cg的另一个端子通过晶体管m10连接到比较器i1(或i2)的接地端子。

69.在图3中,当脉冲φ1变为高电平时,施加到晶体管m6的栅极端子的脉冲φ同时变为高电平。具有接地源极端子的晶体管m6导通,然后,将连接到晶体管m6的漏极端子和源极端子的电容器cs放电。晶体管m5的源极端子连接到电容器cs,因此,晶体管m5的源极端子的电压电平变为接地电平。

70.在时序t4处,脉冲φ1变为低电平,由逻辑电路150或t/g 140提供的脉冲φ2变为高电平。晶体管m8和m10由于施加到它们的栅极端子上的脉冲φ1而截止。当晶体管m8截止时,电容器cg的一个端子与端子4断开连接。当晶体管m10截止时,电容器cg的另一个端子与比较器i1(或i2)的接地端子断开连接。

71.在时序t4处,晶体管m7由于施加到晶体管m7的栅极端子上的脉冲φ2而导通。电容器cg的一个端子通过晶体管m7连接到端子2。在时序t4处,晶体管m9由于施加到晶体管m9的栅极端子上的脉冲φ2而导通。电容器cg的另一个端子通过晶体管m9连接到晶体管m5的栅极端子。晶体管m5充当比较器i1中的电流源。由于斜坡参考电压vramp2施加到端子2,并且电容器cg中的电荷被保存,即电容器cg的两个端子之间的电压差保持恒定,因此可以理解的是,晶体管m5的栅极电压(图2中所示的“vgate”)可以用以下公式“vinit+vth

–

vpixel1”计算。在比较器i2的情况下,该公式为“vinit+vth

–

vpixel2”。

72.在图3中所示的时序t5处,斜坡参考电压vramp1达到输入像素电压vpixel1。由于施加到比较器i1的斜坡参考电压vramp1中的电压增加是通过“vpixel1

–

vinit”获得的,并且斜坡参考电压vramp1与vramp2之间的电压差为vth,因此施加到比较器i1中晶体管m5的栅极端子的电压可以根据下面所示的公式获得。

73.{(vinit+vth

–

vpixel1)+(vpixel1

–

vinit)}=vth

74.这表示晶体管m5可以使足够大以驱动比较器i1的偏置电流流过,比较器i1的输出

变为高电平,并且有一定量的延迟时间响应其输入电压变化。这些响应在图3中示为“vout1”和“ibias1”。

75.在图3中所示的示出t6处,斜坡参考电压vramp1达到输入像素电压vpixel2。由于比较器i2的斜坡参考电压vramp1中的电压增加为(vpixel2

–

vinit),其中,斜坡参考电压vramp1与vramp2之间的电压差为vth,因此可以理解的是,施加到比较器i2中包括的晶体管m5的栅极端子的电压(vgate)通过下面所示的公式获得。这与比较器i1类似。

76.{(vinit+vth

–

vpixel2)+(vpixel2

–

vinit)}=vth

77.这表示晶体管m5可以使足够大以驱动比较器i2的偏置电流流过,比较器i2的输出变为高电平,并且有一定量的延迟时间响应其输入电压变化。这些响应在图3中示为“vout2”和“ibias2”。

78.如上所述,由于每个比较器i1/i2的偏置电流仅在斜坡参考电压vramp1的电平接近其输入像素信号电平(vpixel1或vpixel2)时流动,因此与一些传统ss adc中由恒定电流源驱动的比较器相比,比较器i1和i2的功耗降低。此外,偏置电流在比较器i1/i2中流动的时序可以由输入信号电平和斜坡参考电平(vramp1/vramp2)自动控制。

79.图2中所示的电容器cp的电容用于在图3中所示的t2之后操作比较器i1/i2。在时序t2处,开关sw1断开,比较器i1/i2与公用电源vdd_common断开连接。当实现与比较器i1/i2的比较操作时,具有以下信息可能是有帮助的:可以如何估计电容器cp的电容,以及上文公开的比较器(i1/i2)在与公用电源线(vdd_common)断开连接后如何正确操作其本地电源线(vdd1/vdd2)。

80.在估计电容器cp(为了便于理解,这里简称为“cp”)的电容之前,可以理解的是,在比较器i1/i2的比较过程中流入电容器cs的总电荷小于vth*cs。为了便于理解,在该公式中,“cs”表示电容器cs的电容。为了比较器i1/i2的正确操作,施加到电容器cs的最小电源电压可以基于比较器i1/i2的电压增益、输入-输出时间延迟、输入偏移电压和输出动态范围等各个方面来估计。为了达到实现adc规格所需的这些规格,比较器i1/i2中每个晶体管的漏极-源极电压需要保持高于根据下面所示的公式计算的所谓的饱和电压(vds_min)的电压。

81.vds_min=vgs

–

vt

82.因此,通过将每个晶体管m4、m2和m5的饱和电压vds_min相加,可以估计最小电源电压(vdd_min),如下所示。在该实施例中,假设这些晶体管的尺寸相同。

83.vdd_min=3*vds_min

84.电容器cp的电容需要大于“cs*vth/(vdd_common

–

vdd_min)”。根据这种计算,可以估计电容器cp的最小电容。这种最小电容可以降低成像装置100的功耗。此外,当比较器i1/i2放置在芯片中时,通过使用此类计算结果,可以最小化电容器cp共享的硅面积。硅面积最小可以有助于降低成像装置100成本。

85.在下文中,解释第二实施例。图4示出了比较器i1和i2。图3的附图标记对应于图2。比较器i1/i2包括晶体管m1至m10,其中,m1、m2、m5、m6、m7、m8、m9、m10都是pmos晶体管,而m3和m4是nmos晶体管,还包括端子1至5、电容器cg、cp和cs以及开关sw1。需要说明的是,晶体管m1至m10与图2不同。i3和i4是计数器电路。clk提供来自例如图1中所示的t/g 140或逻辑电路150的时钟信号。图5是比较器i1/i2进行操作时的时序图。在图4和图5中,假设像素信

号电平vpixel1高于像素信号电平vpixel2,斜坡参考电压vramp2低于斜坡参考电压vramp1,并且斜坡参考电压vramp2以预定的偏移电平(vth)精确地跟踪斜坡参考电压vramp1。斜坡参考电压vramp1以恒定速率从预定初始电平(vinit)斜降。晶体管m1至m4的操作类似于图2。

86.在图4中,每个像素信号/电压(为了便于理解,vpixel1和vpixel2)被提供到比较器i1(或i2)的负极输入端(端子4),该比较器i1(或i2)将像素信号vpixel1(或vpixel2)与斜坡参考电压(vramp1)进行比较。另一个斜坡参考电压(vramp2)可以通过采样/保持电路向晶体管m5的栅极端子提供电压,该晶体管m5充当比较器i1(或i2)的偏置电流源。

87.如上所述,“vth”可以设计成偏置电流源晶体管(m5)以使偏置电流流向比较器i1(或i2)的电压电平。因此,比较器i1(或i2)可以具有电压增益,该电压增益足够大以当斜坡参考电压vramp1达到与输入像素信号vpixel1(或vpixel2)相同的电压时,比较输入信号。

88.如上所述,计数器电路i3(或i4)输入从比较器i1(或i2)输出的信号。计数器电路i3(或i4)对通过clk端子提供的脉冲数量进行计数,而来自比较器i1(或i2)的输出信号保持在低电平。

89.在图5中,在时序t1处,脉冲φpw变为高电平,开关sw1相应地接通。公用电源vdd_common通过开关sw1提供给每个比较器(vdd1、vdd2)的本地电源线,并对存储电容器cp充电,以具有与vdd_common相同的电平。从时序t1至t2,对电容器cp充电。

90.在时序t2处,脉冲φpw变为低电平,开关sw1断开。每个比较器(i1、i2)的本地电源线(vdd1/vdd2,在图4中示为vdd)与公用电源线(vdd_common)断开连接。在时序t3处,已经处于高电平并施加到晶体管m8和m10的栅极端子上的脉冲φ1变为低电平。因此,比较器i1(或i2)中的晶体管m8和m10导通。电容器cg的一个端子通过晶体管m10连接到端子4。端子4接收输入像素信号vpixel1(或vpixel2),而电容器cg的另一个端子通过晶体管m8连接到源自公用电源vdd_common的vdd1。在时序t3之后,比较器i1(或i2)使用存储在电容器cp中的电力进行其操作。因此,例如,当比较器i1(或i2)进行比较功能时,可以将每个比较器的本地电源线彼此隔离,因此,可以减少由比较器(i1、i2)之间的电源线相关串扰引起的负面影响。

91.当已经处于高电平并施加到晶体管m8和m10的栅极端子上的脉冲φ1变为低电平,同时施加到晶体管m6的栅极端子的脉冲φres变为低电平时,晶体管m8、m10和m6导通。将连接到晶体管m6的电容器cs放电,施加到晶体管m5的源极端子的电压达到与vdd1/vdd2相同的电平,即与公用电源vdd_common相同的电平。

92.在时序t4处,脉冲φ1变为高电平,同时脉冲φ2变为低电平。在栅极节点上接收脉冲φ1的晶体管m8和m10截止,在栅极节点上接收脉冲φ2的晶体管m7和m9导通。因此,电容器cg的两个端子与端子4(通过晶体管m10)和公用电源vdd(通过晶体管m8)断开连接,并连接到端子2(通过晶体管m9)和晶体管m5的栅极端子(通过晶体管m7)。晶体管m5用作比较器i1(或i2)的电流源。斜坡参考电压vramp2施加到端子2,因此,电容器cg上的电荷被保存。电容器cg的两个端子之间的电压差仍然存在,晶体管m5的栅极端子上的电压通过“vinit

–

vth+vdd

–

vpixelx(x=1或2)”计算。

93.在时序t5处,斜坡参考电压vramp1达到与输入像素信号vpixel1相同的电压。施加到比较器i1的斜坡参考电压vramp1的电压降低为(vinit

–

vpixel1),斜坡参考电压vramp1

与vramp2之间的电压差为vth,因此,比较器i1中的晶体管m5的栅极端子达到如下所示的电压。

94.(vinit

–

vth+vdd1

–

vpixel1)

–

(vinit

–

vpixel1)=vdd1

–

vth

95.该公式表示晶体管m5可以使足够大以驱动比较器i1的偏置电流流过,并且比较器i1的输出信号变为低电平,并且有一定量的延迟时间响应其输入电压变化。在图5中,响应被示为“vout1”和“ibias1”。

96.在时序t6处,斜坡参考电压vramp1达到与输入像素信号vpixel2相同的电压。施加到比较器i2的斜坡参考电压vramp1的电压降低为(vinit

–

vpixel2),斜坡参考电压vramp1与vramp2之间的电压差为vth。施加到比较器i2中的晶体管m5的栅极端子的电压通过如下所示的公式计算。

97.(vinit

–

vth+vdd2

–

vpixel2)

–

(vinit

–

vpixel2)=vdd2

–

vth

98.这表示,如果晶体管m5可以使足够大以驱动比较器i2的偏置电流流过,则比较器i2的输出变为低电平,并且有一定量的延迟时间响应其输入电压变化。这些响应在图5中示为“vout2”和“ibias2”。

99.可以理解的是,成像装置通常具有沿着多个列和行布置的大量像素。图3和/或图5中包括的时序图可以应用于这些像素,并且例如,每列或每行上的像素可以根据图3或图5中描述的相同时序同时操作。逻辑电路150或t/g 140可以输出信号和/或脉冲,以便控制比较器i1/i2。

100.上述实施例可以具有各种优点。首先,例如,ss adc中的每个上述比较器的偏置电流取决于输入信号与施加到比较器的斜坡参考电压之间的电压差。比较器的偏置电流仅当斜坡参考电压电平接近输入信号电平时才开始流动。因此,动态偏置电路完全适合ss adc,此外,还降低了ss adc的功耗。

101.其次,例如,ss adc中的每个上述比较器的本地电源线通过开关(sw1)连接到公用电源(vdd_common)。这种分离的本地电源线分别具有存储电容器(cp)。

102.如上述实施例中所述,就在开始ad转换之前,这些开关(sw1)关闭,同时,对应于布置在一列上的像素的每个比较器的本地电源线与公用(传感器)电源线(vdd_common)断开连接。

103.每列比较器的电源电流由存储电容器(cp)提供,而不是由公用(传感器)电源线(vdd_common)提供。因此,负面影响,例如,在每个本地电源线(vdd1/vdd2)中产生的波动不会传播到其它本地电源线,因此,例如,可以消除“条带噪声”。

104.除了上述实施例之外,本技术可以具有其它方面。例如,第一方面是一种成像装置,所述成像装置包括比较器、像素和控制电路,其中,所述比较器包括开关、第一晶体管和第一电容器,其中,当所述开关接通时,所述第一电容器被充电,并且其中,在所述开关断开之后,所述比较器使用在所述第一电容器中充入的电力,比较从所述像素输入的像素信号与从所述控制电路输入的斜坡信号,并输出输出信号。

105.第二方面是根据上述方面所述的成像装置,其中,所述斜坡信号包括第一斜坡信号和第二斜坡信号。

106.第三方面是根据上述方面所述的成像装置,其中,所述斜坡信号包括所述第一斜坡信号与所述第二斜坡信号之间的预定电压差。

107.第四方面是根据上述方面所述的成像装置,其中,当所述第一斜坡信号达到与所述像素信号相同的电平时,所述比较器使所述输出信号反转。

108.第五方面是根据上述方面所述的成像装置,其中,当将与所述预定电压差具有相同电压电平的电压施加到所述第一晶体管的栅极端子时,所述第一晶体管使偏置电流流过以驱动所述比较器。

109.第六方面是根据上述方面所述的成像装置,其中,所述第一电容器的电容足够大以驱动所述比较器。

110.第七方面是根据上述方面所述的成像装置,其中,当所述第二斜坡信号达到与所述像素信号相同的电平时,所述比较器完成其比较操作。

111.第八方面是根据上述方面所述的成像装置,其中,当所述开关断开时,所述比较器与所述成像装置的公用电源断开连接。

112.第九方面是根据上述方面所述的成像装置,其中,所述第一斜坡信号和所述第二斜坡信号是斜升信号。

113.第十方面是根据上述方面所述的成像装置,其中,所述第一斜坡信号和所述第二斜坡信号是斜降信号。

114.第十一方面是一种用于包括比较器、像素和控制电路的成像装置的成像方法,所述成像方法包括:当所述比较器的开关接通时,对所述比较器的第一电容器充电;在所述开关断开后,使用在所述第一电容器中充入的电力比较从所述像素输入的像素信号与从所述控制电路输入的斜坡信号;输出输出信号。

115.第十二方面是根据上述方面所述的成像方法,其中,所述斜坡信号包括第一斜坡信号和第二斜坡信号。

116.第十三方面是根据上述方面所述的成像方法,其中,所述斜坡信号包括所述第一斜坡信号与所述第二斜坡信号之间的预定电压差。

117.第十四方面是根据上述方面所述的成像方法,其中,当所述第一斜坡信号达到与所述像素信号相同的电平时,所述比较器使所述输出信号反转。

118.第十五方面是根据上述方面所述的成像方法,其中,当将与所述预定电压差具有相同电压电平的电压施加到所述第一晶体管的栅极端子时,所述第一晶体管使偏置电流流过以驱动所述比较器。

119.第十六方面是根据上述方面所述的成像方法,其中,所述第一电容器的电容足够大以驱动所述比较器。

120.第十七方面是根据上述方面所述的成像方法,其中,当所述第二斜坡信号达到与所述像素信号相同的电平时,所述比较器完成其比较操作。

121.第十八方面是根据上述方面所述的成像方法,其中,当所述开关断开时,所述比较器与所述成像装置的公用电源断开连接。

122.第十九方面是根据上述方面所述的成像方法,其中,所述第一斜坡信号和所述第二斜坡信号是斜升信号。

123.第二十方面是根据上述方面所述的成像方法,其中,所述第一斜坡信号和所述第二斜坡信号是斜降信号。

124.上面公开的实施例是示例,应当理解,本发明和本技术的范围不受此类公开内容

的限制或约束。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1