DVI发送器、视频设备的制作方法

dvi发送器、视频设备

技术领域

1.本申请涉及图像处理技术领域,特别是涉及一种dvi发送器、视频设备。

背景技术:

2.dvi(digital visual interface),即数字视频接口,用于实现数字视频信号的高速无损传输。数字视频接口是一种国际开放的接口标准,在pc(personal computer,个人计算机)、dvd(digital versatile disc,数字通用光盘)、高清晰电视、高清晰投影仪等设备上有广泛的应用。在接口形式上有dvi-a、dvi-d和dvi-i三种不同类型。dvi-a只有模拟接口,dvi-d只有数字接口,dvi-i有数字和模拟接口。目前应用主要以dvi-d为主。

技术实现要素:

3.本申请主要解决的问题是提供一种dvi发送器、视频设备,能够降低dvi发送器的设计难度,降低设计成本。

4.本申请采用的一种技术方案是提供一种dvi发送器,dvi发送器基于fpga的逻辑资源实现,dvi发送器包括:编码电路,用于对输入的视频信号进行编码,并输出编码后的视频信号;串行电路,连接编码电路,用于将并行的编码后的视频信号转换为串行的视频信号;差分转换电路,连接串行电路,用于将串行的视频信号转换为差分信号并输出。

5.其中,编码电路包括多个编码器,用于对输入的视频信号中的多路基色信号分别进行编码;串行电路包括多个串行器,分别与多个编码器一一对应连接,将每个编码器输出的编码后的视频信号转换为串行的视频信号;差分转换电路包括多个差分转换器,分别与多个串行器一一对应连接,用于将每个串行器输出的串行的视频信号转换为差分信号并输出。

6.其中,多个编码器包括:第一通道编码器,其数据引脚输入第一路基色信号,其第一控制引脚输入行同步信号,其第二控制引脚输入场同步信号,其使能引脚输入使能信号;第二通道编码器,其数据引脚输入第二路基色信号,其第一控制引脚输入第一控制信号,其第二控制引脚输入第二控制信号,其使能引脚输入使能信号;第三通道编码器,其数据引脚输入第三路基色信号,其第一控制引脚输入第三控制信号,其第二控制引脚输入第四控制信号,其使能引脚输入使能信号。

7.其中,每个编码器包括:比特转换单元,连接数据引脚,用于将输入的视频信号由8bit信号转换为10bit信号;编码单元,连接第一控制引脚和第二控制引脚,用于将输入的信号转换为10bit信号;多路复用单元,连接比特转换单元、编码单元和使能引脚,用于选择输出比特转换单元或编码单元输出的10bit信号。

8.其中,比特转换单元包括:第一1bit计数器,连接数据引脚,用于根据输入的视频信号输出第一计数值;第一延时器,连接数据引脚,用于将输入的视频信号进行第一次延时处理;第一转换器,连接第一1bit计数器和第一延时器,用于利用第一计数值将第一次延时处理的视频信号由8bit信号转换为9bit信号;第二1bit计数器,连接第一转换器,用于对第

一转换器输入的视频信号根据输入的视频信号输出第二计数值;第二延时器,连接第一转换器,用于对第一转换器输入的视频信号进行第二次延时处理;第二转换器,连接第二1bit计数器和第二延时器,用于利用第二计数值将第二次延时处理的视频信号由9bit信号转换为10bit信号。

9.其中,每个串行器包括:数据输入引脚,连接对应的编码器,用于接收对应的编码器输出的编码后的视频信号;第一时钟引脚,用于接收第一时钟信号;第二时钟引脚,用于接收第二时钟信号;数据输出引脚,用于输出串行的视频信号;其中,串行的视频信号是根据第一时钟信号和第二时钟信号,对编码后的视频信号进行串行处理后得到的,第二时钟信号的频率是第一时钟信号的频率的5倍。

10.其中,dvi发送器还包括时钟电路,时钟电路与每个串行器连接,用于对输入的第一时钟信号进行倍频处理以得到第二时钟信号,并向串行器提供第一时钟信号和第二时钟信号。

11.其中,dvi发送器还包括外接电路,与差分转换电路连接,用于将差分转换电路输出的差分信息输出至外部设备。

12.其中,外接电路包括第一电阻、第二电阻、第一电容、第二电容;第一电容的第一端连接差分转换电路的正端,第一电容的第二端连接第一电阻的第一端,第一电阻的第二端连接信号源;第二电容的第一端连接差分转换电路的负端,第二电容的第二端连接第二电阻的第一端,第二电阻的第二端连接信号源。

13.本申请采用的另一种技术方案是提供一种视频设备,视频设备包括dvi发送器;其中,dvi发送器上述方案中提供的dvi发送器。

14.本申请的有益效果是:区别于现有技术的情况,本申请的一种dvi发送器,该dvi发送器基于fpga的逻辑资源实现,dvi发送器包括:编码电路,用于对输入的视频信号进行编码,并输出编码后的视频信号;串行电路,连接编码电路,用于将并行的编码后的视频信号转换为串行的视频信号;差分转换电路,连接串行电路,用于将串行的视频信号转换为差分信号并输出。通过上述方式,该发送器基于编码电路完成并行视频信号的编码,然后采用串行电路实现并行信号到串行信号的转换,并通过差分转换电路转换为差分信号输出,实现并行视频信号转换成差分信号的功能,降低dvi发送器的设计难度,降低设计成本。并且dvi发送器基于fpga的逻辑资源实现,由于fpga具有易实现、灵活性、可移植等特点,使得本申请的dvi发送器的设计更加灵活,降低了设计难度,进一步降低了设计成本。

附图说明

15.为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。其中:

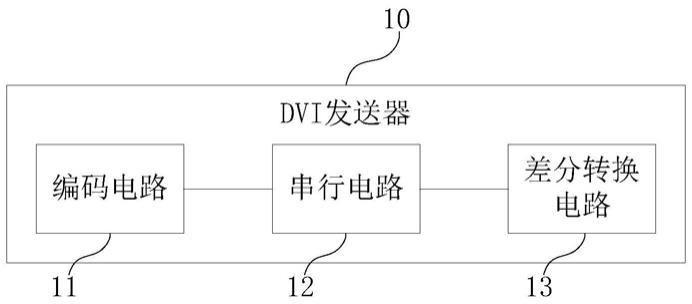

16.图1是本申请提供的dvi发送器第一实施例的结构示意图;

17.图2是本申请提供的dvi发送器第二实施例的结构示意图;

18.图3是本申请提供的编码电路的实施例的结构示意图;

19.图4是本申请提供的单个编码器一实施例的结构示意图;

20.图5是本申请提供的比特转换单元一实施例的结构示意图;

21.图6是本申请提供的串行器一实施例的结构示意图;

22.图7是本申请提供的串行器的时序示意图;

23.图8是本申请提供的dvi发送器第三实施例的结构示意图;

24.图9是本申请提供的外接电路的结构示意图;

25.图10是本申请提供的dvi发送器第四实施例的结构示意图;

26.图11是本申请提供的编码器一实施例的结构示意图;

27.图12是本申请提供的视频设备一实施例的结构示意图。

具体实施方式

28.下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。可以理解的是,此处所描述的具体实施例仅用于解释本申请,而非对本申请的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本申请相关的部分而非全部结构。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

29.在本文中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本申请的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

30.参阅图1,图1是本申请提供的dvi发送器第一实施例的结构示意图。dvi发送器10基于fpga的逻辑资源实现。dvi发送器10包括编码电路11、串行电路12和差分转换电路13。

31.其中,编码电路11连接串行电路12,串行电路12连接差分转换电路13。

32.编码电路11用于对输入的视频信号进行编码,并输出编码后的视频信号。串行电路12连接编码电路11,用于将并行的编码后的视频信号转换为串行的视频信号。差分转换电路13连接串行电路12,用于将串行的视频信号转换为差分信号并输出。

33.其中,本申请的fpga采用了逻辑单元阵列lca(logic cell array)。其内部包括可配置逻辑模块clb(configurable logic block)、输入输出模块iob(input output block)和内部连线(interconnect)三个部分。现场可编程门阵列(fpga)是可编程器件,与传统逻辑电路和门阵列(如pal,gal及cpld器件)相比,fpga具有不同的结构。fpga利用小型查找表(16

×

1ram)来实现组合逻辑,每个查找表连接到一个d触发器的输入端,触发器再来驱动其他逻辑电路或驱动i/o,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到i/o模块。fpga的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与i/o间的联接方式,并最终决定了fpga所能实现的功能,fpga允许无限次的编程。

34.在一些实施例中,编码电路11包括多个编码器,用于对输入的视频信号中的多路基色信号分别进行编码;如视频信号包括三路基色信号,三种基色信号对应红色、绿色、蓝色三种基色。三个编码器分别对应三路基色信号进行编码。以其中一个编码器对基色信号进行编码为例进行说明:

35.当8bit的基色信号输入编码器时,编码器先对8bit的基色信号进行延时处理及计数操作,然后进行转换处理将8bit的基色信号转换为9bit的基色信号;然后将9bit的基色信号再次进行延时处理及计数操作,并进行转换处理将9bit的基色信号转换为10bit的基色信号。并且在行同步信号和场同步信号以及使能信号的作用下输出10bit的基色信号。

36.在一些实施例中,串行电路12包括多个串行器,分别与编码电路11中的多个编码器一一对应连接,将每个编码器输出的编码后的视频信号转换为串行的视频信号。以其中一个串行器为例进行说明:串行器接收到与其对应连接的编码器输入的编码后的视频信号,这个视频信号为10bit。其中,编码后的视频信号按照低速时钟pclk节拍并行输入,并且串行器还会接收到对应于pclk时钟频率的5倍的高速时钟fclk,然后将10bit的视频信号在fclk时钟的上下沿依次串行输出。

37.在一些实施例中,差分转换电路13包括多个差分转换器,分别与串行电路12中的多个串行器一一对应连接,用于将每个串行器输出的串行的视频信号转换为差分信号并输出。

38.在一些实施例中,dvi发送器10还包括时钟电路,时钟电路与串行电路12连接,用于向串行电路提供第二时钟信号。串行电路12还用于基于第二时钟信号将编码后的视频信号转换为串行的视频信号并输出。

39.可选地,该时钟电路为锁相环电路,用于对输出的第一时钟信号进行锁相,确定第一时钟信号的相位,并根据确定的相位对第一时钟信号进行倍频处理,以得到第二时钟信号。可以理解地,由于本实施例中是对10bit的并行数据转化为串行数据,所以可以将第二时钟信号的频率确定为第一时钟的5倍,以便于将10bit的数据进行串行发送。

40.区别于现有技术,本申请提供的一种dvi发送器,该发送器基于编码电路完成并行视频信号的编码,然后采用串行电路实现并行信号到串行信号的转换,并通过差分转换电路转换为差分信号输出,实现并行视频信号转换成差分信号的功能。通过上述方式,本实施例中的dvi发送器基于fpga的逻辑资源实现,由于fpga具有易实现、灵活性、可移植等特点,使得本申请的dvi发送器的设计更加灵活,降低了设计难度,进一步降低了设计成本。

41.参阅图2,图2是本申请提供的dvi发送器第二实施例的结构示意图。dvi发送器20基于fpga的逻辑资源实现。dvi发送器20包括编码电路21、串行电路22、差分转换电路23。

42.其中,编码电路21连接串行电路22,串行电路22连接差分转换电路23。

43.编码电路21包括多个编码器211用于对输入的视频信号中的多路基色信号分别进行编码。如视频信号包括三路基色信号,三种基色信号对应红色、绿色、蓝色三种基色。三个编码器分别对应三路基色信号进行编码。以其中一个编码器对基色信号进行编码为例进行说明:

44.当8bit的基色信号输入编码器时,编码器先对8bit的基色信号进行延时处理及计数操作,然后进行转换处理将8bit的基色信号转换为9bit的基色信号;然后将9bit的基色信号再次进行延时处理及计数操作,并进行转换处理将9bit的基色信号转换为10bit的基色信号。并且在行同步信号和场同步信号以及使能信号的作用下输出10bit的基色信号。

45.串行电路22包括多个串行器221,分别与多个编码器211一一对应连接,将每个编码器输出的编码后的视频信号转换为串行的视频信号。以其中一个串行器为例进行说明:串行器接收到与其对应连接的编码器输入的编码后的视频信号,这个视频信号为10bit。其

中,编码后的视频信号按照低速时钟pclk节拍并行输入,并且串行器还会接收到对应于pclk时钟频率的5倍的高速时钟fclk,然后将10bit的视频信号在fclk时钟的上下沿依次串行输出。

46.差分转换电路23包括多个差分转换器231,分别与多个串行器221一一对应连接,用于将每个串行器输出的串行的视频信号转换为差分信号并输出。

47.参阅图3,图3是本申请提供的编码电路的实施例的结构示意图。其中,编码电路21包括第一通道编码器211a、第二通道编码器211b和第三通道编码器211c。

48.第一通道编码器211a的数据引脚输入第一路基色信号(blu[7:0]),其第一控制引脚输入行同步信号(hsync),其第二控制引脚输入场同步信号(vsync),其使能引脚输入使能信号(de)。

[0049]

第二通道编码器211b的数据引脚输入第二路基色信号(grn[7:0]),其第一控制引脚输入第一控制信号(ctl0),其第二控制引脚输入第二控制信号(ctl1),其使能引脚输入使能信号(de)。其中,第一控制信号、第二控制信号为0。

[0050]

第三通道编码器211c的数据引脚输入第三路基色信号(red[7:0]),其第一控制引脚输入第三控制信号(ctl2),其第二控制引脚输入第四控制信号(ctl3),其使能引脚输入使能信号(de)。其中,第三控制信号、第四控制信号为0。

[0051]

上述第一通道编码器211a、第二通道编码器211b、第三通道编码器211c的结构相同,在实际应用中,可以按照以下方式设置:

[0052]

第一通道编码器211a的数据引脚输入第一路基色信号,其第一控制引脚输入第一控制信号,其第二控制引脚输入第二控制信号,其使能引脚输入使能信号。其中,第一控制信号、第二控制信号为0。

[0053]

第二通道编码器211b的数据引脚输入第二路基色信号,其第一控制引脚输入行同步信号,其第二控制引脚输入场同步信号,其使能引脚输入使能信号。

[0054]

第三通道编码器211c的数据引脚输入第三路基色信号,其第一控制引脚输入第三控制信号,其第二控制引脚输入第四控制信号,其使能引脚输入使能信号。其中,第三控制信号、第四控制信号为0。

[0055]

可以理解,由于上述第一通道编码器211a、第二通道编码器211b和第三通道编码器211c的结构相同,所以三路基色信号可随意分配给第一通道编码器211a、第二通道编码器211b和第三通道编码器211c,且其中一个编码器的第一控制引脚输入行同步信号,其第二控制引脚输入场同步信号即可。其他两个编码器的第一控制引脚、第二控制引脚输入为0的控制信号。

[0056]

参阅图4,图4是本申请提供的单个编码器一实施例的结构示意图。编码器211包括比特转换单元2111、编码单元2112、多路复用单元2113。

[0057]

其中,比特转换单元2111连接数据引脚data,用于将输入的视频信号由8bit信号转换为10bit信号。编码单元2112连接第一控制引脚ctl0和第二控制引脚ctl1,用于将输入的信号转换为10bit信号。多路复用单元2113连接比特转换单元2111、编码单元2112和使能引脚de,用于选择输出比特转换单元2111或编码单元2112输出的10bit信号。

[0058]

参阅图5,图5是本申请提供的比特转换单元一实施例的结构示意图。比特转换单元2111包括第一1bit计数器21111、第一延时器21112、第一转换器21113、第二1bit计数器

21114、第二延时器21115和第二转换器21116。

[0059]

其中,第一1bit计数器21111连接数据引脚data,用于根据输入的视频信号输出第一计数值。第一延时器21112连接数据引脚data,用于将输入的视频信号进行第一次延时处理;第一转换器21113连接第一1bit计数器21111和第一延时器21112,用于利用第一计数值将第一次延时处理的视频信号由8bit信号转换为9bit信号。第二1bit计数器21114连接第一转换器21113,用于对第一转换器21113输入的视频信号根据输入的视频信号输出第二计数值。第二延时器21115连接第一转换器21113,用于对第一转换器21113输入的视频信号进行第二次延时处理。第二转换器21116连接第二1bit计数器21114和第二延时器21115,用于利用第二计数值将第二次延时处理的视频信号由9bit信号转换为10bit信号,然后通过输出引脚输出至多路复用单元。

[0060]

参阅图6,图6是本申请提供的串行器一实施例的结构示意图。串行器包括数据输入引脚data、第一时钟引脚pclk、第二时钟引脚fclk和数据输出引脚q。

[0061]

数据输入引脚data连接对应的编码器,用于接收对应的编码器输出的编码后的视频信号。第一时钟引脚pclk用于接收第一时钟信号。第二时钟引脚fclk,用于接收第二时钟信号。数据输出引脚q用于输出串行的视频信号。其中,串行的视频信号是根据第一时钟信号和第二时钟信号,对编码后的视频信号进行串行处理后得到的,第二时钟信号的频率是第一时钟信号的频率的5倍。

[0062]

具体地,参阅图7,图7是本申请提供的串行器的时序示意图。其中,pclk表示第一时钟引脚pclk接收的第一时钟信号、data表示数据输入引脚data接收的视频信号、fclk表示第二时钟引脚fclk接收的第二时钟信号、q表示数据输出引脚输出的串行数据。当第一时钟引脚pclk接收的第一时钟信号时,数据输入引脚data接收到视频信号0100100111,串行器按照第一时钟信号的第一时间周期将视频信号0100100111输入,然后在第二时间周期,按照接收的第二时钟信号将视频信号0100100111串行输出。在第二时间周期时,数据输入引脚data接收到视频信号1100111010,串行器按照第一时钟信号的第二时间周期将视频信号1100111010输入。然后第三时间周期按照接收的第二时钟信号将视频信号0100100111串行输出。

[0063]

其中,第二时钟信号的频率是第一时钟信号的频率的5倍。

[0064]

在一些实施例中,dvi发送器还包括时钟电路,时钟电路与每个串行器连接,用于对输入的第一时钟信号进行倍频处理以得到第二时钟信号,并向串行器提供第一时钟信号和第二时钟信号。

[0065]

通过上述方式,本实施例中的dvi发送器基于fpga的逻辑资源实现,由于fpga具有易实现、灵活性、可移植等特点,使得本申请的dvi发送器的设计更加灵活,降低了设计难度,进一步降低了设计成本。

[0066]

参阅图8,图8是本申请提供的dvi发送器第三实施例的结构示意图。dvi发送器80基于fpga的逻辑资源实现。dvi发送器80包括编码电路81、串行电路82、差分转换电路83和外接电路84。

[0067]

编码电路81、串行电路82、差分转换电路83与上述实施例的技术方案相似或相同,这里不做赘述。外接电路84连接差分转换电路83,用于将差分转换电路83输出的差分信息输出至外部设备。

[0068]

参阅图9,对外接电路84进行说明:

[0069]

外接电路84包括第一电阻r1、第二电阻r2、第一电容c1、第二电容c2;

[0070]

第一电容c1的第一端连接差分转换电路83的正端,第一电容c1的第二端连接第一电阻r1的第一端,第一电阻r1的第二端连接信号源vcc。第二电容c2的第一端连接差分转换电路83的负端,第二电容c2的第二端连接第二电阻r2的第一端,第二电阻r2的第二端连接信号源vcc。其中,vcc的电压为3.3v,第一电阻r1和第二电阻r2的电阻值为50ω,第一电容c1和第二电容c2的电容量为100nf。通过这种方式,差分转换电路83的正端和负端分别串联第一电容c1和第二电容c2,并且第一电容c1并联第一电阻r1、第二电容c2第二电阻r2,使用vcc信号源上拉到3.3v,从而满足差分转换电路输出电压标准。

[0071]

参阅图10,图10是本申请提供的dvi发送器第四实施例的结构示意图。dvi发送器90包括编码电路91、串行电路92、差分转换电路93和时钟电路94。其中,编码电路91包括多个编码器encoder,用于对输入的视频信号中的多路基色信号分别进行编码。串行电路92包括多个串行器serializer,分别与多个编码器encoder一一对应连接,将每个编码器encoder输出的编码后的视频信号转换为串行的视频信号。差分转换电路93包括多个差分转换器lvde_obuf,分别与多个串行器serializer一一对应连接,用于将每个串行器serializer输出的串行的视频信号转换为差分信号并输出。时钟电路94与串行电路92连接,提供两种时钟信号。第一时钟信号为像素时钟信号,第二时钟信号为像素时钟信号的频率为像素时钟信号频率的5倍。时钟信号也会被串行器serializer进行串行处理,得到串行时钟信号,并输入至差分转换器lvde_obuf,然后在对应的信号通道输出。在一些实施例中,通过配置时钟电路94中的锁相环pll(phase locked loop)的时钟信号,能够满足不同分辨率的转换需求。

[0072]

最后,差分转换器lvde_obuf在四个信号通道输出信息,四个通道分别为channel0、channel1、channel2和channel clock。

[0073]

具体地,参阅图11,图11是本申请提供的编码器一实施例的结构示意图。编码器包括第一1bit计数器bit1 counter、第一延时器delay、第一转换器change 8bit to 9bit、第二1bit计数器bit1 counter、第二延时器delay、第二转换器change 9bit to 10bit、编码单元co_co encode和多路复用单元data mux。

[0074]

其中,第一1bit计数器bit1 counter连接数据引脚,用于根据输入的视频信号d[7:0]输出第一计数值。第一延时器delay连接数据引脚,用于将输入的视频信号d[7:0]进行第一次延时处理;第一转换器change8bit to 9bit连接第一1bit计数器和第一延时器,用于利用第一计数值将第一次延时处理的视频信号d[7:0]由8bit信号转换为9bit信号,得到视频信号d[8:0]。第二1bit计数器bit1 counter连接第一转换器change 8bit to 9bit,用于对第一转换器change 8bit to 9bit输入的视频信号d[8:0]进行处理,输出第二计数值。第二延时器delay连接第一转换器change 8bit to 9bit,用于对第一转换器输入的视频信号d[8:0]进行第二次延时处理;第二转换器change 9bit to 10bit连接第二1bit计数器bit1 counter和第二延时器delay,用于利用第二计数值将第二次延时处理的视频信号d[8:0]由9bit信号转换为10bit信号,得到视频信号d[9:0]。编码单元co_co encode连接第一控制引脚和第二控制引脚,用于将输入的信号转换为10bit信号c[9:0];多路复用单元data mux连接第二转换器change 9bit to10bit、编码单元co_co encode和使能引脚de,用

于选择输出第二转换器change 9bit to 10bit或编码单元co_co encode输出的10bit信号即code_data[9:0]。

[0075]

通过上述方式,本实施例中的dvi发送器基于fpga的逻辑资源实现,由于fpga具有易实现、灵活性、可移植等特点,使得本申请的dvi发送器的设计更加灵活,降低了设计难度,进一步降低了设计成本。并且本实施例中的dvi发送器提供给基于fpga平台进行视频接口设计用户进行产品研制,能够降低用户开发难度,提高产品开发速度。

[0076]

参阅图12,图12是本申请提供的视频设备一实施例的结构示意图。视频设备100包括dvi发送器101。其中,dvi发送器101如上述任一实施例中的dvi发送器。

[0077]

在一些实施例中,该视频设备100通过dvi发送器101对并行的8bit的视频信号进行处理,得到10bit串行的视频信号,然后将10bit串行的视频信号转换为差分信号进行输出。

[0078]

通过上述方式,本实施例中的视频设备能够器基于fpga的逻辑资源实现,由于fpga具有易实现、灵活性、可移植等特点,使得本申请的dvi发送器的设计更加灵活,降低了设计难度,进一步降低了设计成本。并且本实施例中的视频设备提供给基于fpga平台进行视频接口设计用户进行产品研制,能够降低用户开发难度,提高产品开发速度。

[0079]

以上所述仅为本申请的实施方式,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1