一种基于FPGA平台的精确时间同步方法与流程

一种基于fpga平台的精确时间同步方法

技术领域

1.本发明属于通信技术领域,具体涉及一种基于fpga平台的精确时间同步方法。

背景技术:

2.当基于各种通信协议,信息在主系统和从系统之间传输时,由于信息延迟,主从系统之间会存在系统间的时间偏差。现如今,时间同步技术已运用到各行各业中,尤其在国防、金融、通信等领域至关重要,随着时代的发展,各行各业的市场竞争愈显激烈,而在时间同步技术的竞争中,精确和成本较低成为决胜的两大竞争力。

3.精确时间同步协议(ptp)最早被应用于自动控制领域,理论上,它可以达到亚微秒级的同步精度,这已经极大领先早期的网络时间同步协议了。在2008年发布了ptpv2协议,它在原有ptp协议的基础上新增了支持测量节点驻留时间和链路不对称等,在一些支持ptpv2的硬件转发节点上,更是达到了几十纳秒的同步精度,ptp协议的高精度性能使得其在很多行业都能迅速发展。

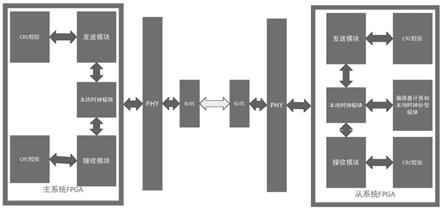

4.ptp协议中规定ptp报文的主要封装形式有三种,分别是:ptp over udp over ipv4、ptp over udpover ipv6和ptp over ieee802.3/ethernet。当下,ptp协议的实现一般采用纯软件方案或软硬件相结合的方案,这两种方法各有侧重点,纯软件方案成本较低但精度也较低,软硬件结合方案成本较高但精度也较高,它们的本质区别只在于时间戳的获取方式差异,但综合来说这两种方案的实现都需要复杂、冗余的系统结构和高昂的成本。

5.发明目的

6.本发明的目的是为了解决现有技术中所面临的难题,提供一种基于fpga平台的精确时间系统同步方法,基于现有ptpv2协议,但摆脱了现有实现ptp协议技术系统复杂、成本太高的窘境,通过一个简单的基于fpga平台的系统,成本较低地实现了主从系统之间的精确时间系统同步。鉴于现有技术的缺点,本发明采用纯硬件的方案,更适用于一些主从系统关系确定的应用场景,比如多通道远程同步触发数据采集、高精度工业流水线同步操作等。

技术实现要素:

7.根据本发明的一个方面,提供了一种基于fpga平台的精确时间同步系统,该信息同步传输系统基于ieee802.3/ethernet的ptp协议,包括主系统fpga、从系统fpga,其中,主系统fpga依次双向连接主系统物理层芯片phy、主系统rj45接口;从系统fpga依次双向连接从系统物理层芯片phy、从系统rj45接口;所述主系统rj45接口与从系统rj45接口相互连接双向交互数据;所述主系统fpga包括主系统发送模块、主系统接收模块、主系统本地时钟模块、第一crc校验模块、第二crc校验模块;其中,所述主系统发送模块分别与第一crc校验模块和主系统本地时钟模块连接,所述主系统接收模块分别与第二crc校验模块和主系统本地时钟模块连接;

8.所述从系统fpga包括从系统发送模块、从系统接收模块、从系统本地时钟模块、第三crc校验模块、第四crc校验模块以及偏移量计算和本地时钟补偿模块;所述从系统发送

模块分别与第三crc校验模块和从系统本地时钟模块连接,所述从系统接收模块分别与第四crc校验模块和从系统本地时钟模块连接;所述从系统本地时钟模块与所述偏移量计算和本地时钟补偿模块连接。

9.优选地,所述主系统发送模块、从系统发送模块通过发送状态机发送数据,覆盖主从双系统逻辑处理;所述发送状态机的执行流程包括发送7个字节的前导码和1个字节的帧开始定界符、发送目的地址和源地址、发送类型值16’h88f7、发送ptp报文头、发送ptp报文数据、校验报文头和报文数据以生成校验码以及发送校验码。

10.更优选地,所述主系统发送模块周期性产生同步脉冲开启同步算法,依次发送sync报文和follow_up报文,收到delay_req报文后开始发送delay_resp报文;若在一定时间内未接受到delay_req报文,则同步周期内发生错误,发送状态机返回至idle,等待下一次同步开始;所述从系统发送模块等待主系统发送的follow_up报文,接收到该报文后开始发送delay_req报文。

11.优选地,所述主系统接收模块、从系统接收模块通过接收状态机接收数据,覆盖主从双系统逻辑处理;所述接收状态机的执行流程包括接收7个字节的前导码和1个字节的帧开始定界符、接收目的地址和源地址、接收类型值16’h88f7、接收ptp报文头、接收ptp报文数据、接收校验码以及校验。

12.更优选地,所述主系统接收模块等待接收delay_req报文,在所述接收状态机的任何一个状态接收数据错误或未接受到数据均返回idle;所述从系统接收模块依次接收到sync、follow_up以及delay_resp报文,在所述接收状态机的任何一个状态接受数据错误或未接受到数据均返回idle。

13.优选地,所述主系统本地时钟模块、从系统本地时钟模块负责系统的输入提供和本地系统的计时。

14.优选地,所述第一crc校验模块、第二crc校验模块、第三crc校验模块、第四crc校验模块为相同型号,在发送报文时,以报文头和报文数据为校验对象生成32位crc校验码;在接收报文时,以接收到的报文头、报文数据和32位校验码为校验对象,校验帧数据传输是否正常。

15.优选地,所述偏移量计算和本地时钟补偿模块用于实现系统的自我补偿,本地时钟补偿依照偏移量去调整本地时钟模块中的计时周期。

16.根据本发明的另一个方面,提供一种应用上述信息同步传输系统进行精确时间补偿的方法,包括以下步骤:

17.步骤1、主系统fpga发送sync报文给从系统fpga,并记录sync报文离开主系统的时间戳t0;从系统fpga接收到来自主系统的sync报文,并记录sync报文到达从系统fpga的时间戳t1;

18.步骤2、主系统fpga发送携带时间戳t0的follow_up报文给从系统fpga,从系统fpga收到follow_up报文并获取了时间戳t0;

19.步骤3、从系统fpga发送delay_req报文给主系统fpga,并记录delay_req报文离开从系统fpga的时间戳t2;主系统fpga收到来自从系统fpga的delay_req报文,并记录delay_req报文到达主系统fpga的时间戳t3;

20.步骤4、主系统fpga发送携带时间戳t3的delay_resp报文给从系统fpga,从系统

fpga收到该报文并获取了时间戳t3;

21.t0、t1、t2以及t3满足如式(1)、式(2)的关系:

22.t1

‑

t0=delay+offset

ꢀꢀꢀꢀꢀ

(1),

23.t3

–

t2=delay

–

offset

ꢀꢀꢀꢀꢀ

(2),

24.其中,delay表示主从系统之间的时间偏移量,offset表示时间补偿量;

25.从系统fpga的偏移量计算和本地时钟补偿模块根据式(1)、(2)计算出从系统fpga相对主系统fpga的时间偏移量,通过本地时钟补偿依照偏移量去调整从系统本地时钟模块中的计时周期。

附图说明

26.图1为本发明所述基于fpga平台的信息同步传输系统的框架图。

27.图2是本发明传输系统的发送模块的发送状态机工作流程图。

28.图3是本发明传输系统的接收模块的接收状态机工作流程图。

具体实施方式

29.以下结合附图,详细阐述本发明的具体实施方式。需要指出的是,具体实施方式仅用于示例性的描述本发明,不应被视作对本发明的保护范围的限定,本领域技术人员应当明白,不脱离本发明主旨的变体和改动均落入本发明的保护范围。

30.ptp协议中规定ptp报文的主要封装形式有三种,分别是:ptp over udp over ipv4、ptp over udpover ipv6和ptp over ieee802.3/ethernet。本实施方式选用ptp over ieee802.3/ethernet,其余两种方式与ieee802.3/ethernet方式类似。

31.ptp协议主要通过sync、follow_up、delay_req和delay_resp四种报文传递来实现主从系统同步的,通过多组信息交互,使得从系统计算出主从系统间的时间偏差并进行合理的自我时间补偿。自我时间补偿具体步骤通常如下:

32.(1)主系统发送sync报文给从系统,并记录sync报文离开主系统的时间戳t0。从系统接收到来自主系统的sync报文,并记录sync报文到达从系统的时间戳t1。

33.(2)主系统发送携带时间戳t0的follow_up报文给从系统,从系统收到follow_up报文并获取了时间戳t0。

34.(3)从系统发送delay_req报文给主系统,并记录delay_req报文离开从系统的时间戳t2;主系统收到来自从系统的delay_req报文,并记录delay_req报文到达主系统的时间戳t3。

35.(4)主系统发送携带时间戳t3的delay_resp报文给从系统,从系统收到该报文并获取了时间戳t3。

36.通过上述信息交互,从系统获得了t0、t1、t2以及t3四个时间戳,从而得到以下公式:

37.t1

‑

t0=delay+offset

ꢀꢀꢀꢀꢀ

(1),

38.t3

–

t2=delay

–

offset

ꢀꢀꢀꢀꢀ

(2),

39.从系统根据公式(1)、(2)计算出从系统相对主系统的时间偏移量,并进行自我时间补偿达到同步效果。

40.图1为本发明所述基于fpga平台的精确时间同步系统的框架图。由图可知,本发明的信息同步传输系统包括主系统fpga、从系统fpga,其中,主系统fpga依次双向连接主系统物理层芯片phy、主系统rj45接口;从系统fpga依次双向连接从系统物理层芯片phy、从系统rj45接口;所述主系统rj45接口与从系统rj45接口相互连接双向交互数据;所述主系统fpga包括主系统发送模块、主系统接收模块、主系统本地时钟模块、第一crc校验模块、第二crc校验模块;所述主系统发送模块分别与第一crc校验模块和主系统本地时钟模块连接,所述主系统接收模块分别与第二crc校验模块和主系统本地时钟模块连接。

41.所述从系统fpga包括从系统发送模块、从系统接收模块、从系统本地时钟模块、第三crc校验模块、第四crc校验模块以及偏移量计算和本地时钟补偿模块;所述从系统发送模块分别与第三crc校验模块和从系统本地时钟模块连接,所述从系统接收模块分别与第四crc校验模块和从系统本地时钟模块连接;所述从系统本地时钟模块与所述偏移量计算和本地时钟补偿模块连接。

42.图2是本发明同步系统的发送模块的发送状态机工作流程图。所述主系统发送模块、从系统发送模块通过发送状态机发送数据,覆盖主从双系统逻辑处理;所述发送状态机的执行流程包括发送7个字节的前导码和1个字节的帧开始定界符、发送目的地址和源地址、发送类型值16’h88f7、发送ptp报文头、发送ptp报文数据、校验报文头和报文数据以生成校验码以及发送校验码。工作时,主系统发送模块周期性产生同步脉冲开启同步算法,依次发送sync报文follow_up报文,收到delay_req报文后开始发送delay_resp报文;若在一定时间内未接受到delay_req报文,则同步周期内发生错误,发送状态机返回至idle,等待下一次同步开始;所述从系统发送模块等待主系统发送的follow_up报文,接收到该报文后开始发送delay_req报文。

43.图3是本发明同步系统的接收模块的接收状态机工作流程图。主系统接收模块、从系统接收模块通过接收状态机接收数据,覆盖主从双系统逻辑处理;所述接收状态机的执行流程包括接收7个字节的前导码和1个字节的帧开始定界符、接收目的地址和源地址、接收类型值16’h88f7、接收ptp报文头、接收ptp报文数据、接收校验码以及校验。所述主系统接收模块等待接收delay_req报文,在所述接收状态机的任何一个状态接收数据错误或未接受到数据均返回idle;所述从系统接收模块依次接收到sync、follow_up以及delay_resp报文,在所述接收状态机的任何一个状态接受数据错误或未接受到数据均返回idle。

44.主系统本地时钟模块、从系统本地时钟模块负责系统的输入提供和本地系统的计时。

45.第一crc校验模块、第二crc校验模块、第三crc校验模块、第四crc校验模块为相同型号,在发送报文时,以报文头和报文数据为校验对象生成32位crc校验码;在接收报文时,以接收到的报文头、报文数据和32位校验码为校验对象,校验帧数据传输是否正常。

46.偏移量计算和本地时钟补偿模块只有在从系统中才会工作,主系统中的偏移量计算和本地时钟补偿模块是永远不会工作的。从系统根据公式(1)、(2)计算出从系统相对主系统的时间偏移量,本地时钟补偿依照偏移量去调整本地时钟模块中的计时周期。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1