一种基于FPGA的拼接屏控制器的制作方法

一种基于fpga的拼接屏控制器

技术领域

1.本发明涉及拼接屏技术领域,具体为一种基于fpga的拼接屏控制器。

背景技术:

2.拼接控制器主要功能是将一个完整的图像信号划分成n块后分配给n个 视频显示单元,视频显示单元可以是液晶拼接屏、等离子拼接屏、背投拼接 屏;实现用多个视频显示单元组成一个组合屏幕动态图像显示屏,并可以支 持多种视频设备的同时接入,拼接控制器广泛应用于展览、会议、电视卖场、 政府机关、电力水利、电信、公安、军队、铁路、交通、矿业、能源、钢铁、 企业等的展示中心、监控中心、调度中心、指挥中心、会议室、展示厅大屏 幕显示系统等离子、液晶电视等大屏幕显示设备,目前已有的拼接屏显示方 案主要是将多块显示器沿所显示图像的水平和竖直方向来进行阵列摆放,如 图1所示,此方案无法实现显示器任意角度的如图2所示的复杂摆放方式, 而能任意角度摆放的复杂拼接阵列给人的视觉效果更好,更适用于需要拼接 显示的广告或创意展示场景。

技术实现要素:

3.针对现有技术的不足,本发明提供了一种基于fpga的拼接屏控制器,具 备旋转操作实时性好,输入图像的有效像素数据直接先旋转后存入ddr3,不 需要将整帧保存完后再进行旋转然后再分割成各个拼接屏的显示区域,减小 ddr3读写的开销等的优点,解决了上述背景技术中提出的问题。

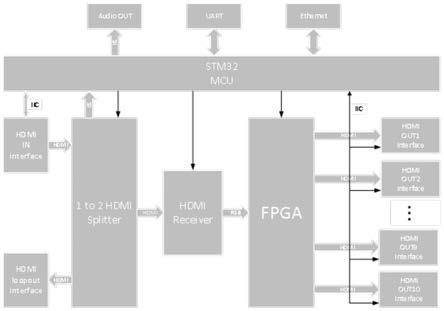

4.本发明提供如下技术方案:一种基于fpga的拼接屏控制器,包括1 to 2 hdmi splitter、hdmi receiver、fpga和stm32 mcu,所述1 to 2hdmi splitter 把进入到该设备内的视频源的hdmi信号分为两路,一路经hdmi receiver转 为rgb信号给到fpga,另一路直接从hdmi loopout接口输出;所述fpga处 理接收到的视频信号并把处理后的视频信号输出,所述fpga包括图像接收及 旋转模块、数据r/w模块、hdmi显示模块、时钟模块和ddr3 ip核,所述hdmireceiver输出的rgb888数据通过fpga的io口输入,经图像接收及旋转模块 处理后给到数据r/w模块,r/w模块将数据通过ip核存入ddr3中作为帧缓存, 同时将ddr3中已经缓存的数据读出给到hdmi显示模块,hdmi显示模块将rgb 数据编码串化成tmds信号通过hdmi接口输出;所述stm32 mcu用来作为hdmi 的edid信息管理和与上位机进行通信,上位机将拼接屏的参数信息发送给 mcu,mcu将这些参数信息打包格式化后发送给fpga进行初始化,所述hdmisplitter和hdmi receiver的初始化配置也交由mcu控制。

5.优选的,视频源的hdmi信号通过hdmi输入接口进入设备,从hdmi loopout 接口输出的信号作为输入信号检测口或者多个模块串联扩展输出通道数。

6.优选的,所述fpga收到视频信号后经内部旋转和显示模块处理后可分成 最多10路输出。

7.优选的,所述图像接收及旋转模块负责将接收到的像素数据进行坐标变 换后存入ram中缓存,然后传给r/w模块写入ddr中。

8.优选的,所述数据r/w模块产生读写ddr3 ip核的用户时序,实现与ddr3 ip核的数据及信息交互,且由于hdmi的时钟和ddr3的时钟不一样,r/w模 块内例化多个fifo ip核作为数据异步处理的缓存。

9.优选的,所述hdmi显示模块内部例化10个独立的hdmi驱动模块,对应 10路hdmi输出,所述时钟模块负责给各个模块提供时钟。

10.优选的,所述拼接屏的参数信息包含旋转角度和各个显示屏的显示坐标, 上位机将拼接屏的参数信息通过ethernet或者串口发送给mcu。

11.与现有技术对比,本发明具备以下有益效果:

12.1、该基于fpga的拼接屏控制器,将拼接屏的旋转阵列拼接摆放转换为 输入图像旋转,拼接屏显示区域相对旋转后的图像只需左右和上下移位即可 实现,本方案的视频延时只是由于ddr3的乒乓操作只需1帧的延时。

13.2、该基于fpga的拼接屏控制器,旋转操作实时性好,输入图像的有效 像素数据直接先旋转后存入ddr3,不需要将整帧保存完后再进行旋转然后再 分割成各个拼接屏的显示区域,减小ddr3读写的开销。

附图说明

14.图1为目前已有拼接屏摆放方式示意图;

15.图2为显示屏复杂摆放方式示意图;

16.图3为本发明硬件框图示意图;

17.图4为本发明结构fpga的程序框图示意图;

18.图5为图像像素数据示意图;

19.图6为旋转后的图像像素数据示意图;

20.图7为本发明结构图像接收及旋转模块程序流程图;

21.图8为本发明结构图像旋转0至90度示意图;图9为本发明结构图像旋转90至180度示意图;图10为本发明结构图像旋转180至270度示意图;图11为本发明结构图像旋转270至360度示意图。

具体实施方式

22.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行 清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而 不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做 出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

23.请参阅图3和4,一种基于fpga的拼接屏控制器,包括1 to 2hdmisplitter、hdmi receiver、fpga和stm32 mcu,1 to 2hdmi splitter把进 入到该设备内的视频源的hdmi信号分为两路,一路经hdmi receiver转为rgb 信号给到fpga,另一路直接从hdmi loopout接口输出;fpga处理接收到的 视频信号并把处理后的视频信号输出,fpga包括图像接收及旋转模块、数据 r/w模块、hdmi显示模块、时钟模块和ddr3 ip核,hdmi receiver输出的 rgb888数据通过fpga的io口输入,经图像接收及旋转模块处理后给到数据 r/w模块,r/w模

块将数据通过ip核存入ddr3中作为帧缓存,同时将ddr3 中已经缓存的数据读出给到hdmi显示模块,hdmi显示模块将rgb数据编码串 化成tmds信号通过hdmi接口输出;stm32 mcu用来作为hdmi的edid信息管 理和与上位机进行通信,上位机将拼接屏的参数信息发送给mcu,mcu将这些 参数信息打包格式化后发送给fpga进行初始化,hdmi splitter和hdmireceiver的初始化配置也交由mcu控制,将拼接屏的旋转阵列拼接摆放转换 为输入图像旋转,拼接屏显示区域相对旋转后的图像只需左右和上下移位即 可实现,本方案的旋转操作实时性好,输入图像的有效像素数据直接先旋转 后存入ddr3,不需要将整帧保存完后再进行旋转然后再分割成各个拼接屏的 显示区域,减小ddr3读写的开销,本方案的视频延时只是由于ddr3的乒乓 操作只需1帧的延时。

24.视频源的hdmi信号通过hdmi输入接口进入设备,从hdmi loopout接口 输出的信号作为输入信号检测口或者多个模块串联扩展输出通道数。

25.fpga收到视频信号后经内部旋转和显示模块处理后可分成最多10路输 出。

26.图像接收及旋转模块负责将接收到的像素数据进行坐标变换后存入ram 中缓存,然后传给r/w模块写入ddr中,时钟模块负责给各个模块提供时钟。

27.数据r/w模块产生读写ddr3 ip核的用户时序,实现与ddr3 ip核的数 据及信息交互,且由于hdmi的时钟和ddr3的时钟不一样,r/w模块内例化多 个fifo ip核作为数据异步处理的缓存。

28.hdmi显示模块内部例化10个独立的hdmi驱动模块,对应10路hdmi输 出。

29.拼接屏的参数信息包含旋转角度和各个显示屏的显示坐标,上位机将拼 接屏的参数信息通过ethernet或者串口发送给mcu。

30.图像接收及旋转模块的实现的原理:请参阅图5,以选用xilinx fpga为 例,mig ip核配置为位宽24bit,为了降低用户端时钟频率,一般将phy端 与用户端时钟频率比值配置为4:1,其突发传输长度为8,每个用户周期需要 将8个连续数据即192bit数据一起给到ip核。

31.请参阅图6,由于旋转后,原图像的坐标经过变换,同一行的像素在旋转 后形成的图像上不再是在同一行上,原图像同一行连续的像素点,在旋转后 的图像上不再是连续的,无法直接连续的存入ddr中,用常规图像操作方法 行不通。

32.本方案提出了一种方法:1)同一将旋转后的图像范围设置为5000*5000 的分辨率,将5000*5000分辨率的长5000和宽5000带入旋转矩阵,即可计算 出原图像旋转后各像素点在新图像中的坐标;2)在fpga中,用bmg ip核例 化4个存储器,用来缓存输入数据,分别为1个像素数据存储器、2个地址存 储器、1个计数存储器,其中素数据存储器配置为:emery type配置为true dualport ram;port a读写位宽都设为24bit,读写深度设为40000,port b读 写位宽设为192bit,读写深度为5000,port a用于写数据,port b用于读数 据;地址存储器配置为:memery type配置为true dual port ram;port a 读写位宽都设为28bit,读写深度设为5000,port b读写位宽设为28bit, 读写深度为5000,port a用于写数据,port b用于读数据;计数存储器的配 置为:memery type配置为true dual port ram;port a读写位宽都设为3bit, 读写深度设为5000,port b读写位宽设为3bit,读写深度为5000,port a用 于写数据,port b用于读数据,三个存储器的port b的存储深度都为5000, 对应旋转后图像垂直方向上的行数,每一个数据地址与图像的相应的行一一 对应。

33.请参阅图7至11,旋转后的图像,其y坐标落在上下两根虚线之间。0

°ꢀ

~90

°

和180

°

~270

°

原图像的第一行和第一列在旋转后的坐标中对应的地址 作为ddr3中的初始地址,90

°

~180

°

和270

°

~360

°

原图像的第一行和最后 一列在旋转后坐标中对应的地址作为ddr3中的初始地址,将此地址作为初始 地址存入addr_mem_original中,在帧同步信号有效时读出存入 addr_mem_deal待用并且将原图像原点旋转后的y坐标pic_y_start赋值给 pic_y0,然后以0

°

~90

°

为例,在frame_hsync行同步信号有效时将pic_y0 赋值给pic_y作为当前这行的初始地址,在frame_de帧数据有效时每输入一 个数据,计算其旋转后的y坐标pic_y作为data_mem_deal和addr_mem_deal 以及cnt_mem的索引地址,将数据存入data_mem_deal,data_mem_deal port a 的索引地址为pic_y*8+cnt_mem[pic_y],然后将cnt_mem[pic_y]加1,当 cnt_mem某次读出来的值为7时,说明该行已经缓存入8个数据,可以读出给 到fifo中了,随即同步将data_mem_deal和addr_mem_deal对应索引地址的 数据读出,传给fifo,读出后将addr_mem_deal读出的值加8后再写回原索引 地址,表示该行后面8个数据在ddr3中的地址加8。其他角度同理,由于180

°ꢀ

~360

°

原图像原点在右边,所以处理过程和0

°

~90

°

是反的,cnt_mem每次 是减1,addr_mem_deal每次是减8,frame_de信号被拉低后计算下一行的起 始地址赋值给pic_y0,然后重复上述步骤。

[0034]

将输出数据data_out[191:0]和addr_out[27:0]一起同步传入r/w模块 中的fifo中缓存,当缓存中的数据量达到一定数量后,r/w模块会同步将 data_out[191:0]和addr_out[27:0]读出来送入ddr3 ip核存入ddr3中,存 入时将data_out[191:0]存入的地址为addr_out[27:0]。

[0035]

当ddr3中存完一帧数据后由于乒乓操作将跳到另外的bank继续下一 帧的写入,然后hdmi显示模块从已经写完的帧读取数据出去显示。

[0036]

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而 言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行 多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限 定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1