基于OCT&IVUS影像数据实时同步显示装置的制作方法

本申请涉及医疗器械,具体涉及一种基于oct&ivus影像数据实时同步显示装置。

背景技术:

1、光学断层扫描成像(简称为oct)和血管超声扫描成像(简称为ivus)这种两技术在影像成像时所需要的工作时钟和频率均不相同,物理上分别依赖于两路不同源的时钟系统。

2、对于oct&ivus的混合成像系统的常规做法是按照oct和ivus的工作时钟进行独立采样,然后通过软件算法计算时序上的差异并将数据进行对齐处理,最终在屏幕上完成同一时间点的采样影像显示。但是上述方案从时效性上分析,由于数据是后处理模式,不具备实时性;同时因数据需要由处理器参与运算,其影像成像预处理对齐耗时较长,系统成像响应慢。

技术实现思路

1、有鉴于此,本申请提供一种基于oct&ivus影像数据实时同步显示装置,该装置实现了oct&ivus影像数据实时同步显示功能,解决了因依靠处理器和软件算法共同参与的预处理过程带来的显示滞后性和显示帧率偏低问题,同时减轻了计算机系统的运行负载。

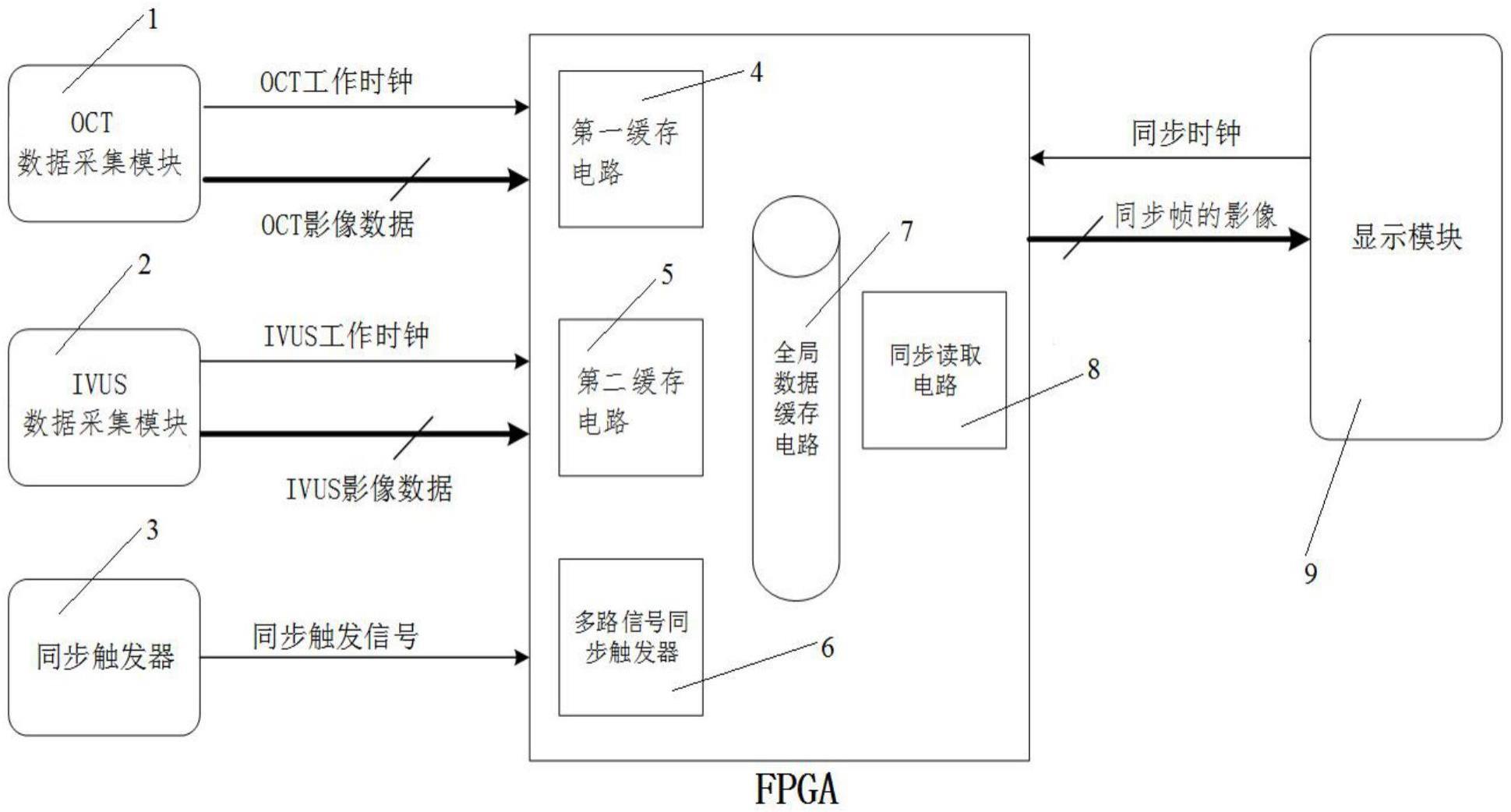

2、为实现上述目的,根据本申请的一个方面,提供了一种基于oct&ivus影像数据实时同步显示装置,包括oct数据采集模块、ivus数据采集模块、同步时钟、同步触发器、fpga芯片以及显示模块,其中,

3、所述fpga芯片内具有第一缓存电路、第二缓存电路、全局数据缓存电路、同步读取电路以及多路信号同步触发器;

4、所述oct数据采集模块用于采集oct影像数据,并按照oct工作时钟将其采集的数据传输至所述第一缓存电路中;

5、所述ivus数据采集模块用于采集ivus影像数据,并按照ivus工作时钟将其采集的数据传输至所述第二缓存电路中;

6、所述同步时钟用于将第一缓存电路中的数据以及第二缓存电路中的数据同步至所述全局数据缓存电路;

7、所述同步触发器用于触发激活所述多路信号同步触发器;

8、所述多路信号同步触发器通过一个时间窗口捕获所述oct工作时钟,ivus工作时钟和同步时钟均为有效的时刻,并向所述同步读取电路发送触发信号,以激活所述同步读取电路;

9、所述同步读取电路用于搬空所述全局数据缓存电路中的数据,并将oct影像数据和ivus影像数据构建为同步帧的影像传输至显示模块;

10、所述显示模块用于显示同一时刻的所述oct影像数据和ivus影像数据同步帧的影像。

11、进一步地,所述同步时钟将同一周期内的每一帧oct影像数据和每一帧ivus影像数据同步至所述全局数据缓存电路。

12、进一步地,所述同步触发器周期性地向所述多路信号同步触发器发出信号以激活所述所述多路信号同步触发器。

13、进一步地,所述同步触发器发出信号的周期为所述oct数据采集模块采集一帧数据的时间;

14、所述oct数据采集模块采集一帧数据的时间与所述ivus数据采集模块采集一帧数据的时间相同。

15、进一步地,所述同步读取电路周期性的搬空所述全局数据缓存电路中的数据,并将每一帧oct影像数据和每一帧ivus影像数据同步对齐,多组同步对齐后的影像数据构建为同步帧的影像传输至显示模块。

16、进一步地,所述同步触发器为旋转编码器。

17、根据本申请所述的基于oct&ivus影像数据实时同步显示装置实现了oct&ivus影像数据实时同步显示功能,解决了因依靠处理器和软件算法共同参与的预处理过程带来的显示滞后性和显示帧率偏低问题,同时减轻了计算机系统的运行负载。

技术特征:

1.一种基于oct&ivus影像数据实时同步显示装置,其特征在于,包括oct数据采集模块、ivus数据采集模块、同步时钟、同步触发器、fpga芯片以及显示模块,其中,

2.根据权利要求1所述的装置,其特征在于,所述同步时钟将同一周期内的每一帧oct影像数据和每一帧ivus影像数据同步至所述全局数据缓存电路。

3.根据权利要求1所述的装置,其特征在于,所述同步触发器周期性地向所述多路信号同步触发器发出信号以激活所述多路信号同步触发器。

4.根据权利要求3所述的装置,其特征在于,所述同步触发器发出信号的周期为所述oct数据采集模块采集一帧数据的时间;

5.根据权利要求1所述的装置,其特征在于,所述同步读取电路周期性的搬空所述全局数据缓存电路中的数据,并将每一帧oct影像数据和每一帧ivus影像数据同步对齐,多组同步对齐后的影像数据构建为同步帧的影像传输至显示模块。

6.根据权利要求1所述的装置,其特征在于,所述同步触发器为旋转编码器。

技术总结

本申请公开了一种基于OCT&IVUS影像数据实时同步显示装置,包括OCT数据采集模块、IVUS数据采集模块、同步时钟、同步触发器、FPGA芯片以及显示模块,其中,FPGA芯片内具有第一缓存电路、第二缓存电路、全局数据缓存电路、同步读取电路以及多路信号同步触发器;本申请所述的基于OCT&IVUS影像数据实时同步显示装置实现了OCT&IVUS影像数据实时同步显示功能,解决了因依靠处理器和软件算法共同参与的预处理过程带来的显示滞后性和显示帧率偏低问题,同时减轻了计算机系统的运行负载。

技术研发人员:肖琳,张林涛,冯庆宇

受保护的技术使用者:武汉阿格斯科技有限公司

技术研发日:20221230

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!