具有集成CMOS电路的MEMS装置的制作方法

本发明涉及一种具有集成cmos电路的微机电系统mems装置以及制造该装置的方法。

背景技术:

1、mems装置用于多种应用中。通常,该装置包含使用控制电路控制或与感测电路接口的mems组件。mems组件的一种可能的类型是致动器,例如压电致动器。

2、压电致动器的一个应用是用于包括喷墨打印机的打印机,压电致动器还用于增材制造、纺织品、生物技术和制药应用。喷墨打印机通过将微滴喷射到打印介质上以用于在打印介质(例如纸)上重建数字图像。许多喷墨打印机结合了“按需喷墨”技术,其中控制了从打印头的喷墨喷嘴相继地喷射个别墨滴。墨滴以足够的动量喷射,使得它们粘附到该介质上。根据施加的驱动信号喷射每个微滴,该驱动信号将按需喷墨打印机与连续喷墨装置区分开,在连续喷墨装置中,通过微型喷嘴泵送墨水来生成连续的墨滴流。

3、成功的按需喷墨技术是压电喷墨打印机。压电喷墨打印机将压电致动器结合到流体腔的壁中。压电元件的变形使压电致动器发生偏转,引起存储在流体腔内的打印流体中的压力变化,从而使微滴通过喷嘴喷射。

4、wo 2018/054917 a1涉及一种用于打印头的微滴喷射器,其包含与衬底集成并与第一电极和第二电极电连接的电子组件,第一电极和第二电极之间设有压电致动器。形成喷嘴形成层的材料在电子组件上延伸,并且还限定了流体腔的流体腔出口。压电致动器覆盖喷嘴形成层。

5、us 2011/0169892 a1涉及一种用于注射式打印机的喷嘴,其包括限定了喷嘴端口的顶层、限定了支撑顶层的喷嘴腔壁的衬底层,以及附接到衬底的致动器组合件,致动器组合件包括支撑件、从支撑件悬伸出以终止于喷嘴腔壁内的活塞中的杠杆臂和设置在杠杆臂的与活塞的末端相对的末端处的螺线管,该螺线管包括可移动的磁极和与可移动的磁极间隔开的固定的磁极。

6、正是在这种背景下设计了本公开。

技术实现思路

1、根据本公开的一方面,提供了一种制造微机电系统mems装置的方法。mems装置包含微机电组件和被配置成与微机电组件导电连通的集成电路。该方法包含:在衬底上形成多个集成电路层以形成集成电路,多个集成电路层包含多个集成电路钝化层和金属化层;去除该装置的组件区域中的多个集成电路钝化层和金属化层中的至少一个的部分;以及形成一个或多个组件区域层来代替组件区域中被去除的部分以形成可移动的微机电组件,一个或多个组件区域层与多个集成电路钝化层和金属化层中的至少一个的部分不同。

2、因此,该组件不需要包括集成电路层的至少一些,选择这些电路层通常是为了它们在集成电路中的功能性而不是为了该组件,因此,可以具体地选择组件区域层以提供可移动的微机电组件的预期特性。此类特性可以包括杨氏模量、厚度或密度。

3、此外,通过去除和替换组件区域中的功能冗余层,mems装置可以特别紧凑,这是因为该组件不需要包括冗余层的至少一些。

4、应当理解,该方法通常包含精确地去除多个集成电路钝化层和金属化层中的至少一个的部分。换句话说,不是去除至少一个层的全部。

5、还应当理解,集成电路层是为mems装置提供集成电路的层。类似地,应当理解,组件区域层是形成可移动的mems装置的部分的任何层,因此不形成mems装置的集成电路的部分。

6、多个集成电路层可以是多个cmos电路层。

7、因此,根据本公开的另一方面,提供了一种制造微机电系统mems装置的方法。mems装置通常包含可移动的微机电组件和被配置成与微机电组件导电连通的cmos电路。该方法包含:在衬底上形成多个cmos电路层以形成cmos电路,多个cmos电路层包含多个cmos电路钝化层和金属化层;去除该装置的组件区域中的多个cmos电路钝化层和金属化层中的至少一个的部分;以及形成一个或多个组件区域层来代替组件区域中被去除的部分以形成可移动的微机电组件,一个或多个组件区域层与多个cmos电路钝化层和金属化层中的至少一个的部分不同。

8、因此,组件区域不需要包括cmos电路层的至少一些,选择这些电路层通常是为了它们在cmos电路中的功能性而不是为了该组件,因此,可以具体地选择一个或多个组件区域层以提供可移动的微机电组件的预期特性。此类特性可以包括杨氏模量、厚度或密度。

9、一个或多个组件区域层可以各自具有大于10吉帕斯卡的杨氏模量。一个或多个组件区域层可以各自具有小于1,200吉帕斯卡的杨氏模量,例如小于700吉帕斯卡。

10、在一些实例中,一个或多个组件区域层的刚度小于(例如,小于一半)被去除的部分的刚度。换句话说,一个或多个组件区域层比它们替换的部分更有柔性。因此,增强了柔性。

11、在其它实例中,一个或多个组件区域层的刚度可以大于(例如,大于两倍)被去除的部分的刚度。因此,可以增强致动力。

12、此外,通过去除和替换组件区域中的冗余层,mems装置可以特别紧凑,这是因为该组件不需要包括冗余层的至少一些。

13、更进一步,该方法允许使用对材料特性和厚度具有特别好的容差控制的工艺来沉积作为组件区域层中的一个的mems钝化特征部件。应当理解,在形成期间,cmos电路经受多个工艺步骤以优化电性能。此类工艺步骤可能损害对mems功能性重要的机械和结构方面。因此,有益的是,可以去除和替换形成mems组件的组件区域中的cmos钝化层和金属化层中的至少一些。这对于多个mems组件装置的阵列特别重要。因此,该方法减少了工艺变化并提高了晶圆产量。

14、应当理解,多个集成电路钝化层和金属化层可以一起在多个集成电路层内形成一个或多个集成电路金属化特征部件,其由集成电路钝化区域包围。类似地,应当理解,多个cmos钝化层和金属化层可以一起在多个cmos电路层内形成一个或多个cmos金属化特征部件,其由cmos钝化区域包围。

15、多个cmos钝化层和金属化层可以包含多个cmos钝化层和多个cmos金属化层。

16、一个或多个组件区域层至少部分地与一个或多个cmos电路层中的至少一个的部分不同。

17、一个或多个组件区域层可以是多个至少两个不同的组件区域层。

18、在cmos钝化层和金属化层的上下文中的金属化应当被理解为诸如cmos电路的集成电路的基本任何区域,其提供集成电路的组件之间的互连,或者集成电路和集成电路的外部连接器之间的互连。金属化区域可以由金属形成,例如铝、铜、铝铜合金或任何其它合适的合金。

19、在cmos钝化层和金属化层的上下文中的钝化应当被理解为诸如cmos电路的集成电路的基本任何区域,其通过将集成电路的诸如晶体管表面的一个或多个组件与环境中的电条件和/或化学条件隔离来为集成电路提供电稳定性。钝化区域可以由绝缘材料形成,例如氧化物、氮化物、碳化物及其组合,例如它们的层压体。

20、衬底通常由硅形成。衬底可以由硅晶片形成。

21、应当理解,术语“金属化区域”和“钝化区域”是本领域技术人员公知的。

22、cmos电路通常进一步包含形成多个晶体管的多个电路层,多个晶体管能一起操作以使cmos电路充当控制电路(即,控制器)。可以理解,用于cmos金属化层或cmos钝化层的典型制造工艺包括抛光步骤,以制备用于在其上施加另一层的层。抛光(有时被称为化学机械抛光cmp步骤)通常不可能仅在具有明确界定的边界的层的局部化子区域中进行。因此,通常抛光整个层。由于这个原因,应当理解,在整个衬底上施加cmos钝化层和金属化层,并且必须随后在衬底上不需要钝化层和金属化层的任何区域中去除钝化层和金属化层。

23、去除该装置的组件区域中的多个cmos钝化层和金属化层中的至少一个的部分可以包含去除多个cmos钝化层和金属化层中的多于一个的部分。去除该装置的组件区域中的多个cmos钝化层和金属化层中的至少一个的部分可以包含去除多个cmos钝化层和金属化层中的每一个的部分。

24、因此,没有cmos钝化层和金属化层保留在组件区域中,因此,该装置的组件区域可以完全由与多个cmos钝化层和金属化层不同的层形成。

25、去除多个cmos钝化层和金属化层中的至少一个的部分可以包含蚀刻要去除的这些层。因此,可以使用在集成电路制造过程中常用的简单工艺来去除这些层。

26、蚀刻可以是深反应离子蚀刻drie。可选地,蚀刻可以是标准的钝化蚀刻,以去除cmos钝化层和金属化层中的一个或多个钝化区域。

27、蚀刻可以仅到达部分地穿过衬底的组合件和多个cmos钝化层和金属化层的位置。

28、可以从与衬底相对的组件区域的一侧进行蚀刻。因此,蚀刻可以去除直到衬底的组件区域中的多个cmos钝化层和金属化层。

29、一个或多个组件区域层中的至少一个可以由与多个cmos电路层中的邻近层不同的材料形成。邻近层可以与一个或多个组件区域层中的至少一个齐平。因此,可以使用不同的材料配置来实现为了代替cmos电路层而设置的一个或多个组件区域层与多个cmos电路层相比不同的功能特性。该材料可以与用于多个cmos电路层中的任何层的那些材料中的任一种不同。

30、在其它实例中,可以形成一个或多个组件区域层中的至少一个,以具有与多个cmos电路层中的邻近层不同的厚度。在这种情况下,一个或多个组件区域层中的至少一个可以由与邻近层相同的材料形成。一个或多个组件区域层中的至少一个可以被形成为单个层或不同材料的层压体。

31、形成一个或多个组件区域层可以包含沉积mems钝化层来代替被去除的部分。mems钝化层可以在组件区域之外的多个cmos钝化层和金属化层上延伸。mems钝化层可以由与多个cmos钝化层和金属化层中的cmos钝化区域不同的材料形成。在其它实例中,mems钝化层可以由与多个cmos钝化层和金属化层,或单个层,或不同材料的层压体中的cmos钝化区域相同的材料形成,但具有与其不同的厚度。因此,mems钝化层被配置成特别适合用于组件区域中的微机电组件的结构。

32、mems钝化层可以是与在mems组件的操作期间功能上涉及的任何其它组件区域层不同的层。

33、在一些实例中,mems钝化层可以由不适合用作由多个cmos钝化层和金属化层形成的cmos钝化区域的材料形成。

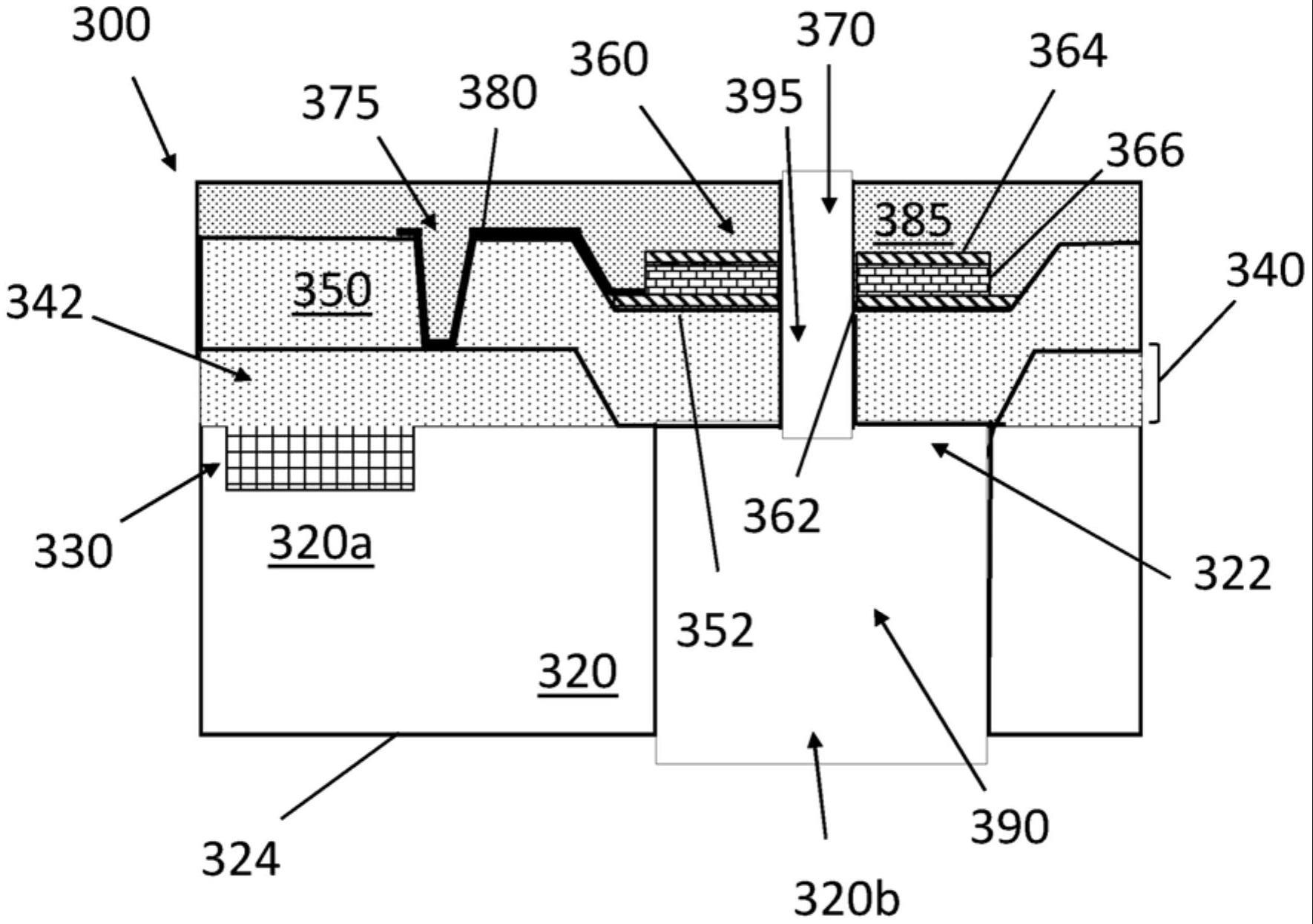

34、从另一方面看,本公开提供一种微机电系统mems装置,其包含衬底,衬底具有与其一体提供的cmos电路。cmos电路由包括多个cmos钝化层和金属化层的多个cmos电路层形成。cmos电路被设置在mems装置的cmos电路区域中。mems装置进一步包含可移动的微机电组件,其被配置成由集成电路控制并被设置在mems装置的组件区域中。组件区域与cmos电路区域不同。组件区域包含包括微机电组件的一个或多个组件区域层。组件区域中的一个或多个组件区域层或一个或多个组件区域层中的每一个与集成电路区域的多个cmos钝化层和金属化层中的每一个不同。

35、因此,该组件由如cmos电路的cmos钝化层或cmos金属化层不是为了它们的功能性而选择的层形成。

36、cmos电路区域可以在平行于衬底的平面的方向上邻近组件区域。

37、衬底可以包含第一表面,第一表面具有在其上形成的多个cmos钝化层和金属化层中的一个。在组件区域中,组件区域层可以延伸为与第一表面共面。

38、一个或多个组件区域层中的一个可以是mems钝化层。因此,相对于在集成电路区域中的多个cmos钝化层和金属化层,可以为其它组件区域层提供电稳定性和化学隔离。

39、一个或多个组件区域层有时可以被称为替换层。

40、mems钝化层可以覆盖在集成电路区域中的多个cmos钝化层和金属化层。因此,mems钝化层可以为cmos电路组件提供与环境的进一步电隔离和化学隔离。

41、mems钝化层可以在其中限定开口,以提供与cmos电路的多个cmos钝化层和金属化层的cmos金属化区域的电连接。可以经由mems金属化组件提供电连接,将cmos金属化区域连接到微机电组件的第一电极和第二电极中的至少一个。

42、该方法可以包含在mems钝化层中形成开口。可以通过蚀刻来形成开口。蚀刻可以是深反应离子蚀刻drie方法或标准的cmos钝化蚀刻方法。

43、mems装置可以包含覆盖微机电组件、mems钝化层和mems金属化层的封装层。该方法可以包含例如通过沉积来形成封装层。

44、衬底可以在其组件区域中限定开口。微机电组件可以包含在开口上延伸的悬臂。微机电组件可以包含在开口上延伸的膜片。

45、上文所述的开口的一个或多个可以具有蚀刻侧。

46、该方法可以包含在其组件区域中形成衬底中的开口。因此,当在组件区域中形成衬底中的开口时,可以在组件区域中从衬底释放一个或多个组件区域层,由此相对于在组件区域之外的该装置的部分其更容易弯曲(即,移动)。

47、可以通过蚀刻来形成衬底中的开口。蚀刻可以是深反应离子蚀刻drie方法或其它方法,例如各向异性湿法蚀刻。

48、可以从与微机电组件相对的衬底的一侧形成衬底中的开口。衬底中的开口可以延伸到一个或多个组件区域层。衬底中的开口可以延伸到mems钝化层。这样,当通过蚀刻来形成衬底中的开口时,一个或多个组件区域层可以被配置成充当蚀刻终止。换句话说,进行蚀刻时通常不超过蚀刻终止。

49、mems装置可以进一步包含穿过mems钝化层和封装层的喷嘴开口,以允许流体在至少部分地由衬底限定的流体腔与mems装置的外部环境之间流过mems钝化层和封装层中的开口。

50、微机电组件可以是多个微机电组件。多个微机电组件中的每一个可以限定组件区域中的相应的喷嘴开口。因此,mems装置可以包括多个喷嘴开口。微机电组件中的每一个可以电连接到cmos电路。微机电组件中的每一个可以被配置成由cmos电路控制。因此,可以通过cmos电路为多个微机电组件提供控制。

51、该方法可以进一步包含形成喷嘴开口。可以通过蚀刻来形成喷嘴开口。蚀刻可以是深反应离子蚀刻drie或其它传统的cmos钝化蚀刻。可以从与衬底相对的mems装置的一侧形成喷嘴开口。

52、在一些实例中,可以在衬底开口形成之前形成喷嘴开口。在其它实例中,可以在衬底开口形成之后形成喷嘴开口。

53、微机电组件可以是压电组件。换句话说,微机电组件可以包括在微机电组件中功能上使用的压电材料的一个或多个区域。

54、微机电组件可以是致动器。

55、致动器可以是压电致动器。

56、致动器可以包含第一电极、第二电极和设置在第一电极和第二电极之间的压电致动器本体。第一电极和第二电极中的至少一个可以经由多个cmos钝化层和金属化层的cmos金属化区域中的一个或多个电连接到cmos电路。

57、压电组件通常包含设置在第一电极和第二电极之间的压电体。所述第一电极和第二电极中的至少一个通常电连接到至少一个电子组件(例如cmos电路的电子组件)。压电体通常包含能在低于450℃的温度下加工的一种或多种压电材料(例如由其形成)。

58、高于300℃,集成电子组件(例如cmos电子组件)通常开始劣化,妨碍装置操作并降低效率。高于450℃,集成电子组件(例如cmos电子组件)通常甚至更严重地退化。因此,能在低于450℃的温度下加工的压电材料的使用允许压电组件与至少一个电子组件(例如驱动电路的电子组件)的加工和集成,而基本上不损害所述至少一个电子组件。

59、可以是,压电体包含能在低于300℃的温度下加工的一种或多种压电材料(例如由其形成)。能在低于300℃的温度下加工的压电材料的使用允许压电组件与至少一个电子组件(例如驱动电路的)的加工和集成,而对所述至少一个电子组件的损害甚至更小。能在低于300℃的温度下加工的压电材料的使用通常允许由单个衬底(例如从单个衬底晶片)上的多个mems装置的大规模制造实现功能性装置的较高产量。

60、通过将压电组件与至少一个电子组件(例如驱动电子器件)集成,减少或消除了提供单独的驱动电子器件的需要。因此,大量的压电组件可以紧密地集成在一个芯片上,增加了每个芯片的组件,减小了整个装置大小,并且相比能用具有压电mems组件的现有的mems装置实现的组件密度,允许更高的组件密度。与在单个芯片上集成相关联的其它益处包括最终降低的制造成本、模块性和装置可靠性。

61、相比需要在较高温度下加工的压电材料,能在低于450℃(或低于300℃)下加工的压电材料通常具有更差的压电特性(例如更低的压电常数)。例如,相比由诸如氮化铝(aln)的可低温处理的压电材料形成的压电致动器,由诸如锆钛酸铅(pzt)的可高温处理的压电材料形成的压电致动器能够施加大一个数量级的力,所有其它因素是相等的。

62、一种或多种压电材料通常能在低于450℃(或低于300℃)的温度下加工(例如,可沉积,并且如果需要,可退火),使得压电组件能在低于450℃(或低于300℃)的温度下制造。在低于450℃(或低于300℃)的温度下压电组件的制造允许压电组件与集成有衬底的至少一个电子组件的集成。

63、因此,压电体通常能在低于450℃(或低于300℃)的温度下成形(例如,通过沉积一种或多种压电材料,并且如果需要,使其退火)。

64、一种或多种压电材料通常能在低于450℃(或低于300℃)的衬底温度下加工(例如,可沉积,并且如果需要,可退火)。换句话说,在一种或多种压电材料的加工(例如,沉积,并且如果需要,退火)期间,衬底的温度通常不会达到或超过450℃(或300℃)。在压电体形成期间,衬底的温度通常不会达到或超过450℃(或300℃)。在压电组件制造期间,衬底的温度通常不会达到或超过450℃(或300℃)。可以是,在(例如整个)mems装置制造期间,衬底的温度不会达到或超过450℃(或300℃)。

65、压电体可以包含一种压电材料(例如由其形成)。可选地,压电体可以包含多于一种压电材料(例如由其形成)。

66、压电体可以包含陶瓷材料(例如由其形成),其包含铝和氮以及任选地选自以下的一种或多种元素:钪、钇、钛、镁、铪、锆、锡、铬、硼。

67、压电体可以包含氮化铝(aln)(例如由其形成)。

68、压电体可以包含氧化锌(zno)(例如由其形成)。

69、一种或多种压电材料可以包含氮化铝和/或氧化锌(例如由其组成)。

70、氮化铝可以由纯氮化铝组成。可选地,氮化铝可以包含一种或多种元素(即氮化铝可以包含氮化铝化合物)。氮化铝可以包含以下元素中的一种或多种:钪、钇、钛、镁、铪、锆、锡、铬、硼。

71、压电体可以包含氮化钪铝(scaln)(例如由其形成)。通常选择氮化钪铝中钪的百分比以在可制造的限度内优化压电常数d31。例如,通常从范围0<x≤0.5中选择scxal1-xn中的x的值。钪的较大级分通常导致d31的较大值(即较强的压电效应)。氮化钪铝中钪的质量百分比(即重量百分比)通常大于5%。氮化钪铝中钪的质量百分比(即重量百分比)通常大于10%。氮化钪铝中钪的质量百分比(即重量百分比)通常大于20%。氮化钪铝中钪的质量百分比(即重量百分比)通常大于30%。氮化钪铝中钪的质量百分比(即重量百分比)通常大于40%。氮化钪铝中钪的质量百分比(即重量百分比)可以小于或等于50%。

72、包括氮化铝化合物(并且特别是氮化钪铝)的氮化铝和氧化锌是可以在低于450℃,或更优选地在低于300℃下沉积的压电材料。包括氮化铝化合物(并且特别是氮化钪铝)的氮化铝和氧化锌是可以在低于450℃,或更优选地在低于300℃下通过物理气相沉积(例如溅射)来沉积的压电材料。包括氮化铝化合物(并且特别是氮化钪铝)的氮化铝和氧化锌是在沉积之后通常不需要退火的压电材料。

73、压电体可以包含氮化铝(例如诸如氮化钪铝的氮化铝化合物)和/或氧化锌(例如由其形成),其在低于450℃,或更优选地在低于300℃下通过物理气相沉积来沉积。

74、压电体可以包含一个或多个iii-v族半导体和/或ii-vi族半导体(即包含来自周期表的iii族和v族和/或ii族和vi族的元素的化合物半导体)(例如由其形成)。此类iii-v族半导体和ii-vi族半导体通常以六方纤锌矿晶体结构结晶。由于以六方纤锌矿晶体结构结晶的iii-v族半导体和ii-vi族半导体具有非中心对称晶体结构,它们通常是压电体。

75、压电体可以包含非铁电压电材料(例如由其形成或由其组成)。一种或多种压电材料可以是一种或多种非铁电压电材料。铁电材料通常需要在强外加电场下(即沉积后)极化。非铁电压电材料通常不需要极化。

76、压电体通常具有压电常数d31,其量值小于30pc/牛顿,或更通常地小于20pc/牛顿,或甚至更通常地小于10pc/牛顿。一种或多种压电材料通常具有压电常数d31,其量值小于30pc/牛顿,或更通常地小于20pc/牛顿,或甚至更通常地小于10pc/牛顿。

77、一种或多种压电材料通常是cmos兼容的。由此,应当理解,一种或多种压电材料通常不包含损害cmos电子结构的物质,或者通常能在不使用损害cmos电子结构的物质的情况下加工(例如,可沉积,并且如果需要,可退火)。例如,一种或多种压电材料的加工(例如沉积,并且如果需要,退火)通常不包括(例如强)酸(例如盐酸)和/或(例如强)碱(例如氢氧化钾)的使用。

78、本领域技术人员应当理解,可选的致动器设计也是可能的,例如具有多个电极的多个致动器。

79、该方法可以包含在mems钝化层上沉积微机电组件。可以使用物理气相沉积(pvd)方法来沉积微机电组件。具体地,通常使用物理气相沉积方法来沉积压电致动器本体。

80、压电致动器本体可以包含一种或多种pvd沉积的压电材料。

81、mems装置可以是用于打印头的微滴喷射器。因此,致动器可以用于从打印头排出微滴。换句话说,本公开可以延伸到打印头。打印头可以是喷墨打印头。微滴喷射器可以是用于(例如被配置成用于)喷墨打印头的微滴喷射器。微滴喷射器可以是墨滴喷射器。

82、打印头可以被配置成打印流体(例如功能性流体)以用于制造打印电子器件。

83、打印头可以被配置成打印生物流体。生物流体通常包含生物大分子,例如诸如dna或rna、微生物和/或酶的多核苷酸。打印头可以被配置成打印用于生物或生物技术应用的其它流体,例如稀释剂或试剂。

84、打印头可以是体素打印头(即被配置用于诸如增材打印的3d打印的打印头)。

85、打印头通常用于打印机。因此,本公开延伸到包含一个或多个打印头的打印机。应当理解,打印机基本上是被设置成排出打印材料(例如,诸如墨水的打印液体)以创建打印对象的预期外观(例如,颜色)和/或形状和/或功能的任何设备。打印机可以是被设置为将彩色墨水打印到衬底(例如,纸)上的2d打印机。在其它实例中,打印机可以是被配置成通过从打印机的一个或多个打印头排出打印材料来创建3d对象的增材制造装置(即3d打印机)。

86、因此,从另一方面看,本公开延伸到包含一个或多个打印头的打印机,一个或多个打印头包含上文所述的mems微滴喷射器。打印机可以被配置成从mems微滴喷射器喷射打印液体(例如,墨水),通过控制mems压电致动器的操作以使一个或多个组件区域层中的至少一个弯曲,由此从其中排出打印液体。打印机可以进一步包含打印液体源。打印液体源可以是打印液体盒。

87、从另一方面看,本公开还延伸到一种打印方法。该方法包含提供包括如上文所述的打印机的打印设备。该设备包含打印液体源。可以是,打印液体(例如,墨水)源是打印机的部分。打印机包含一个或多个打印头,每个打印头包含如上文所述的一个或多个微滴喷射器。该方法包含控制一个或多个微滴喷射器中的至少一个,使得致动器使一个或多个组件区域层中的至少一个弯曲,由此从微滴喷射器喷射打印液体。因此,打印机使用打印液体来打印。

88、致动器可以生成例如用于pmut或扬声器的声音。致动器可以用于射流泵。

89、微机电组件可以是传感器组件。传感器组件可以是压电传感器组件。换句话说,可以将微机电组件的移动转换为可以传导到cmos电路的电信号。传感器组件可以是麦克风、压力传感器或生物传感器。

90、根据本公开的又一方面,提供了一种微机电系统mems装置,其包含衬底,衬底具有与其一体提供的cmos电路。cmos电路由包括多个cmos钝化层和金属化层的多个cmos电路层形成,多个cmos钝化层和金属化层一起限定由一个或多个cmos钝化区域包围的多个cmos金属化区域。多个cmos钝化层和金属化层一起在第一平面与第二平面之间延伸,第一平面由邻接衬底的多个cmos钝化层和金属化层中的一个限定,并且第二平面平行于第一平面并由多个cmos钝化层和金属化层中的最远的一个限定。cmos电路被设置在mems装置的cmos电路区域中。mems装置进一步包含可移动的微机电组件,其被配置成由集成电路控制并被设置在mems装置的组件区域中。组件区域与cmos电路区域不同。组件区域包含包括微机电组件的一个或多个组件区域层。一个或多个组件区域层中的至少一个延伸到第一平面。延伸到第一平面的一个或多个组件区域层中的至少一个与邻接衬底的多个cmos钝化层和金属化层中的一个不同。

91、因此,在与多个cmos钝化层和金属化层相同的平面中,mems装置的组件区域中的对应层是不同的。

92、通常,延伸到第一平面的一个或多个组件区域层邻近多个cmos钝化层和金属化层。延伸到第一平面的一个或多个组件区域层可以从衬底的与多个cmos钝化层和金属化层相同的一侧延伸。延伸到第一平面的一个或多个组件区域层中的至少一个可以在从第二平面到第一平面的方向上延伸。

93、第一平面可以被限定为邻接衬底的多个cmos钝化层和金属化层中的一个与衬底之间的边界。

94、在一些实例中,延伸到第一平面的一个或多个组件区域层中的至少一个由与邻接衬底的多个cmos钝化层和金属化层中的一个不同的材料形成。在其它实例中,延伸到第一平面的一个或多个组件区域层中的至少一个由与邻接衬底的多个cmos钝化层和金属化层中的一个相同的材料形成,但具有与其不同的厚度。

95、mems钝化层的厚度可以小于多个cmos钝化层和金属化层的组合厚度。可选地,mems钝化层的厚度可以大于多个cmos钝化层和金属化层的组合厚度。

96、mems钝化层可以在组件区域中具有与在cmos电路区域中基本上类似的厚度。

97、在组件区域中背离衬底的mems钝化层的表面可以与在cmos电路区域中背离衬底的mems钝化层的表面基本上共面。

98、mems钝化层可以由多个层形成。多个层由至少两种不同材料形成。

99、mems装置可以包含设置在cmos电路区域之外的多个微机电组件。cmos电路可以与多个微机电组件中的多于一个电连通。

100、mems装置可以包含设置在组件区域之外的多个cmos电路。多个cmos电路可以包括不同类型的多个cmos电路。多个cmos电路可以包含至少一个hv cmos电路和至少一个lvcmos电路。附加地或可选地,可以通过一个或多个深沟道隔离(dti)结构来划分多个cmos电路。

101、在一些实例中,每个cmos电路与设置在cmos电路区域之外的多个微机电组件中的相应的一个电连通。

102、衬底可以包含一个或多个接合焊盘。

103、mems装置可以被配置成使得微机电组件经由作为一个或多个组件区域层中的一个提供的mems金属化层电连接到cmos电路。

- 还没有人留言评论。精彩留言会获得点赞!