显示面板以及其像素电路的制作方法

[0001]

本发明是有关于一种显示面板以及像素电路。

背景技术:

[0002]

随着电子科技的演进,在电子装置上提升高品质的显示装置成为重要的趋势。而有源发光式发光二极管,在成功微型化后,成为平面式显示面板的一种设计主流。

[0003]

在习知的技术领域中,发光二极管的亮度控制可基于脉冲宽度调变以及振幅调变两种方式。基于发光二极管在工作效率上的要求,在使发光二极管具有高外部量子效率(external quantum efficiency,eqe)的条件下,发光二极管需要工作在足够高的驱动电流下。如此一来,通过振幅调变的方式将无法有效维持发光二极管的高外部量子效率。而通过脉冲宽度调变的机制,在高解析度的需求上,也有设计上的困难。此外,在维持高外部量子效率的前提下,可能造成显示面板通过的总电流量过大,而难以实施的现象。

技术实现要素:

[0004]

本发明提供多种像素电路以及其所组成的显示面板,可提升发光元件的发光效率。

[0005]

本发明的像素电路包括驱动晶体管以及激光时间长度调变器。驱动晶体管具有控制端以接收脉宽控制信号以及振幅控制信号,驱动晶体管并产生驱动信号。激光时间长度调变器与驱动晶体管、控制开关以及发光元件串联耦接,在第一时间区间中,依据激光时间控制信号以调整提供驱动信号至发光元件的多个第二时间区间的时间长度。

[0006]

本发明的另一像素电路包括第一控制开关、驱动晶体管、第二控制开关、第一电容以及第一晶体管至第五晶体管。第一控制开关具有第一端接收电源电压,并受控于激光信号。驱动晶体管具有第一端耦接至第一控制开关的第二端。第一晶体管具有第一端接收显示数据,第一晶体管的第二端耦接至驱动晶体管的控制端,第一晶体管的控制端接收重置信号。第二晶体管具有第一端耦接至第一晶体管的第二端,第二晶体管的第二端耦接至驱动晶体管的第二端,第二晶体管的控制端接收第一栅极驱动信号。第三晶体管具有第一端以接收显示数据,第三晶体管的第二端耦接至驱动晶体管的控制端。第二电容的一端接收时序控制信号,另一端耦接至第三晶体管的控制端。第四晶体管具有第一端耦接至第三晶体管的控制端,第四晶体管的第二端耦接至驱动晶体管的控制端,第四晶体管的控制端接收重置信号或第二栅极驱动信号。第五晶体管具有第一端接收显示数据,第五晶体管的第二端耦接至驱动晶体管的第一端,第五晶体管的控制端接收第一栅极驱动信号。

[0007]

此外,本发明的显示面板包括多个第一像素列以及多个第二像素列。各第一像素列具有多个第一像素电路。第二像素列分别与第一像素列交错排列,各第二像素列具有多个第二像素电路。其中,第一像素电路以及第二像素电路的每一包括驱动晶体管、控制开关以及激光时间长度调变器。驱动晶体管具有控制端以接收脉宽控制信号以及振幅控制信号,驱动晶体管并产生驱动信号。控制开关与驱动晶体管以及发光元件串联耦接,依据激光

信号以控制驱动晶体管产生驱动信号的第一时间区间。激光时间长度调变器与驱动晶体管、控制开关以及发光元件串联耦接,在第一时间区间中,依据第一激光时间控制信号或第二激光时间控制信号以调整提供驱动信号至发光元件的多个第二时间区间的时间长度。

[0008]

基于上述,本发明的显示面板以及像素电路通过激光时间长度调变器以区分为激光时间区间的第一时间区间为多个第二时间区间,并借此进行亮度调整动作。如此一来,可维持发光元件在高外部量子效率(external quantum efficiency,eqe)的条件下工作,并可执行均匀的高度亮度的调整动作。本发明另一像素电路则通过电路整合的方式,来减低像素电路所需要的电路元件,并稳定驱动信号的输出品质。

[0009]

以下结合附图和具体实施例对本发明进行详细描述,但不作为对本发明的限定。

附图说明

[0010]

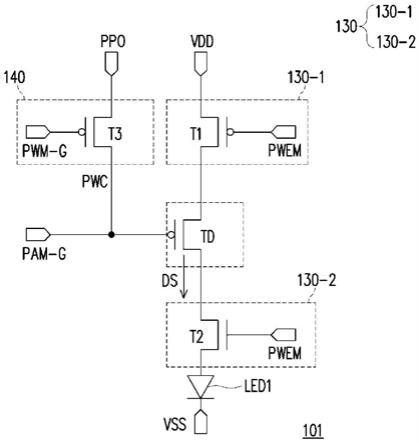

图1a为本发明一实施例的像素电路的示意图。

[0011]

图1b为本发明另一实施例的像素电路的示意图。

[0012]

图2为本发明实施例的像素电路的动作示意图。

[0013]

图3为本发明实施例的像素电路的动作波形图。

[0014]

图4a以及图4b分别为本发明实施例的像素电路的不同实施方式的示意图。

[0015]

图5为本发明另一实施例的像素电路的示意图。

[0016]

图6为本发明图5实施例的像素电路的动作波形图。

[0017]

图7为本发明另一实施例的像素电路的示意图。

[0018]

图8为本发明实施例的像素电路的一实施方式的示意图。

[0019]

图9为本发明实施例的像素电路的另一实施方式的示意图。

[0020]

图10为本发明一实施例的显示面板的示意图。

[0021]

图11为本发明图10实施例的激光时间控制信号的动作波形图。

[0022]

图12a为本发明另一实施例的像素电路的示意图。

[0023]

图12b为的本发明实施例的像素电路1200的动作波形图。

[0024]

图13为本发明另一实施例的像素电路的示意图。

[0025]

其中,附图标记:

[0026]

101、102、400、400

’

、500、700、800、900、1200、1300:像素电路

[0027]

1000:显示面板

[0028]

120、420、520、720、820、920、1220、1230:控制开关

[0029]

130-1、130-2:电路

[0030]

130、430、530、730、830、930、1011~1023:激光时间长度调变器

[0031]

140、440、540、740、840:脉宽控制信号产生器

[0032]

c1~c2:电容

[0033]

ds:驱动信号

[0034]

g-em、g-em1~g-em3、gg-em:激光信号

[0035]

ga:驱动信号

[0036]

gp:信号

[0037]

led1~led3、led11~led23:发光元件

[0038]

pwem、pwem1~pwem3:激光时间控制信号

[0039]

t1~t10、t41~t43、t41

’

~t43

’

、t511~t522、t53、t711~t723、t73:晶体管

[0040]

td、td

’

:驱动晶体管

[0041]

vdd:电源电压

[0042]

v0、tcs_l、tcs_h:电压

[0043]

vp1:脉宽调变数据

[0044]

vp2:振幅调变数据

[0045]

t1、t2、t31、t321~t323、t31

’

、ten1、ten2:时间区间

[0046]

ts1~ts6:阶段

[0047]

pwc:脉宽控制信号

[0048]

pwm-g:脉宽调变信号

[0049]

pam-g:振幅控制信号

[0050]

ppo:参考电压

[0051]

vss:参考电源

[0052]

data[m]:显示数据

[0053]

gg-res、res:重置信号

[0054]

g1[n]、g2[n]栅极驱动信号

[0055]

tcs:时序控制信号

[0056]

ref:参考信号

[0057]

p11~p23:像素电路

[0058]

pc1、pc2:像素列

具体实施方式

[0059]

下面结合附图对本发明的结构原理和工作原理作具体的描述:

[0060]

请参照图1a,图1a为本发明一实施例的像素电路的示意图。像素电路100包括驱动晶体管td以及由电路130-1、130-2组成的激光时间长度调变器130。驱动晶体管td具有控制端以接收脉宽控制信号pwc以及振幅控制信号pam-g,脉宽控制信号pwc依据脉宽调变信号pwm-g所产生。驱动晶体管td并产生驱动信号ds。在本实施例中,发光元件led1可以为任意形式的发光二极管。

[0061]

在另一方面,激光时间长度调变器130中的电路130-1、130-2与驱动晶体管td以及发光元件led1串联耦接。其中驱动晶体管td耦接在电路130-1、130-2中间。在本实施例中,电路130-1、130-2分别由晶体管t1、t2所建构,并耦接在驱动晶体管td、电源电压vdd以及发光元件led1间。晶体管t1、t2的控制端接收激光时间控制信号pwem,并依据激光时间控制信号pwem而被导通或断开。其中,晶体管t1、t2依据在第一时间区间(激光时间区间)中的多个第二时间区间中,依据激光时间控制信号pwem而被导通。其中,第二时间区的时间长度间可依据激光时间控制信号pwem进行调整,并借以调控发光元件led1的发光亮度。

[0062]

在本发明部分实施例中,激光时间长度调变器130中的电路130-1、130-2可以择一来实施即可。不必要同时建构电路130-1、130-2以形成激光时间长度调变器130。

[0063]

图1b为本发明另一实施例的像素电路的示意图。像素电路102包括驱动晶体管td、

控制开关120以及激光时间长度调变器130。驱动晶体管td具有控制端以接收脉宽控制信号pwc以及振幅控制信号pam-g。驱动晶体管td并产生驱动信号ds。控制开关120与驱动晶体管td以及发光元件led1串联耦接。控制开关120依据激光信号g-em以控制驱动晶体管td产生驱动信号ds的第一时间区间。在本实施例中,控制开关120由晶体管t2所建构。晶体管t2的耦接在驱动晶体管td的第一端与发光元件led1间。晶体管t2的控制端接收激光信号g-em,并在依据激光信号g-em而导通的第一时间区间,使驱动信号ds被提供至发光元件led1以驱使发光元件led1发光。

[0064]

值得一提的,在本发明实施例中,激光时间控制信号pwem的频率高于激光信号g-em的频率。

[0065]

在此请同步参照图1b以及图2,其中图2为本发明实施例的像素电路的动作示意图。图2的横轴为时间轴,纵轴则为驱动信号ds的电流。在图2中,在补偿时间区间tc中,像素电路100可执行电路的补偿动作,并在第一时间区间t1中,使控制开关120导通。并且,在第一时间区间t1中的多个第二时间区间t2,像素电路100中的晶体管t1依据激光时间控制信号pwem而被导通,并通过第二时间区间t2的时间长度来进行发光元件led1的亮度调整动作。

[0066]

由图2可以得知,当要调整发光元件led1所产生的亮度为低显示亮度时,除降低第一时间区间t1的时间长度外,还可以通过调低第二时间区间t2时间长度来完成。重点在于,本发明实施例中,并不需要通过降低驱动信号ds的电流值来使发光元件led1所产生的亮度降低,可以使发光元件(发光二极管)led1维持在高外部量子效率(eqe)的工作条件下。

[0067]

此外,在本实施例中,像素电路100另包括脉宽控制信号产生器140。脉宽控制信号产生器140耦接至驱动晶体管td的控制端,并依据脉宽调变信号pwm-g以产生脉宽控制信号pwc。在本实施例中,脉宽控制信号产生器140由晶体管t3所构成。晶体管t3的一端接收参考电压ppo,另一端耦接至驱动晶体管td的控制端,并提供脉宽控制信号pwc。晶体管t3的控制端接收脉宽调变信号pwm-g,并依据脉宽调变信号pwm-g而被导通或断开。其中,参考电压ppo可以为脉冲宽度调变夹止电压(pulse width modulation pinch off voltage)。

[0068]

附带一提的,图1b中激光时间长度调变器130与控制开关120的位置是可以相互交换的,并没有一定的限制。而在本实施例中,控制开关120设置在相对邻近于发光元件led1的位置,激光时间长度调变器130设置在相对远离于发光元件led1的位置。可减少相对高频的激光时间控制信号pwem对发光元件led1的发光效果所造成的影响。

[0069]

在本实施例中,晶体管t1~t3以及驱动晶体管td可以均为p型晶体管。发光二极管led1的阳极耦接至晶体管t2,发光二极管led1的阴极耦接至参考电源vss。

[0070]

以下请参照图3,图3为本发明实施例的像素电路的动作波形图。在多个像素电路的架构中,多个像素电路分别接受激光时间控制信号pwem1~pwem3。在图3的上半部波形中,在第一时间区间t31中,激光时间控制信号pwem1~pwem3可分别在多个第二时间区间t321~t323被致能,并借以调整对应的多个发光元件的亮度。另外,在图3的下半部波形中,通过调长第一时间区间t31为第一时间区间t31

’

,也可在维持发光二极管的外部量子效率(eqe)的前提下,达成调降发光元件所产生的亮度的目的。

[0071]

接着请参照图4a以及图4b,图4a以及图4b分别为本发明实施例的像素电路的不同实施方式的示意图。在图4a中,像素电路400包括驱动晶体管td、控制开关420、激光时间长

度调变器430以及脉宽控制信号产生器440。与图1a、图1b的实施例不相同的,发光元件led1耦接在电源电压vdd以及控制开关420间。此外,像素电路400中,控制开关420由晶体管t42所建构,激光时间长度调变器430由晶体管t41所建构,脉宽控制信号产生器440则由晶体管t43所建构,其中,驱动晶体管td、晶体管t41~t43皆为p型晶体管。

[0072]

在图4b中,像素电路400

’

中的控制开关420、激光时间长度调变器430以及脉宽控制信号产生器440则分别由晶体管t41

’

、t42

’

以及t43

’

所建构,且像素电路400

’

中的驱动晶体管td

’

、晶体管t41

’

~t43

’

则可以皆为n型晶体管。

[0073]

请参照图5,图5为本发明另一实施例的像素电路的示意图。像素电路500包括驱动晶体管td、控制开关520、激光时间长度调变器530以及脉宽控制信号产生器540。其中,在本实施例中,控制开关520包括晶体管t521以及t522。晶体管t521以及t522具有共同耦接至驱动晶体管td的第一端,晶体管t521以及t522并具有分别耦接至发光元件led1、led2的第二端。晶体管t521以及t522另分别受控于激光信号g-em1以及g-em2。

[0074]

对应于控制开关520,激光时间长度调变器530具有晶体管t511以及t512。晶体管t511以及t512具有共同接收电源电压vdd的第一端,并具有共同耦接至驱动晶体管td的第二端。晶体管t511以及t512另分别受控于激光时间控制信号pwem1以及激光时间控制信号pwem2。

[0075]

在当晶体管t521被导通的一个第一时间区间中,晶体管t511可依据激光时间控制信号pwem1以交错的被导通及断开,并解以调控发光元件led1的发光亮度。在另一方面,在当晶体管t522被导通的另一个第一时间区间中,晶体管t512可依据激光时间控制信号pwem2以交错的被导通及断开,并解以调控发光元件led2的发光亮度。

[0076]

在本实施例中,发光元件led1以及led2为可分别发送不同波长光束的发光二极管。

[0077]

附带一提的,脉宽控制信号产生器540可由晶体管t53来建构。

[0078]

请参照图6,图6为本发明图5实施例的像素电路的动作波形图。在当激光信号g-em1被致能时(拉低为相对低的电压电位时),激光时间控制信号pwem1可交错的被禁能(拉高为相对高的电压电位)及致能(拉低为相对低的电压电位),并借以调控发光元件led1的发光亮度。在另一方面,在当激光信号g-em2被致能时(拉低为相对低的电压电位时),激光时间控制信号pwem2可交错的被禁能(拉高为相对高的电压电位)及致能(拉低为相对低的电压电位),并借以调控发光元件led2的发光亮度。

[0079]

接着请参照图7,图7为本发明另一实施例的像素电路的示意图。像素电路700包括驱动晶体管td、控制开关720、激光时间长度调变器730以及脉宽控制信号产生器740。像素电路700与前述实施例的像素电路500的差异在于,控制开关720包括三个晶体管t721~t723,并分别耦接至三个发光元件led1~led3。激光时间长度调变器730则包括分别对应晶体管t721~t723的晶体管t711~t713。

[0080]

本实施例的像素电路700的动作方式与像素电路500相类似,在此不多赘述。发光元件led1~led3发射光束的波长可以不相同。

[0081]

附带一提的,脉宽控制信号产生器740可由晶体管t73来建构。

[0082]

请参照图8,图8为本发明实施例的像素电路的一实施方式的示意图。像素电路800包括驱动晶体管td、控制开关820、激光时间长度调变器830及建构周边电路的晶体管t3~

t7及电容c1~c2。在本实施方式中,驱动晶体管td、控制开关820、激光时间长度调变器830串接在电源电压vdd以及发光元件led1间,发光元件led1并耦接至参考电源vss。此外,晶体管t3的第一端接收显示数据data[m],并受控于重置信号gg-res。晶体管t4的第一端耦接至晶体管t3的第二端,晶体管t4的第二端耦接至驱动晶体管td的第一端(与控制开关820的耦接端点),晶体管t4并受控于栅极驱动信号g2[n]。电容c1耦接在电源电压vdd与驱动晶体管td的控制端间。电容c2则具有第一端以接收时序控制信号tcs,并具有耦接至晶体管t6、t5的第二端。晶体管t5的第一端耦接至电容c2的第二端,晶体管t5的控制端接收栅极驱动信号g1[n]或重置信号res。晶体管t5的第二端耦接至驱动晶体管td的控制端。晶体管t6具有第一端接收显示数据data[m],晶体管t6的第二端耦接至驱动晶体管td的控制端,晶体管t6的控制端耦接至电容c2的第二端。晶体管t7具有第一端接收显示数据data[m],晶体管t7的第二端耦接至驱动晶体管td的第二端,晶体管t7的控制端接收栅极驱动信号g2[n]。

[0083]

本实施方式中,控制开关820、激光时间长度调变器830分别由晶体管t2、t1所建构,并形成一8t2c的电路架构。像素电路800可以设置在具有像素电路阵列的显示面板中,并依据栅极驱动信号g1[n]、g2[n]、时序控制信号tcs以在设定的时序中以驱动发光元件led1。

[0084]

以下请参照图9,图9为本发明实施例的像素电路的另一实施方式的示意图。像素电路900包括驱动晶体管td、控制开关920、激光时间长度调变器930及建构周边电路的晶体管t3~t10及电容c1~c2。电容c1具有第一端接收扫描信号tcs。晶体管t3具有第一端耦接至电容c1的第二端,晶体管t3的第二端接收参考信号ref,晶体管t3并受控于重置信号gg-res。晶体管t4具有第一端接收参考信号ref,晶体管t4的控制端接收重置信号gg-res,晶体管的第二端耦接至驱动晶体管td的控制端。晶体管t5具有第一端耦接至驱动晶体管td的控制端,晶体管t5的第二端耦接至驱动晶体管td的第一端,晶体管t5的控制端接收栅极驱动信号g2[n]。晶体管t6具有第一端耦接至电容c1的第二端,晶体管t6的控制端接收栅极驱动信号g1[n]。晶体管t7具有第一端耦接至晶体管t6的第二端,晶体管t7的第二端耦接至驱动晶体管td的控制端,晶体管t7的控制端接收激光信号gg-em。晶体管t8具有控制端耦接至电容c1的第二端,晶体管t8的第一端耦接至晶体管t6的第二端。晶体管t9具有第一端接收显示数据data[m],晶体管t9的第二端耦接至晶体管t8的第二端,晶体管t9的控制端接收栅极驱动信号g1[n]。晶体管t10具有第一端接收参考电压ppo,晶体管t10的第二端耦接至晶体管t8的第二端,晶体管t10的控制端接收激光信号gg-em。电容c2则具有第一端接收电源电压vdd,电容c2的第二端耦接至驱动晶体管td的控制端。

[0085]

本实施方式中,控制开关920、激光时间长度调变器930分别由晶体管t2、t1所建构,并形成一11t2c的电路架构。与图8的实施方式相类似,像素电路900可以设置在具有像素电路阵列的显示面板中,并依据栅极驱动信号g1[n]、g2[n]、时序控制信号tcs以在设定的时序中以驱动发光元件led1。

[0086]

请参照图10,图10为本发明一实施例的显示面板的示意图。显示面板1000包括多个像素电路p11~p23。其中,像素电路p11~p13形成第一像素列pc1,像素电路p21~p23则形成第二像素列pc2。第一像素列pc1与第二像素列pc2交错排列。此外,像素电路p11~p23可应用前述多个实施例以及实施方式的任一像素电路来实施,没有固定的限制。值得一提的,在第一像素列pc1中的像素电路p11~p13中,像素电路p11~p13分别具有的激光时间长

度调变器1011~1013共同受控于激光时间控制信号pwem1。在第二像素列pc2中的像素电路p21~p23中,像素电路p21~p23分别具有的激光时间长度调变器1021~1023则共同受控于另一激光时间控制信号pwem2。

[0087]

在此请注意,请同步参照图10以及图11,其中图11为本发明图10实施例的激光时间控制信号的动作波形图。在本实施例中激光时间控制信号pwem1以及激光时间控制信号pwem2可以在相同的第一时间区间中进行转态动作。然值得注意的,中激光时间控制信号pwem1以及激光时间控制信号pwem2的被致能时间区间ten1、ten2(被拉低为相对低电压电位的时间区间)是依序发生且不相互重叠的。也就是说,在相同的显示面板1000上,像素电路p11~p13提供驱动电流至对应的发光元件led11~led13的时间区间,与像素电路p21~p23提供驱动电流至对应的发光元件led21~led23的时间区间是错开的。如此一来,在不改变显示面板1000的显示画质的前提下,显示面板1000在同一时间点上所产生的总电流量可以被降低,并有效减低电源供应上的负担,且降低所可能产生的电磁干扰。

[0088]

附带一提的,显示面板1000也可通过三个(或三个以上)依序致能的激光时间控制信号,来使显示面板1000上的发光元件可区分为三组(或更多组)的方式,来在不同的时间区间中被点亮,并更有效降低显示面板1000在在同一时间点上所产生的总电流量。

[0089]

请参照图12a,图12a为本发明另一实施例的像素电路的示意图。像素电路1200包括控制开关1220以及1230、驱动晶体管td以及建构周边电路的晶体管t1~t5以及电容c1、c2。控制开关1220以及1230则分别由晶体管t7、t6所建构。像素电路1200用以驱动发光元件led1。

[0090]

在电路架构的细节上,控制开关1230具有第一端接收电源电压vdd,并受控于激光信号gg-em。晶体管td具有第一端耦接至控制开关1230的第二端。控制开关1220耦接在驱动晶体管td的第二端与发光元件led间,控制开关1230并受控于激光信号gg-em。电容c1的一端接收电源电压vdd,另一端耦接至驱动晶体管td的控制端。晶体管t1具有第一端接收显示数据data[m],晶体管t1的第二端耦接至驱动晶体管td的控制端,晶体管t1的控制端接收重置信号gg-res。晶体管t2具有第一端耦接至晶体管t1的第二端,晶体管t2的第二端耦接至驱动晶体管td的第二端,晶体管t2的控制端接收一栅极驱动信号g2[n]。晶体管t3具有第一端以接收显示数据data[m],晶体管t3的第二端耦接至驱动晶体管td的控制端。电容c2的一端接收时序控制信号tcs,另一端耦接至晶体管t3的控制端。晶体管t4具有第一端耦接至晶体管t3的控制端,晶体管t4的第二端耦接至驱动晶体管td的控制端,晶体管t4的控制端接收重置信号res或栅极驱动信号g1[n]。晶体管t5具有第一端接收显示数据data[m],晶体管t5的第二端耦接至驱动晶体管td的第一端,晶体管t5的控制端接收栅极驱动信号g2[n]。

[0091]

在动作方面,请同步参照图12b为的本发明实施例的像素电路1200的动作波形图。在第一驱动阶段ts0中,时序控制信号tcs为一持续下降的斜波,晶体管t3、t6、t7以及驱动晶体管td被导通,而其余的晶体管t1、t2、t4、t5均被断开。此时,信号gp随时序控制信号tcs持续下降,而显示数据data[m]的电压电位被设定为脉冲宽度调变夹止电压(例如参考电压ppo),并在时序控制信号tcs的电压足够低时,通过晶体管t3传送至驱动晶体管td的控制端以使驱动信号ga上升。如此,驱动晶体管td的闸-源极间的电压差可以大于0。

[0092]

接着,在第二驱动阶段ts1,通过重置信号res以及gg-res以使晶体管t1、t4被导通,并通过激光信号gg-em以使晶体管t6、t7被切断。如此一来,电容c2的第二端(与晶体管

t4的耦接端点)可通过晶体管t1、t4形成一回路。通过使显示数据data[m]为例如为参考电源vss的电压电位,可使信号gp以及驱动信号ga的电压值被拉低。此时时序控制信号tcs可以为一相对低的电压tcs_l(例如等于参考电源vss)。

[0093]

在第三驱动阶段ts2中,晶体管t1变更为被切断的状态。显示数据data[m]提供发光元件led1的脉宽调变数据vp1,并在栅极驱动信号g1[n]被拉低时,通过晶体管t3、t4被写入至电容c2中。

[0094]

接着,在第四驱动阶段ts3中,晶体管t4被切断。时序控制信号tcs在一时间点被拉高至相对高的电压电位tcs_h,以使电容c2执行电压泵高(pumping up)的操作。如此一来,电容c2第二端上的信号gp的电压电位实质上可以等于vp1-vth+tcs_h。其中,vp-vth为实质写入至电容c2的电压电位,vth为晶体管t4的导通电压。

[0095]

在第五驱动阶段ts4中,显示数据data[m]的电压电位再次被设定例如为电压v0,并使晶体管t1导通,以通过被导通的晶体管t1以对电容c1以及驱动晶体管td的驱动端上的驱动信号ga进行重置动作。

[0096]

在第六驱动阶段ts5中,晶体管t1变更为被切断,晶体管t2、t5变更为被导通,此时晶体管t5所接收的显示数据data[m]为振幅调变数据vp2,并在栅极驱动信号g2[n]被拉低时,通过被导通的晶体管t5、t2而被写入至电容c1以及驱动晶体管td的控制端。

[0097]

在第七驱动阶段ts6中,晶体管t2、t5变更为被切断,晶体管t6、t7再次被导通。如此一来,驱动晶体管td的控制端依据电容c1、c2上的电压来产生驱动信号,并借以驱动发光元件led1发光。

[0098]

在此请注意,在本实施例中,通过设置开关电路1220,可以阻隔发光元件led1的寄生电容对像素电路1200产生的影响,并且,发光元件led1的阴极端接收稳定的直流参考电源vss,可使发光元件led1可接收相对高的驱动信号的驱动电流。此外,显示数据data[m]中载入关于扫描动作的部分命令,可提升像素电路1200的电压设定效能。整体来说,像素电路1200仅需要8个晶体管两个电容来建构,也可经减少需要的电路元件的数量,提升价格的竞争力。

[0099]

附带一提的,本实施例中的晶体管t1~t5以及驱动晶体管td可均由p型的晶体管的建构。

[0100]

以下请参照图13,图13为本发明另一实施例的像素电路的示意图。图13实施例的像素电路1300的电路架构与动作方式与像素电路1200相类似。差异点在于,图13实施例中的晶体管t1~t5由为n型晶体管来建构。其中,像素电路1300的设计重点在于产生驱动信号(电流)的电路由p型晶体管所建构,而用以锁结驱动晶体管td控制端上的电压的相关晶体管t1、t2、t4、t5则由n型晶体管来建构。本实施例通过互补式晶体管的设计结构,可有效减低驱动晶体管td的控制端上所需要的电压电位,减低驱动晶体管td所可能产生的漏电现象,并可优化电容值的设计,并达成高解析度设计的目的。

[0101]

综上所述,本发明一实施例中的像素电路可通过激光时间长度调变器的设置,来在激光时间区间中,进一步针对发光元件的发光亮度进行调整。借此,在维持发光元件的外部量子效率的前提下,也可达成低亮度显示的效果。在本发明另一实施例中,则提供可简化电路架构的像素电路,同样可以提升像素电路的工作效能。

[0102]

当然,本发明还可有其它多种实施例,在不背离本发明精神及其实质的情况下,熟

悉本领域的技术人员当可根据本发明作出各种相应的改变和变形,但这些相应的改变和变形都应属于本发明所附的权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1