显示驱动器以及显示装置的制作方法

1.本发明涉及一种根据图像信号来驱动显示屏的显示驱动器、以及包含所述显示驱动器的显示装置。

背景技术:

2.在液晶显示装置中包含液晶屏,并且包含:栅极驱动器,对形成于所述液晶屏的多个扫描线进行驱动;以及源极驱动器,对在所述液晶屏中与各扫描线交叉的多个信号线进行驱动。

3.作为所述源极驱动器,已知包含下述部分的源极驱动器:电阻分压电路、灰阶放大器、多个模数转换器(digital analog convertor,dac)电路、以及作为外部端子的多个输出端子(例如参照专利文献1)。

4.电阻分压电路及灰阶放大器(称为灰阶电压生成电路)通过将电源电压分压从而生成与64灰阶的亮度分别对应的64个电压,并将这些电压以64个灰阶信号的形式经由灰阶信号总线配线而供给于各dac电路。各dac电路从经由灰阶信号总线配线所接收的64个灰阶信号中选择与显示数据对应的一个,并将其经由与自身对应的输出端子而输出。各dac电路在源极驱动器内,配置于与并排配置成一列的输出端子分别对应的位置。

5.现有技术文献

6.专利文献

7.专利文献1日本专利特开2009-69287号公报

技术实现要素:

8.发明所要解决的问题

9.此外,这种源极驱动器中,有时负荷伴随每一水平扫描期间的显示数据的变化而变动,导致各灰阶信号的电平暂时下降(或增加),接着逐渐增加(或下降)而回到各自的所需电平。

10.此时,灰阶信号的电平下降(或增加)后至回到所需电平时,产生延迟,此延迟是由与灰阶电压生成电路及dac电路间的配线长对应的配线电阻、及dac电路所含的最终段的输出放大器的输入电容所引起。由此,对于配置于距灰阶电压生成电路远的位置的、dac电路(称为远端dac)的输出信号来说,与配置于距灰阶电压生成电路近的位置的、dac电路(称为近端dac)的输出信号相比,产生更大的延迟。

11.因此,若伴随近年来的显示装置的大画面化及高精细化而一水平扫描期间变短,则有时在各水平扫描期间的结束时间点,接收了来自近端dac的输出信号的、液晶屏内的信号线上的电平达到所需电平,但在接收了来自远端dac的输出信号的、液晶屏内的信号线上,其电平未达到所需电平。由此,负责液晶屏的画面中央区域的显示的信号线上的信号电平、与负责画面的左端及右端区域的显示的信号线上的信号电平产生电平差。因此,在所述电平差成为一灰阶以上的情况下,可能在画面中央区域、与画面左端及右端区域之间在视

觉上产生色差。

12.因此,本发明的目的在于提供一种显示驱动器以及显示装置,可显示抑制了这种色差的高品质的高精细图像。

13.解决问题的技术手段

14.本发明的显示驱动器根据加载信号而导入基于图像信号的多个像素数据片,并根据所导入的所述多个像素数据片,生成对显示屏的多个源极线施加的多个像素驱动电压,且所述显示驱动器包括:总线配线,包含多个配线;灰阶电压生成电路,生成以m(m为2以上的整数)灰阶来表示亮度电平的m个灰阶电压,并将所述m个灰阶电压分别施加于属于所述总线配线的m个配线各自的一端与另一端之间的中间部;多个解码器,沿着所述m个配线而并排配置,分别经由所述m个配线而接收所述m个灰阶电压,根据所述像素数据片从所述m个灰阶电压中选择一个并输出;多个输出放大器,将从所述多个解码器输出的电压分别个别地放大,生成为所述多个像素驱动电压;第一灰阶间短路电路,根据所述加载信号,使所述m个配线各自的所述一端彼此短路;以及第二灰阶间短路电路,根据所述加载信号,使所述m个配线各自的所述另一端彼此短路。

15.而且,本发明的显示驱动器根据加载信号来导入基于图像信号的多个像素数据片,并根据所导入的所述多个像素数据片,生成对显示屏的多个源极线施加的多个像素驱动电压,且所述显示驱动器包括:第一总线配线及第二总线配线,分别包含多个配线;灰阶电压生成电路,生成以m(m为2以上的整数)灰阶来表示亮度电平的m个灰阶电压,将所述m个灰阶电压分别施加于属于所述第一总线配线的m个配线各自的一端与另一端之间的中间部,并且分别施加于属于所述第二总线配线的m个配线各自的一端与另一端之间的中间部;第一解码器~第r(r为2以上的整数)解码器,沿着所述第一总线配线而并排配置,分别经由属于所述第一总线配线的所述m个配线而接收所述m个灰阶电压,根据所述像素数据片从所述m个灰阶电压中选择一个并输出;第(r+1)解码器~第n解码器,沿着所述第二总线配线而并排配置,分别经由属于所述第二总线配线的所述m个配线而接收所述m个灰阶电压,根据所述像素数据片从所述m个灰阶电压中选择一个并输出;输出放大器,将从所述第一解码器~第r解码器及所述第(r+1)解码器~第n解码器输出的电压分别个别地放大,生成为n个所述像素驱动电压;第一灰阶间短路电路,根据所述加载信号,使属于所述第一总线配线的所述m个配线各自的所述一端彼此短路;第二灰阶间短路电路,根据所述加载信号,使属于所述第一总线配线的所述m个配线各自的所述另一端彼此短路;第三灰阶间短路电路,根据所述加载信号,使属于所述第二总线配线的所述m个配线各自的所述一端彼此短路;以及第四灰阶间短路电路,根据所述加载信号,使属于所述第二总线配线的所述m个配线各自的所述另一端彼此短路。

16.而且,本发明的显示驱动器根据加载信号来导入基于图像信号的多个像素数据片,并根据所导入的所述多个像素数据片,生成对显示屏的多个源极线施加的多个像素驱动电压,且所述显示驱动器包括:总线配线,包含m个(m为2以上的整数)配线;灰阶电压生成电路,生成以所述m个灰阶来表示亮度电平的灰阶电压,并将所述m个灰阶电压分别施加于所述m个配线各自的一端与另一端之间;多个解码器,沿着所述m个配线而并排配置,分别经由所述m个配线而接收所述m个灰阶电压,根据所述像素数据片从所述m个灰阶电压中选择一个并输出;多个输出放大器,将从所述多个解码器输出的电压分别个别地放大,生成为所

述多个像素驱动电压;以及灰阶间短路电路,根据所述加载信号,使所述m个配线各自的所述一端彼此及所述另一端彼此的至少一者短路。

17.本发明的显示装置包含:显示屏,具有多个源极线;以及显示驱动器,根据加载信号来导入基于图像信号的多个像素数据片,并根据所导入的所述多个像素数据片而生成多个像素驱动电压,分别施加于所述显示屏的多个源极线,且所述显示驱动器包括:总线配线,包含多个配线;灰阶电压生成电路,生成以m(m为2以上的整数)灰阶来表示亮度电平的m个灰阶电压,并将所述m个灰阶电压分别施加于属于所述总线配线的m个配线各自的一端与另一端之间的中间部;多个解码器,沿着所述m个配线而并排配置,分别经由所述m个配线而接收所述m个灰阶电压,根据所述像素数据片从所述m个灰阶电压中选择一个并输出;多个输出放大器,将从所述多个解码器输出的电压分别个别地放大,生成为所述多个像素驱动电压;第一灰阶间短路电路,根据所述加载信号,使所述m个配线各自的所述一端彼此短路;以及第二灰阶间短路电路,根据所述加载信号,使所述m个配线各自的所述另一端彼此短路。

18.而且,本发明的显示装置包含:显示屏,具有多个源极线;以及显示驱动器,根据加载信号来导入基于图像信号的多个像素数据片,并根据所导入的所述多个像素数据片而生成多个像素驱动电压,分别施加于所述显示屏的多个源极线,且所述显示驱动器包括:第一总线配线及第二总线配线,分别包含多个配线;灰阶电压生成电路,生成以m(m为2以上的整数)灰阶来表示亮度电平的m个灰阶电压,将所述m个灰阶电压分别施加于属于所述第一总线配线的m个配线各自的一端与另一端之间的中间部,并且分别施加于属于所述第二总线配线的m个配线各自的一端与另一端之间的中间部;第一解码器~第r(r为2以上的整数)解码器,沿着所述第一总线配线而并排配置,分别经由属于所述第一总线配线的所述m个配线而接收所述m个灰阶电压,根据所述像素数据片从所述m个灰阶电压中选择一个并输出;第(r+1)解码器~第n解码器,沿着所述第二总线配线而并排配置,分别经由属于所述第二总线配线的所述m个配线而接收所述m个灰阶电压,根据所述像素数据片从所述m个灰阶电压中选择一个并输出;输出放大器,将从所述第一解码器~第r解码器及所述第(r+1)解码器~第n解码器输出的电压分别个别地放大,生成为n个所述像素驱动电压;第一灰阶间短路电路,根据所述加载信号,使属于所述第一总线配线的所述m个配线各自的所述一端彼此短路;第二灰阶间短路电路,根据所述加载信号,使属于所述第一总线配线的所述m个配线各自的所述另一端彼此短路;第三灰阶间短路电路,根据所述加载信号,使属于所述第二总线配线的所述m个配线各自的所述一端彼此短路;以及第四灰阶间短路电路,根据所述加载信号,使属于所述第二总线配线的所述m个配线各自的所述另一端彼此短路。

19.发明的效果

20.本发明的显示驱动器包含:灰阶电压生成电路,生成以m(m为2以上的整数)灰阶来表示亮度电平的m个灰阶电压,并分别施加于m条配线各自的中间部;以及多个解码器,沿着m条配线而并排配置,分别根据像素数据片从经由所述m条配线而接收的m个灰阶电压中选择一个并输出。

21.此处,所述显示驱动器中,根据进行多个像素数据片的导入的加载信号,来使m条配线各自的一端彼此短路,并且使所述m条配线各自的另一端彼此短路。

22.通过所述短路处理,而缩短配置于距灰阶电压生成电路的配线长长的位置的解码

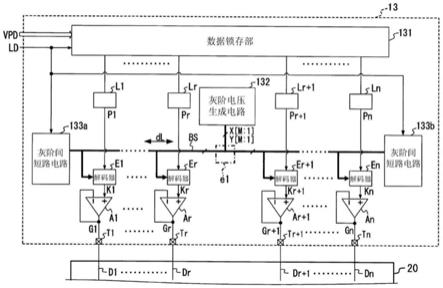

器中的延迟时间,即,缩短负责画面左端及右端区域的显示的解码器中的延迟时间。因此,配置于所述配线长短的位置的解码器也就是负责画面中央区域的显示的解码器的延迟时间、与负责画面左端及右端区域的显示的解码器的延迟时间的差变小。

23.由此,可在水平扫描期间的结束时间点,使负责显示屏的画面中央区域的显示的源极线的电压、与负责画面左端及右端区域的显示的源极线的电压的差减少至小于一灰阶的电压。

24.因此,根据本发明,可提供一种抑制了色差的高品质的显示图像。

附图说明

25.图1为表示包含本发明的源极驱动器13的显示装置100的结构的框图。

26.图2为表示加载信号ld的波形图。

27.图3为表示源极驱动器13的内部结构的电路图。

28.图4为表示灰阶电压生成电路132的输出段的结构的电路图。

29.图5为表示总线配线bs的中间部e1的连接形态的一例的图。

30.图6为表示灰阶间短路电路133a的电路图。

31.图7为表示灰阶间短路电路133b的电路图。

32.图8为表示未设置灰阶间短路电路的情况下的、一水平扫描期间内的各信号的波形的波形图。

33.图9为表示设有灰阶间短路电路的情况下的、一水平扫描期间内的各信号的波形的波形图。

34.图10为表示源极驱动器13的内部结构的另一例的电路图及配置图。

35.符号的说明

36.13:源极驱动器

37.20:显示屏

38.132:灰阶电压生成电路

39.133a、133b:灰阶间短路电路

40.a1~an:输出放大器

41.bs:总线配线

42.e1~en:解码器

43.qn、qp:开关元件

具体实施方式

44.以下,一方面参照附图一方面对本发明的实施例进行详细说明。

45.图1为表示包含本发明的显示驱动器的显示装置100的结构的框图。如图1所示,显示装置100具有驱动控制部11、栅极驱动器12、源极驱动器13、及例如包含液晶屏的显示屏20。

46.在显示屏20,形成有分别沿二维画面的水平方向伸长的m个(m为2以上的整数)水平扫描线s1~sm、以及分别沿二维画面的垂直方向伸长的n个(n为2以上的整数)源极线d1~dn。进而,在水平扫描线s及源极线d的各交叉部的区域(由虚线包围的区域),形成有成为

像素的显示单元pc。

47.驱动控制部11接收输入图像信号vs,基于所述输入图像信号vs而生成水平同步信号,并将其供给于栅极驱动器12。而且,驱动控制部11基于输入图像信号vs而生成图像数据信号vpd,并将其供给于源极驱动器13,所述图像数据信号vpd针对每个像素而包含以例如6位(bit)的数据来表示所述像素的亮度电平的、像素数据pd的系列。进而,驱动控制部11生成与水平同步信号对应的二值的加载信号ld,并将其供给于源极驱动器13。

48.图2为表示加载信号ld的一例的时间图(time chart)。

49.如图2所示,驱动控制部11生成下述脉冲信号作为加载信号ld,即:在各水平扫描期间,分别在其开头从例如逻辑电平0的状态过渡至逻辑电平1,并以规定期间w1维持所述逻辑电平1的状态。

50.栅极驱动器12与从驱动控制部11供给的水平同步信号同步而生成栅极脉冲,并将其依次施加于显示屏20的各水平扫描线s1~sm。

51.源极驱动器13基于图像数据信号vpd而生成与显示屏20的源极线d1~源极线dn分别对应的像素驱动信号g1~像素驱动信号gn,并分别个别地供给于对应的源极线d1~源极线dn。此外,源极驱动器13为单一的半导体芯片,或分割为多个半导体芯片而形成。

52.图3为表示源极驱动器13的内部结构的框图。

53.如图3所示,源极驱动器13包含数据锁存部131、灰阶电压生成电路132、灰阶间短路电路133a及灰阶间短路电路133b、解码器e1~解码器en以及输出放大器a1~输出放大器an。

54.数据锁存部131根据加载信号ld,将图像数据信号vpd所含的像素数据pd的系列以一水平扫描线程度导入,即,以n个为单位而导入。另外,数据锁存部131将所导入的n个像素数据pd分别供给于电平位移电路l1~电平位移电路ln。

55.电平位移电路l1~电平位移电路ln对n个像素数据pd各自的信号电平的振幅进行电平位移至解码器e1~解码器en中可使用的电平,将所得的n个像素数据片作为像素数据p1~像素数据pn而分别供给于解码器e1~解码器en。

56.灰阶电压生成电路132分别生成具有正极性的电压值的m(m为2以上的整数)个灰阶电压y[1]~y[m],所述正极性的电压值符合相对于显示屏20的伽马特性的倒伽马特性。进而,灰阶电压生成电路132分别生成具有负极性的电压值的m个灰阶电压x[1]~x[m],所述负极性的电压值符合所述倒伽马特性。此外,下文中,将灰阶电压y[1]~y[m]也表述作灰阶电压y[m:1],将灰阶电压x[1]~x[m]也表述作灰阶电压x[m:1]。

[0057]

图4为表示灰阶电压生成电路132的输出段的结构的电路图。

[0058]

如图4所示,灰阶电压生成电路132包含伽马缓冲器gb1~伽马缓冲器gb4、及梯形电阻ldr。

[0059]

各伽马缓冲器gb1~gb4例如包含操作放大器,如图4所示,包含自身的反转输入端子(-)与自身的输出端子y连接的、所谓电压跟随器电路(voltage follower circuit)。伽马缓冲器gb1~伽马缓冲器gb4分别具有以下的大小关系,且且在各自的非反转输入端子(+)个别地接收基准电压vg1~基准电压vg4,所述基准电压vg1~基准电压vg4具有符合所述倒伽马特性的电压值。

[0060]

vg1>vg2>vg3>vg4

[0061]

各伽马缓冲器gb1~gb4的输出端子y如图4所示,分别连接于梯形电阻ldr的四处的不同连接点。根据所述结构,梯形电阻ldr按照所述倒伽马特性将基准电压vg1及基准电压vg2间分压为m个,生成m个电压作为正极性的灰阶电压y[m:1]。而且,梯形电阻ldr按照所述倒伽马特性将基准电压vg4及基准电压vg3间分压为m个,生成m个电压作为负极性的灰阶电压x[m:1]。

[0062]

灰阶电压生成电路132将所述m个正极性的灰阶电压y[m:1]、及m个负极性的灰阶电压x[m:1],经由包含2m个配线的总线配线bs而供给于各解码器e1~en。

[0063]

各解码器e1~en每隔规定期间,交替选择正极性的灰阶电压y[m:1]与负极性的灰阶电压x[m:1]。此处,各解码器e1~解码器en从所选择的m个灰阶电压中,选择与自身所接收的像素数据p所示的亮度电平对应的至少一个灰阶电压。解码器e1~解码器en将具有各自选择的灰阶电压的灰阶信号k1~灰阶信号kn供给于输出放大器a1~输出放大器an。

[0064]

各输出放大器a1~an例如为自身的输出端子与自身的反转输入端子(-)连接的、包含所谓操作放大器的电压跟随器电路。输出放大器a1~输出放大器an在各自的非反转输入端子(+)接收从解码器e1~解码器en输出的灰阶信号k1~灰阶信号kn,将与各自所接收的灰阶信号相应的电流输出至自身的输出端子,由此生成与灰阶电压对应的像素驱动信号g1~像素驱动信号gn。所述像素驱动信号g1~像素驱动信号gn经由形成有源极驱动器13的半导体芯片的外部端子t1~外部端子tn而输出,供给于显示屏20的源极线d1~源极线dn。

[0065]

此外,图3所示的电路图中,关于解码器e1~解码器en、输出放大器a1~输出放大器an、外部端子t1~外部端子tn、总线配线bs、灰阶电压生成电路132、灰阶间短路电路133a及灰阶间短路电路133b,表示半导体芯片内的配置形态的一例。

[0066]

即,在半导体芯片内,如图3所示,解码器e1~解码器en及输出放大器a1~输出放大器an是沿着总线配线bs而并排配置,所述总线配线bs包含沿着方向dl分别伸长的2m条配线。

[0067]

如图3所示,灰阶电压生成电路132针对沿着方向dl伸长的总线配线bs上的中间部,即,针对属于所述总线配线bs的2m条配线各自的一端与另一端之间的中间部e1,施加灰阶电压y[m:1]及灰阶电压x[m:1]。此外,如图3所示,中间部e1优选位于由解码器e1~解码器en中配置于中央的解码器er与解码器er+1之间所夹持的区域内的总线配线bs上。

[0068]

图5为详细表示总线配线bs及所述中间部e1处的连接形态的图。

[0069]

如图5所示,总线配线bs包含:配线yl[1]~配线yl[m],用于将灰阶电压y[1]~y[m]传输至各解码器e1~en;以及配线xl[1]~配线xl[m],用于将灰阶电压x[1]~灰阶电压x[m]传输至各解码器e1~en。即,灰阶电压生成电路132将自身所生成的正极性的灰阶电压y[1]~灰阶电压y[m]在所述中间部e1中分别施加于总线配线bs所包含的配线yl[1]~配线yl[m]。进而,灰阶电压生成电路132将自身所生成的负极性的灰阶电压x[1]~灰阶电压x[m]在所述中间部e1中分别施加于总线配线bs所包含的配线xl[1]~配线xl[m]。

[0070]

而且,如图3所示,各解码器e1~en经由在分别对应的位置从所述总线配线bs分支的2m条配线,接收正极性的灰阶电压y[m:1]及负极性的灰阶电压x[m:1]。

[0071]

此外,在所述总线配线bs的一端,如图3所示那样形成有灰阶间短路电路133a,在所述总线配线bs的另一端形成有灰阶间短路电路133b。

[0072]

图6为表示灰阶间短路电路133a的内部结构的电路图。

[0073]

如图6所示,灰阶间短路电路133a包含电平位移器lsa、正极短路开关部swp及负极短路开关部swn。

[0074]

电平位移器lsa生成加载信号lda,此加载信号lda是将表示二值(逻辑电平0或1)的加载信号ld的电压电平,进行电平位移至可对正极短路开关部swp及负极短路开关部swn的各开关进行通断(on-off)控制的电压电平而成。进而,电平位移器lsa生成使加载信号lda的逻辑电平反转的信号作为加载信号ldaq。

[0075]

正极短路开关部swp连接于总线配线bs中的、分别传输正极性的灰阶电压y[1]~灰阶电压y[m]的配线yl[1]~配线yl[m]各自的一端(左端)。正极短路开关部swp包含多个开关元件qp,所述多个开关元件qp根据加载信号ldaq,将配线yl[1]~配线yl[m]各自的一端以5个为单位相互电连接。各开关元件qp在加载信号ldaq表示例如逻辑电平1的情况下成为断开状态,另一方面,在表示逻辑电平0的情况下成为接通状态,将配线yl[1]~配线yl[m]中邻接的配线彼此电连接。

[0076]

负极短路开关部swn连接于总线配线bs中的、分别传输负极性的灰阶电压x[1]~灰阶电压x[m]的配线xl[1]~配线xl[m]各自的一端(左端)。负极短路开关部swn包含多个开关元件qn,所述多个开关元件qn根据加载信号lda,将配线xl[1]~配线xl[m]各自的一端以5个为单位相互电连接。各开关元件qn在加载信号lda表示例如逻辑电平0的情况下成为断开状态,另一方面,在表示逻辑电平1的情况下成为接通状态,将配线xl[1]~配线xl[m]中邻接的配线彼此电连接。

[0077]

图7为表示灰阶间短路电路133b的内部结构的电路图。

[0078]

如图7所示,灰阶间短路电路133b包含电平位移器lsb、正极短路开关部swq及负极短路开关部swj。

[0079]

此外,电平位移器lsb与图6所示的电平位移器lsa具有相同结构。而且,正极短路开关部swq与图6所示的正极短路开关部swp为相同结构,负极短路开关部swj与图6所示的负极短路开关部swn具有相同结构。

[0080]

因此,关于电平位移器lsb的动作、与加载信号ldbq相应的正极短路开关部swq的动作、及与加载信号ldb相应的负极短路开关部swj的动作,省略其说明。

[0081]

此处,在源极驱动器13中,通过设置灰阶间短路电路133a及灰阶间短路电路133b,从而针对配置于距灰阶电压生成电路132的总线配线bs的配线长长的位置的解码器e,相对于配置于所述配线长短的位置的解码器e,而大幅度地缩短所述解码器中的延迟时间。

[0082]

以下,关于利用灰阶间短路电路133a、灰阶间短路电路133b的解码器的高速化动作,取距灰阶电压生成电路132的配线长达到最长的解码器e1及解码器en、以及所述配线长达到最短的解码器er及解码器er+1为例,参照图8及图9进行说明。

[0083]

图8及图9为表示解码器e1、解码器er、解码器er+1及解码器en从正极性最小的灰阶电压y[1]的选择状态过渡至最大的灰阶电压y[m]的选择状态时的与解码器e1、解码器er、解码器er+1及解码器en有关的各信号在一水平扫描期间内的波形的波形图。

[0084]

此外,图8表示未设置灰阶间短路电路(133a、133b)的情况下的信号波形,图9表示设有所述灰阶间短路电路的情况下的信号波形。

[0085]

首先,在未设置灰阶间短路电路的情况下,如图8所示,从解码器e1及解码器en输出的灰阶信号k1及灰阶信号kn与从解码器er及解码器er+1输出的灰阶信号kr及灰阶信号

kr+1相比,缓慢地从灰阶电压y[1]的状态推移至灰阶电压y[m]的状态。

[0086]

即,如图8所示,灰阶信号k1、灰阶信号kr、灰阶信号kr+1及灰阶信号kn从灰阶电压y[1]的状态即时间点t0开始增加,在其后的时间点t1,灰阶信号kr及灰阶信号kr+1先达到灰阶电压y[m]的状态。接着,在从所述时间点t1延迟的时间点t2,灰阶信号k1及灰阶信号kn达到灰阶电压y[m]的状态。

[0087]

此时,接收了所述灰阶信号kr及所述灰阶信号kr+1的输出放大器ar及输出放大器ar+1随着灰阶信号kr及灰阶信号kr+1的电压增加,生成如图8所示那样增加的像素驱动信号gr及像素驱动信号gr+1。输出放大器ar及输出放大器ar+1将这些像素驱动信号gr及gr+1分别经由输出端子tr及输出端子tr+1而施加于显示屏20的源极线dr及源极线dr+1。源极线dr及源极线dr+1各自的电压(以下称为电压ur及电压ur+1)也对应于这些像素驱动信号gr及gr+1而增加。但是,由于所述源极线dr及源极线dr+1的配线电阻及寄生电容的影响,所述电压增加的速度较像素驱动信号gr及像素驱动信号gr+1更慢。

[0088]

此处,接收了较灰阶信号kr及灰阶信号kr+1更缓慢地增加的灰阶信号k1及灰阶信号kn的输出放大器a1及输出放大器an生成较像素驱动信号gr及像素驱动信号gr+1更缓慢地增加的像素驱动信号g1及像素驱动信号gn。输出放大器a1及输出放大器an将这些像素驱动信号g1及gn分别经由输出端子t1及输出端子tn而施加于显示屏20的源极线d1及源极线dn。源极线d1及源极线dn各自的电压(以下称为电压u1及电压un)也对应于这些像素驱动信号g1及gn而增加。但是,由于所述源极线d1及源极线dn的配线电阻及寄生电容的影响,所述电压增加的速度较像素驱动信号g1及像素驱动信号gn更慢。

[0089]

因此,在一水平扫描期间的结束时间点,负责显示屏20的画面中央区域的显示的源极线dr及源极线dr+1的电压ur及电压ur+1、与负责画面左端及右端区域的显示的源极线d1及源极线dn的电压u1及电压un产生图8所示的电压差vt1。此时,一水平扫描期间的结束时间点的状态作为最终的显示图像而被看到,因而在所述电压差vt1成为一灰阶以上的情况下,在显示屏20的画面中央区域、与画面左端及右端区域之间产生色差。

[0090]

另一方面,在设有灰阶间短路电路的情况下,如图9所示,所述灰阶间短路电路所含的图6及图7所示的所有开关元件qp及qn在水平扫描期间的开头的规定期间w1的期间中,根据逻辑电平1的加载信号ld而成为接通状态。此外,在所述规定期间w1以外的期间中,图6及图7所示的所有开关元件qp及qn根据逻辑电平0的加载信号ld而成为断开状态。因此,在水平扫描期间的开头的规定期间w1的期间中,总线配线bs所含的配线yl[m:1]及配线xl[m:1]成为以5条为单位短路的状态,在所述规定期间w1以外的期间中分别成为经开放的状态。

[0091]

由此,针对经各开关元件qp(qn)短路的每5条配线yl(xl),与施加于各配线yl(xl)的灰阶电压y(x)对应的电荷经由开关元件qp(qn)而合成。

[0092]

此时,针对每5条配线yl(xl)经由开关元件qp(qn)合成的电荷经由各配线yl(xl)而分别流入解码器e1~解码器en。此期间中,各解码器e1~en处于下述状态,即:从经由各配线yl(xl)而接收的2m个灰阶电压中,选择与对自身供给的像素数据p相应的一个。即,各解码器e1~en处于下述状态,即:将2m个配线(yl、xl)中的一个配线连接于输出放大器a的非反转输入端子(+)。

[0093]

因此,各解码器e1~en在图8所示的规定期间w1之间,经由所述选择的一个配线,将合成电荷供给于输出放大器a的非反转输入端子(+),所述合成电荷是将与所述配线处于

短路状态的合计5个配线上的电荷合成而成。通过此种合成电荷的补充,从而对输出放大器a的输入电容进行充放电。因此,与仅利用一个配线上的电荷对输出放大器a的输入电容进行充放电的情况相比,灰阶信号k1~灰阶信号kn及像素驱动信号g1~像素驱动信号gn的上升或下降速度变得高速,灰阶信号k1~灰阶信号kn及像素驱动信号g1~像素驱动信号gn的延迟时间变短。

[0094]

此外,如图3所示,来自5个配线的合成电荷的补充是从设于总线配线bs的两端的灰阶间短路电路133a(133b)向总线配线bs的中间部e1进行。此时,从灰阶间短路电路133a(133b)到各解码器e1~en的总线配线bs(包含yl、xl)的配线长越长,由配线电阻所引起的合成电荷的损失越大。即,对距灰阶间短路电路133a(133b)的配线长短的解码器e1(en)所补充的合成电荷的量,多于对所述配线长长的解码器er(er+1)所补充的合成电荷的量。

[0095]

由此,如图9所示,从距灰阶间短路电路133a(133b)的配线长达到最长的解码器er(er+1)输出的灰阶信号kr(kr+1)以与图8所示的情况大致相同的速度上升,在时间点t1后立即达到灰阶电压y[m]。另一方面,从所述配线长达到最短的解码器e1(en)输出的灰阶信号k1(kn)以较图8所示的情况更高速的速度上升,在较时间点t2更早的时间点t2a达到灰阶电压y[m]。

[0096]

即,通过使在总线配线bs的两端邻接的配线彼此短路,从而缩短灰阶信号k1(kn)所产生的延迟时间、与灰阶信号kr(kr+1)所产生的延迟时间的差。重要的是,通过缩短配置于距灰阶电压生成电路132的总线配线bs的配线长长的位置的解码器(例如e1、en)的延迟时间,从而减小与配置于所述配线长短的位置的解码器(例如er、er+1)的延迟时间的差。

[0097]

因此,如图9所示,在一水平扫描期间的结束时间点,负责画面中央区域的显示的源极线dr(dr+1)的电压ur(ur+1)、与负责画面左端(右端)区域的显示的源极线d1(dn)的电压u1(un)的电压差vt2小于图8所示的电压差vt1。因此,可使所述电压差vt2小于一灰阶的电压差。

[0098]

因此,根据图3所示的源极驱动器13,可在驱动高精细及大画面的显示屏20时,提供抑制了在显示屏20的画面中央区域与画面左端及右端区域之间产生的色差的、高品质的显示图像。

[0099]

此外,所述实施例中,如图6及图7所示,由多个开关元件qp及qn来构成灰阶间短路电路133a及灰阶间短路电路133b,但也可利用金属氧化物半导体(metal oxide semiconductor,mos)型的晶体管来实现这些开关元件qp及qn。

[0100]

即,将图6及图7所示的正极短路开关部swp及正极短路开关部swq所含的开关元件qp全部设为p通道型的mos晶体管,将负极短路开关部swn及负极短路开关部swj所含的开关元件qn全部设为n通道型的mos晶体管。

[0101]

此处,图6所示的电平位移器lsa将加载信号lda供给于作为负极短路开关部swn所含的开关元件qn的各n通道型mos晶体管的栅极。进而,电平位移器lsa将使所述加载信号lda的逻辑电平反转而得的加载信号ldaq,供给于作为正极短路开关部swp所含的开关元件qp的各p通道型mos晶体管的栅极。另一方面,图7所示的电平位移器lsb将加载信号ldb供给于作为负极短路开关部swj所含的开关元件qn的各n通道型mos晶体管的栅极。进而,电平位移器lsb将使所述加载信号ldb的逻辑电平反转而得的加载信号ldbq,供给于作为正极短路开关部swq所含的开关元件qp的各p通道型mos晶体管的栅极。

[0102]

进而,关于作为图6及图7所示的开关元件qp的p通道型mos晶体管,其漏极(drain)及源极(source)分别连接于相互邻接的一对配线中的一者及另一者。同样地,关于作为开关元件qn的n通道型mos晶体管,其漏极及源极也分别连接于相互邻接的一对配线中的一者及另一者。

[0103]

而且,图6及图7所示的一例中,灰阶间短路电路133a及灰阶间短路电路133b分别针对每5灰阶,使分别传输所述5灰阶的灰阶电压的5个配线(yl、xl)在各水平扫描期间的开头部短路。但是,短路的配线数不限定于5个。即,只要为下述结构即可:针对与下述数量、例如相互邻接的4个~8个的各灰阶分别对应的每4~8条配线,使此4~8条配线短路,所述数量为通过合成电荷(此合成电荷是通过短路经由各配线而合成)的补充而增加的电压、与短路结束后的电压的差变得微小的数量。

[0104]

重要的是,作为源极驱动器13,只要包含以下的总线配线、灰阶电压生成电路、多个解码器、输出放大器、以及第一灰阶间短路电路及第二灰阶间短路电路即可。

[0105]

总线配线(bs)包含沿规定方向(dl)伸长的多个配线(yl[1]~yl[m]、xl[1]~xl[m])。灰阶电压生成电路(132)生成以m(m为2以上的整数)灰阶来表示亮度电平的m个灰阶电压(y[1]~y[m]、x[1]~x[m])。此外,灰阶电压生成电路(132)将所述m个灰阶电压分别施加于属于所述总线配线(bs)的m个配线(xl或yl)各自的一端与另一端之间的中间部(e1)。多个解码器(e1~en)沿着m个配线(xl或yl)而并排配置,分别经由这些m个配线而接收m个灰阶电压(y或x),根据像素数据片(p)从m个灰阶电压中选择一个并输出。多个输出放大器(a1~an)将从所述多个解码器输出的电压(k1~kn)分别个别地放大,生成为多个像素驱动电压(g1~gn)。第一灰阶间短路电路(133a)根据进行多个像素数据片的导入加载图像信号(ld),使所述m个配线各自的一端彼此短路。第二灰阶间短路电路(133b)根据所述加载信号(ld),使所述m个配线各自的另一端彼此短路。

[0106]

而且,图3所示的一例中,将灰阶电压生成电路132所生成的灰阶电压y[m:1]及x[m:1],施加于沿着并排配置成一列的解码器e1~解码器en而配置的、一系统的总线配线bs的中间部。因此,从灰阶电压生成电路132到解码器e1(en)的配线长、与到解码器er(er+1)的配线长依然存在差。其结果为,在总线配线bs的配线电阻相对较高的情况下,可能灰阶信号k1(kn)所产生的延迟时间、与灰阶信号kr(kr+1)所产生的延迟时间之间产生大的时间差,无法可靠地抑制上文所述的色差。

[0107]

因此,也可将所述一系统的总线配线bs在方向dl的中间部分割为两个,对经分割的总线配线各自的中间部,施加由灰阶电压生成电路132所生成的灰阶电压y[m:1]及x[m:1],由此实现由配线电阻所致的延迟时间的减半。

[0108]

图10为鉴于此方面而成的、表示源极驱动器13的另一结构的、半导体芯片内的各区块的配置形态的图。此外,图10中,省略图3所示的数据锁存部131及电平位移电路l1~电平位移电路ln、以及加载信号ld的配线。而且,关于图10所示的解码器e1~解码器en、输出放大器a1~输出放大器an、灰阶电压生成电路132、灰阶间短路电路133a及灰阶间短路电路133b,与图3所示相同。

[0109]

图10所示的源极驱动器13中,图3及图5所示的总线配线bs被分割为:第一总线配线bs1,将灰阶电压y[m:1]及x[m:1]分别供给于解码器e1~解码器er;以及第二总线配线bs2,将灰阶电压y[m:1]及x[m:1]分别供给于解码器er+1~解码器en。此外,总线配线bs1及

总线配线bs2并未相互连接。

[0110]

在总线配线bs1的一端连接有灰阶间短路电路133a,在其另一端,连接有具有与图7所示的灰阶间短路电路133b同样的结构的灰阶间短路电路141a。在总线配线bs2的一端,连接有具有与图6所示的灰阶间短路电路133a同样的结构的灰阶间短路电路141b,在其另一端连接有灰阶间短路电路133b。

[0111]

图10所示的结构中,灰阶电压生成电路132将自身生成的灰阶电压y[m:1]及灰阶电压x[m:1],施加于与总线配线bs1及总线配线bs2无关而另设置的主总线配线mbs。此外,主总线配线mbs与图5所示的总线配线bs同样地,包含用于分别个别地传输灰阶电压y[1]~灰阶电压y[m]及灰阶电压x[1]~灰阶电压x[m]的2m个配线。此处,主总线配线mbs的2m个配线各自的一端如图10所示,在属于第一总线配线bs1的各配线的一端与另一端之间的中间部,连接于属于总线配线bs1的各配线。而且,主总线配线mbs的2m个配线各自的另一端如图10所示,在属于第二总线配线bs2的各配线的一端与另一端之间的中间部,连接于属于总线配线bs2的各配线。

[0112]

根据图10所示的结构,可使各灰阶信号k1~kn的延迟时间的差、及各像素驱动信号g1~gn的延迟时间的差较采用图3所示的结构的情况更小。因此,可更可靠地抑制在显示屏20的画面中央区域、与画面左端及右端区域之间产生的色差。

[0113]

此外,作为图10所示的源极驱动器13,只要包含以下的第一总线配线及第二总线配线、灰阶电压生成电路、第一解码器~第n(n为2以上的整数)解码器、输出放大器、第一灰阶间短路电路~第四灰阶间短路电路即可。

[0114]

第一总线配线(bs1)及第二总线配线(bs2)分别包含多个配线(yl[1]~yl[m]、xl[1]~xl[m])。灰阶电压生成电路(132)生成以m(m为2以上的整数)灰阶来表示亮度电平的m个灰阶电压(y[1]~y[m]、x[1]~x[m])。另外,灰阶电压生成电路(132)将这些m个灰阶电压,分别施加于属于第一总线配线(bs1)的m个配线各自的一端与另一端之间的中间部、及属于第二总线配线(bs2)的m个配线各自的一端与另一端之间的中间部。第一解码器~第n解码器中的第一解码器~第r(r为2以上且小于n的整数)解码器(e1~er)沿着第一总线配线(bs1)而并排配置,分别经由属于所述第一总线配线的m个配线而接收m个灰阶电压,根据像素数据片(p)从m个灰阶电压中选择一个并输出。第一解码器~第n解码器中的第r+1解码器~第n解码器(er+1~en)沿着第二总线配线(bs2)而并排配置,分别经由属于所述第二总线配线的m个配线而接收m个灰阶电压,根据像素数据片(p)从m个灰阶电压中选择一个并输出。输出放大器(a1~an)将从第一解码器~第n解码器输出的电压(k1~kn)分别个别地放大,生成为n个像素驱动电压(g1~gn)。

[0115]

第一灰阶间短路电路(133a)根据导入多个像素数据片的加载信号(ld),使属于第一总线配线(bs1)的m个配线各自的一端彼此短路。第二灰阶间短路电路(141a)根据加载信号(ld),使属于第一总线配线(bs1)的m个配线各自的另一端彼此短路。第三灰阶间短路电路(141b)根据加载信号(ld),使属于第二总线配线(bs2)的m个配线各自的一端彼此短路。第四灰阶间短路电路(133b)根据加载信号(ld),使属于第二总线配线(bs2)的m个配线各自的另一端彼此短路。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1