LED显示面板的驱动装置及其操作方法与流程

led显示面板的驱动装置及其操作方法

技术领域

1.本发明涉及一种发光二极管(light

‑

emitting diode,led)显示设备,且特别涉及一种led显示面板的驱动装置及其操作方法。

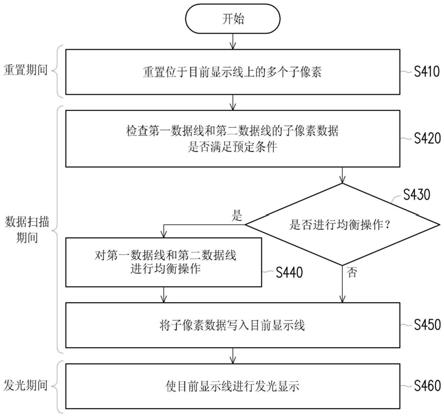

背景技术:

2.有机发光显示(organic light

‑

emitting display,oled)面板的子像素电路的晶体管具有二极管特性,使得在数据扫描期间所述晶体管的栅极电压可能会发生电压过充的现象。当子像素电路的晶体管的栅极电压发生电压过充时,所述子像素电路的存储电容的电压无法追随输出缓冲器的输出电压至目标电平,进而造成oled面板显示异常。

3.须注意的是,“背景技术”段落的内容是用来帮助了解本发明。在“背景技术”段落所公开的部分内容(或全部内容)可能不是所属技术领域的技术人员所知道的已知技术。在“背景技术”段落所公开的内容,不代表该内容在本发明申请前已被所属技术领域的技术人员所知悉。

技术实现要素:

4.本发明提供一种驱动装置及其操作方法,以避免均衡操作所导致的过充现象。

5.在根据本发明的实施例中,上述的驱动装置适于驱动发光二极管显示面板。驱动装置包括源极驱动电路、输出切换电路以及均衡控制电路。输出切换电路的第一输入端与第二输入端分别耦接至源极驱动电路的第一输出端与第二输出端。输出切换电路的第一输出端与第二输出端适于分别耦接至发光二极管显示面板的第一数据线与第二数据线。输出切换电路能够对第一数据线和第二数据线进行均衡操作。均衡控制电路被配置为检查第一数据线的子像素数据和第二数据线的子像素数据是否满足预定条件。在重置期间之后,均衡控制电路依据检查的结果而决定是否在数据扫描期间中控制输出切换电路去对第一数据线与第二数据线进行均衡操作。在重置期间中,位于发光二极管显示面板的目前显示线上的发光二极管显示面板的多个子像素被重置。

6.在根据本发明的实施例中,上述的操作方法包括:由驱动装置的输出切换电路对发光二极管显示面板的第一数据线和第二数据线进行均衡操作;由驱动装置的均衡控制电路检查第一数据线的子像素数据和第二数据线的子像素数据是否满足预定条件;在重置期间重置位于发光二极管显示面板的目前显示线上的发光二极管显示面板的多个子像素;以及在重置期间后,由均衡控制电路依据检查的结果而决定是否在数据扫描期间中控制输出切换电路去对第一数据线与第二数据线进行均衡操作。

7.基于上述,本发明诸实施例所述驱动装置及其操作方法可以检查第一数据线和第二数据线的子像素数据是否满足预定条件,进而依据检查的结果而决定是否对第一数据线与第二数据线进行均衡操作。举例来说,当满足预定条件时,输出切换电路可以进行均衡操作,以减少数据线的充放电操作的电压摆幅(voltage swing)。当没有满足预定条件时,输出切换电路不进行均衡操作,以避免过充现象的发生。因此,所述驱动装置可以避免均衡操

作所导致的过充现象。

附图说明

8.图1是有机发光显示(organic light

‑

emitting display,oled)面板的一种子像素电路的示意图。

9.图2是说明图1所示子像素电路的信号波形示意图。

10.图3是依照本发明的一实施例的一种驱动装置的电路方块(circuit block)示意图。

11.图4是依照本发明的一实施例的一种驱动装置的操作方法的流程示意图。

12.图5是依照本发明的另一实施例的一种驱动装置的操作方法的流程示意图。

13.图6是依照本发明的一实施例说明图3所示均衡控制电路、源极驱动电路与输出切换电路的电路方块示意图。

14.图7是依照本发明的一实施例说明图6所示信号的波形示意图。

15.图8是依照本发明的另一实施例说明图3所示均衡控制电路、源极驱动电路与输出切换电路的电路方块示意图。

16.图9是依照本发明的一实施例说明图8所示信号的波形示意图。

17.图10是依照本发明的又一实施例说明图3所示均衡控制电路、源极驱动电路与输出切换电路的电路方块示意图。

18.图11是依照本发明的一实施例说明图10所示信号的波形示意图。

19.图12是依照本发明的更一实施例说明图3所示均衡控制电路、源极驱动电路与输出切换电路的电路方块示意图。

20.附图标记说明

21.10:oled面板

22.11:栅极驱动器

23.12、13:切换电路

24.300:驱动装置

25.310:均衡控制电路

26.311、315、319:数据与均衡控制电路

27.312、316:移位寄存器

28.313、317:数据锁存器

29.314、318:逻辑电路

30.320:源极驱动电路

31.321、322:数字模拟转换器

32.323、324:输出缓冲器

33.330:输出切换电路

34.340:数字控制与时序产生电路

35.350、380:面板控制信号产生电路

36.360:面板电源产生电路

37.370:灰阶产生电路

38.c

st

:存储电容

39.clk:时钟信号

40.data:数据电压

41.data1、data2:曲线

42.data_o、data_e、data_o/e:子像素数据

43.eck:发光时钟信号

44.ee:发光组件

45.elvdd:阳极电压

46.elvss:阴极电压

47.emi、emi[n]、emi[n

‑

1]、emi[y

‑

1]、emi[y]、emi

odd

[n]、emi

even

[n]、emi

odd

[y]、emi

even

[y]:发光信号

[0048]

eq_prd、eq1_prd、eq2_prd:均衡时钟

[0049]

etv:发光起始脉冲

[0050]

g

n

、g

n

‑1、:驱动信道

[0051]

init、init[n]、init[n

‑

1]、init[y

‑

1]、init[y]、init

odd

[n]、init

even

[n]、init

odd

[y]、init

even

[y]:重置信号

[0052]

line[y

‑

3]、line[y

‑

2]、line[y

‑

1]、line[y]、line[y+1]、line[y+2]:水平期间

[0053]

load:锁存信号

[0054]

m1、m2、m3、m4、m5、m6、m7:晶体管

[0055]

mux1、mux2、en_mux1、en_mux2:切换信号

[0056]

os:过充现象

[0057]

pemi、pemi[y]、pemi[y+1]、pemi_e[y+1]、pemi_o[y+1]:发光期间

[0058]

peq[y

‑

1]:第一子期间

[0059]

pinit、pinit[y

‑

2]、pinit[y

‑

1]、pini_e[y

‑

1]、pini_o[y

‑

1]:初始化期间

[0060]

pscan、pline[y]、pline[y

‑

1]:数据扫描期间

[0061]

pscan[y]、pscan[y

‑

1]、pscan_o[y]、pscan_e[y]:第二子期间

[0062]

s[x]、s[x+1]、s

even

[1]、s

even

[x]、s

even

[x+1]、s

odd

[1]、s

odd

[x]、s

odd

[x+1]:数据线

[0063]

s410~s460、s510~s570:步骤

[0064]

scan、scan[n]、scan[n

‑

1]、scan[y

‑

1]、scan[y]、scan[y+1]、scan

even

[n]、scan

odd

[n]、scan

even

[y

‑

1]、scan

even

[y]、scan

even

[y+1]、scan

odd

[y

‑

1]、scan

odd

[y]、scan

odd

[y+1]:扫描信号

[0065]

sck:扫描时钟信号

[0066]

seq、seq1、seq_e、seq_e1、seq_o、seq_o1:均衡控制信号

[0067]

seq1、soe1、seq

even1

、seq

odd1

、soe

even1

、soe

odd1

:开关信号

[0068]

s

even

[x][y

‑

1]、s

even

[x+1][y

‑

1]、s

odd

[x][y

‑

1]、s

odd

[x+1][y

‑

1]:先前子像素数据

[0069]

s

even

[x][y]、s

even

[x+1][y]、s

odd

[x][y]、s

odd

[x+1][y]:目前子像素数据

[0070]

s

even

[x][y+1]、s

even

[x+1][y+1]、s

odd

[x][y+1]、s

odd

[x+1][y+1]:下一个子像素数据

[0071]

soe_prd、soe1_prd、soe2_prd:输出致能时钟

[0072]

stv:扫描起始脉冲

条显示线、第y+1条显示线与第y+2条显示线)的驱动操作可以参照第y条显示线的相关说明来类推,故不予赘述。

[0083]

请参照图1与图2。当操作在第y

‑

1条显示线的初始化期间(又称重置期间)pinit时,重置信号init被拉低。此时,晶体管m1、m2、m3、m4与m6为截止(turn off),而晶体管m5与m7为导通(turn on)。因此,参考电压vref可以重置发光组件ee与存储电容c

st

,以便为了下一次存储电容c

st

的充电做准备。当操作在第y条显示线的数据扫描期间pscan时,扫描信号scan被拉低。此时,晶体管m2、m5、m6与m7为截止,而晶体管m1、m3与m4为导通。因此,显示驱动集成电路的输出缓冲器(未绘示)开始通过数据线与接成二极管形式的晶体管m3,对存储电容c

st

进行充电至目标电平(显示数据所对应的数据电压data)。当操作在第y+1条显示线的发光期间pemi时,发光信号emi被拉低。此时,晶体管m1、m4、m5与m7关闭为截止,而晶体管m2、m3与m6为导通,使得发光组件ee进行发光显示。存储电容c

st

的数据电压(亦即晶体管m3的栅极电压vg)可以决定晶体管m3的源栅极电压v

sg

。因此,栅极电压vg可以控制通过晶体管m3的电流,进而控制发光组件ee的亮度。

[0084]

在数据扫描期间pscan,显示驱动集成电路的输出缓冲器(未绘示)会将显示数据所对应的数据电压data写到存储电容c

st

。然而由于接成二极管形式的晶体管m3的二极管特性,晶体管m3的栅极电压vg可能会在数据扫描期间pscan发生电压过充的现象。图2所示data1表示未发生过充现象os的数据电压data的曲线,而图2所示data2表示发生过充现象os的数据电压data的曲线。若对oled面板的数据线毫无条件地进行电荷共享操作,则过充现象os极有可能会频繁发生。发生过充现象os的数据电压data会被写入存储电容c

st

。图2所示vg1表示未发生过充现象os的栅极电压vg的曲线,图2所示vg2表示发生过充现象os的栅极电压vg的期望曲线,而图2所示vg3表示发生过充现象os的栅极电压vg的实际曲线。在发生过充现象os后,晶体管m3的栅极电压vg被期望追随数据电压data的曲线data2至目标电平(如期望曲线vg2所示)。在数据扫描期间pscan,晶体管m3具有二极管特性,使得栅极电压vg无法追随数据电压data的曲线data2至目标电平(如实际曲线vg3所示)。当晶体管m3的栅极电压vg发生电压过充时,存储电容c

st

的电压无法追随输出缓冲器(未绘示)的输出电压(数据电压data的曲线data2)至目标电平,进而造成oled面板显示异常。

[0085]

下述诸实施例将说明发光二极管(light

‑

emitting diode,led)显示面板的均衡(equalization)操作。依照设计需求,所述led显示面板可以是有机发光显示(organic light

‑

emitting display,oled)面板或是其他显示面板。依据前一条与当条line在做完数据线eq后与数据线终值的关系,驱动装置可以判断是否要对相邻数据线进行均衡操作。所述均衡操作是指,在显示面板的两条数据线之间提供短路路径,以使这两条数据线的电压暂时地趋于一致。一般而言,所述均衡操作的时间极短。在所述均衡操作结束后,所述短路路径会被截断,以避免影响正常操作。在符合预定条件时,驱动装置可以对相邻的数据线进行均衡操作;反之在不符合预定条件时,驱动装置可以不进行均衡操作。藉由选择性地进行均衡操作,驱动装置可以不但可以减少数据线的充放电操作的电压摆幅(voltage swing),也可以避免均衡操作所导致的过充现象。

[0086]

图3是依照本发明的一实施例的一种驱动装置300的电路方块(circuit block)示意图。图3所示驱动装置300适于驱动led显示面板,例如oled面板10或是其他显示面板。驱动装置300包括均衡控制电路310、源极驱动电路320以及输出切换电路330。基于时序控制

器(未绘示)的控制,均衡控制电路310可以提供所述第一数据线的子像素数据和所述第二数据线的子像素数据给源极驱动电路320。源极驱动电路320可以将这些子像素数据转换为数据电压。

[0087]

输出切换电路330的第一输入端与第二输入端分别耦接至源极驱动电路320的第一输出端与第二输出端。输出切换电路330的第一输出端与第二输出端适于耦接至oled面板10的第一数据线与第二数据线。源极驱动电路320可以将数据电压通过输出切换电路330传输给oled面板10的第一数据线和第二数据线。此外,输出切换电路330能够对oled面板10的第一数据线和第二数据线选择性地进行均衡操作。oled面板10包括多个显示子像素,这些显示子像素的每一个包括用于存储子像素数据的电荷(数据电压)的存储电容(例如图1所示存储电容c

st

)。

[0088]

图4是依照本发明的一实施例的一种驱动装置300的操作方法的流程示意图。在图4所示实施例中,驱动装置300对于oled面板10的驱动操作至少分成重置期间、数据扫描期间与发光期间。请参照图3与图4。在重置期间中,位于oled面板10的目前显示线上的oled面板10的多个子像素被重置(步骤s410)。所述子像素包括发光组件(例如有机发光二极管或是其他发光二极管)。本实施例并不限制所述子像素的实施方式。依照设计需求,在一些实施例中,oled面板10的所述子像素可以参照图1与图2所述子像素电路的相关说明。在其他实施例中,oled面板10的所述子像素可以是其他子像素电路。在重置期间之后进入了数据扫描期间。

[0089]

均衡控制电路310可以在数据扫描期间检查第一数据线的子像素数据和第二数据线的子像素数据是否满足预定条件(步骤s420)。所述预定条件可以防止在oled面板10的所述子像素中的存储电容(例如图1所示存储电容c

st

)过度充电。须注意的是,依照设计需求,在另一些实施例中,均衡控制电路310可以在重置期间之后以及在数据扫描期间之前进行步骤s420。在又一些实施例中,均衡控制电路310可以在重置期间中行步骤s420。

[0090]

在所述重置期间之后,均衡控制电路310可以依据步骤s420的检查的结果而决定是否在数据扫描期间中控制输出切换电路去对oled面板10的第一数据线与第二数据线进行均衡操作(步骤s430)。当第一数据线和第二数据线的子像素数据不满足所述预定条件时(步骤s430的判断结果为“否”),驱动装置300进行步骤s450。当第一数据线和第二数据线的子像素数据满足所述预定条件时(步骤s430的判断结果为“是”),驱动装置300进行步骤s440。

[0091]

在步骤s440中,基于均衡控制电路310的控制,输出切换电路330对oled面板10的第一数据线和第二数据线进行均衡操作。举例来说,输出切换电路330可以在步骤s440中将第一数据线电性连接至第二数据线,以及在步骤s440结束后使第一数据线不电性连接至第二数据线。在步骤s440结束后,驱动装置300进行步骤s450。

[0092]

在步骤s450中,源极驱动电路320可以将子像素数据(数据电压)通过输出切换电路330传输给oled面板10的第一数据线和第二数据线,以便将子像素数据写入至oled面板10的目前显示线上的子像素。在数据扫描期间之后进入了发光期间。在发光期间中,驱动装置300使oled面板10的目前显示线上的多个子像素进行发光显示(亦即点亮子像素中的发光组件,步骤s460)。

[0093]

基于上述,基于“oled面板10的第一数据线和第二数据线的子像素数据是否满足

预定条件”的检查结果,本实施例所述驱动装置300可以决定是否对第一数据线与第二数据线进行均衡操作。举例来说,当满足预定条件时,输出切换电路330可以进行均衡操作,以减少数据线的充放电操作的电压摆幅(voltage swing)。当没有满足预定条件时,输出切换电路330不进行均衡操作,以避免过充现象的发生。因此,所述驱动装置300可以避免均衡操作所导致的过充现象。尤其是,对于具有接成二极管形式的晶体管的子像素(例如图1所示子像素电路)而言,这样的子像素更不容许过充现象的发生。

[0094]

所述预定条件可以依照设计需求来定义。举例来说,在一些实施例中,待检查的第一数据线的子像素数据报括先前子像素数据与目前子像素数据,待检查的第二数据线的子像素数据报括先前子像素数据与目前子像素数据,以及所述预定条件可以包括这四者之间的关系。均衡控制电路310可以在步骤s420检查第一数据线的先前子像素数据、第一数据线的目前子像素数据、第二数据线的先前子像素数据与第二数据线的目前子像素数据,以便决定是否控制输出切换电路330去对第一数据线与第二数据线进行均衡操作。输出切换电路330可以在oled面板10的目前显示线所对应的数据扫描期间内,对第一数据线和第二数据线进行均衡操作。

[0095]

在一些实施例中,均衡控制电路310可以在步骤s420检查第一数据线的子像素数据的变化方向以及第二数据线的子像素数据的变化方向(所述预定条件)。举例来说,在一些实施例中,所述预定条件包括条件一与条件二。所述条件一为,“从第一数据线的先前子像素数据所对应的先前电压电平到第一数据线和第二数据线的均衡电平的方向”是否一致于“从第一数据线的先前子像素数据所对应的先前电压电平到第一数据线的目前子像素数据所对应的目前电压电平的方向”。所述条件二为,“从第二数据线的先前子像素数据所对应的先前电压电平到第一数据线和第二数据线的均衡电平的方向”是否一致于“从第二数据线的先前子像素数据所对应的先前电压电平到第二数据线的目前子像素数据所对应的目前电压电平的方向”。

[0096]

当第一数据线的先前子像素数据大于第二数据线的先前子像素数据时,以及当第一数据线的目前子像素数据小于第一数据线的先前子像素数据与第二数据线的先前子像素数据的平均值时,以及当第二数据线的目前子像素数据大于所述平均值时,均衡控制电路310可以控制输出切换电路330去进行均衡操作。当第一数据线的先前子像素数据小于第二数据线的先前子像素数据时,以及当第一数据线的目前子像素数据大于所述平均值时,以及当第二数据线的目前子像素数据小于所述平均值时,均衡控制电路310可以控制输出切换电路330去进行均衡操作。

[0097]

图5是依照本发明的另一实施例的一种驱动装置300的操作方法的流程示意图。在图5所示实施例中,均衡控制电路310可以比较第一数据线的先前子像素数据s

odd

[x][y

‑

1]与第二数据线的先前子像素数据s

even

[x][y

‑

1](步骤s510)。当先前子像素数据s

odd

[x][y

‑

1]大于先前子像素数据s

even

[x][y

‑

1]时(步骤s510的判断结果为“是”),驱动装置300进行步骤s520。在步骤s520中,均衡控制电路310可以比较s

odd

[x][y]与(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2,以及比较s

even

[x][y]与(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2。其中,s

odd

[x][y]为第一数据线的目前子像素数据,s

even

[x][y]为第二数据线的目前子像素数据,以及(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2为先前子像素数据s

odd

[x][y

‑

1]与先前子像素数据s

even

[x][y

‑

1]的平均值。

[0098]

当第一数据线的目前子像素数据小于平均值时(即s

odd

[x][y]<(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2),以及当第二数据线的目前子像素数据大于平均值时(即s

even

[x][y]>(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2),步骤s520的判断结果为“是”,因而驱动装置300进行步骤s530。在步骤s530中,均衡控制电路310可以控制输出切换电路330去对oled面板10的第一数据线和第二数据线进行均衡操作。均衡操作会使所述第一数据线与所述第二数据线的电压约略均衡在平均值(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2)所对应的电压电平。当步骤s520的判断结果为“否”时,驱动装置300进行步骤s550。在步骤s550中,均衡控制电路310可以控制输出切换电路330对oled面板10的第一数据线和第二数据线不进行均衡操作。

[0099]

当先前子像素数据s

odd

[x][y

‑

1]不大于先前子像素数据s

even

[x][y

‑

1]时(步骤s510的判断结果为“否”),驱动装置300进行步骤s540。在步骤s540中,均衡控制电路310可以判断第一数据线的先前子像素数据s

odd

[x][y

‑

1]是否小于第二数据线的先前子像素数据s

even

[x][y

‑

1]。当先前子像素数据s

odd

[x][y

‑

1]不小于先前子像素数据s

even

[x][y

‑

1]时(步骤s540的判断结果为“否”),驱动装置300进行步骤s550。在步骤s550中,均衡控制电路310可以控制输出切换电路330对oled面板10的第一数据线和第二数据线不进行均衡操作。

[0100]

当先前子像素数据s

odd

[x][y

‑

1]小于先前子像素数据s

even

[x][y

‑

1]时(步骤s540的判断结果为“是”),驱动装置300进行步骤s560。在步骤s560中,均衡控制电路310可以比较s

odd

[x][y]与(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2,以及比较s

even

[x][y]与(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2。当第一数据线的目前子像素数据大于平均值时(即s

odd

[x][y]>(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2),以及当第二数据线的目前子像素数据小于平均值时(即s

even

[x][y]<(s

odd

[x][y

‑

1]+s

even

[x][y

‑

1])/2),步骤s560的判断结果为“是”,因而驱动装置300进行步骤s570。在步骤s570中,均衡控制电路310可以控制输出切换电路330去对oled面板10的第一数据线和第二数据线进行均衡操作。当步骤s560的判断结果为“否”时,驱动装置300进行步骤s550。在步骤s550中,均衡控制电路310可以控制输出切换电路330对oled面板10的第一数据线和第二数据线不进行均衡操作。

[0101]

进行均衡操作的判断条件包括,除了判断两相邻数据线的电压是否有所差异外,同时也会考虑在做完均衡操作之后数据线是否会有过充的问题。判断两相邻数据线电压的差异,主要是为了确保均衡操作具有省电的效果。判断两相邻数据线在做均衡操作时的电压变动方向与数据线的目标电压的方向是否一致,则可避免数据线过充的问题。因此,驱动装置300可以确保在做完均衡操作之后也不会影响到oled面板10的视效。

[0102]

图6是依照本发明的一实施例说明图3所示均衡控制电路310、源极驱动电路320与输出切换电路330的电路方块示意图。在图6所示实施例中,驱动装置300还包括数字控制与时序产生电路340、面板控制信号产生电路350、面板电源产生电路360与灰阶产生电路370。数字控制与时序产生电路340也可被称为时序控制器。数字控制与时序产生电路340可以控制均衡控制电路310、面板控制信号产生电路350、面板电源产生电路360与灰阶产生电路370。此外,数字控制与时序产生电路340还可以提供时序信息(例如时钟信号)给均衡控制电路310与面板控制信号产生电路350,以及提供子像素数据给均衡控制电路310。基于数字控制与时序产生电路340的控制,灰阶产生电路370可以提供灰阶电压给源极驱动电路320。

[0103]

基于数字控制与时序产生电路340所提供的时序信息,面板控制信号产生电路350可以产生扫描起始脉冲stv、扫描时钟信号sck、发光起始脉冲etv与发光时钟信号eck给栅

极驱动器11。栅极驱动器11包括多个驱动信道,例如图6所示驱动信道g

n

与g

n

‑1。栅极驱动器11可以产生重置信号init(例如第n条重置线的重置信号init[n]以及第n

‑

1条重置线的重置信号init[n

‑

1])、扫描信号scan(例如第n条显示线的扫描信号scan[n]以及第n

‑

1条显示线的扫描信号scan[n

‑

1])以及发光信号emi(例如第n条发光线的发光信号emi[n]以及第n

‑

1条发光线的发光信号emi[n

‑

1])给oled面板10的子像素。依照设计需求,在一些实施例中,图6所示oled面板10的子像素可以参照图1与图2所述子像素电路的相关说明来类推,故不再赘述。此外,基于数字控制与时序产生电路340的控制,面板电源产生电路360可以提供阳极电压elvdd、阴极电压elvss与参考电压vref给oled面板10。

[0104]

图7是依照本发明的一实施例说明图6所示信号的波形示意图。请参照图6与图7。图7所示横轴表示时间。图7所示line[y

‑

3]、line[y

‑

2]、line[y

‑

1]、line[y]与line[y+1]分别表示第y

‑

3条显示线、第y

‑

2条显示线、第y

‑

1条显示线、第y条显示线与第y+1条显示线的水平期间。图7所示scan[y

‑

1]、scan[y]与scan[y+1]分别表示第y

‑

1、y与y+1条显示线的扫描信号scan。图7所示init[y

‑

1]表示第y

‑

1条显示线的重置信号init。图7所示emi[y

‑

1]表示第y

‑

1条显示线的发光信号emi。图7所示pinit[y

‑

2]表示第y

‑

1条显示线的重置期间pinit。图7所示pline[y

‑

1]表示第y

‑

1条显示线的数据扫描期间pscan。图7所示pemi[y]表示第y

‑

1条显示线的发光期间pemi。图7所示s

odd

[x][y

‑

1]、s

odd

[x][y]与s

odd

[x][y+1]分别表示第一数据线s

odd

[1]的先前子像素数据、目前子像素数据与下一个子像素数据。图7所示s

even

[x][y

‑

1]、s

even

[x][y]与s

even

[x][y+1]分别表示第二数据线s

even

[1]的先前子像素数据、目前子像素数据与下一个子像素数据。

[0105]

图6所示均衡控制电路310包括数据与均衡控制电路311、移位寄存器312、数据锁存器313以及逻辑电路314。数据与均衡控制电路311耦接至数字控制与时序产生电路340,以接收子像素数据串流。基于所述子像素数据串流,数据与均衡控制电路311可以检查所述第一数据线s

odd

[1]的子像素数据以及所述第二数据线s

even

[1]的子像素数据是否满足所述预定条件,以及依据检查的结果而设定均衡控制信号seq。举例来说,数据与均衡控制电路311可以检查所述第一数据线s

odd

[1]的先前子像素数据与目前子像素数据,以及数据与均衡控制电路311可以检查所述第二数据线s

even

[1]的先前子像素数据与目前子像素数据,以及依据检查的结果而设定均衡控制信号seq。

[0106]

移位寄存器312耦接至数据与均衡控制电路311,以接收均衡控制信号seq、时钟信号clk、子像素数据data_o与子像素数据data_e。数据锁存器313耦接至移位寄存器312,以接收均衡控制信号seq、子像素数据data_o与子像素数据data_e。数据锁存器313还耦接至数据与均衡控制电路311,以接收锁存信号load、输出致能时钟soe_prd以及均衡时钟eq_prd。逻辑电路314耦接至数据锁存器313,以接收均衡控制信号seq1。逻辑电路314还通过数据锁存器313耦接至数据与均衡控制电路311,以接收输出致能时钟soe_prd以及均衡时钟eq_prd。

[0107]

源极驱动电路320包括数字模拟转换器(digital to analog converter,dac)321、数字模拟转换器322、输出缓冲器323以及输出缓冲器324。依照设计需求,输出缓冲器323以及输出缓冲器324可以是运算(op)放大器或是其他增益电路。数字模拟转换器321的输入端耦接至数据锁存器313的第一输出端。数字模拟转换器322的输入端耦接至数据锁存器313的一第二输出端。输出缓冲器323的输入端耦接至数字模拟转换器321的输出端。输出

缓冲器323的输出端耦接至输出切换电路330。输出缓冲器324的输入端耦接至数字模拟转换器322的输出端。输出缓冲器324的输出端耦接至输出切换电路330。

[0108]

逻辑电路314依据均衡控制信号seq1、输出致能时钟soe_prd以及均衡时钟eq_prd产生开关信号seq1与soe1,以控制输出切换电路330。图6所示输出切换电路330包括输出开关sw

odd1

、输出开关sw

even1

与均衡开关sw

eq1

。输出开关sw

odd1

的第一端耦接至源极驱动电路320的第一输出端。输出开关sw

odd1

的第二端适于耦接至oled面板10的第一数据线s

odd

[1]。输出开关sw

even1

的第一端耦接至源极驱动电路320的第二输出端。输出开关sw

even1

的第二端适于耦接至oled面板10的第二数据线s

even

[1]。均衡开关sw

eq1

的第一端与第二端分别耦接至输出开关sw

odd1

的第二端与输出开关sw

even1

的第二端。

[0109]

当均衡控制电路310决定在数据扫描期间pline[y

‑

1]中控制输出切换电路330去进行均衡操作时,均衡控制电路310决定在数据扫描期间pline[y

‑

1]的第一子期间peq[y

‑

1]控制输出开关sw

odd1

与输出开关sw

even1

为截止以及均衡开关sw

eq1

为导通,以及均衡控制电路310决定在第一子期间peq[y

‑

1]后的数据扫描期间pline[y

‑

1]的第二子期间pscan[y

‑

1]控制输出开关sw

odd1

与输出开关sw

even1

为导通以及均衡开关sw

eq1

为截止。举例来说,当均衡控制信号seq1为高逻辑电平(表示决定进行均衡操作)时,逻辑电路314在数据扫描期间pline[y

‑

1]的第一子期间peq[y

‑

1]截止输出开关sw

odd1

与输出开关sw

even1

以及导通均衡开关sw

eq1

,以及在数据扫描期间pline[y

‑

1]的第二子期间pscan[y

‑

1]导通输出开关sw

odd1

与输出开关sw

even1

以及截止均衡开关sw

eq1

。

[0110]

当均衡控制电路310决定在数据扫描期间pline[y

‑

1]中不控制输出切换电路330去进行均衡操作时,均衡控制电路310在数据扫描期间pline[y

‑

1]中持续截止均衡开关sw

eq1

。举例来说,当均衡控制信号seq1为低逻辑电平(表示决定不进行该均衡操作)时,逻辑电路314可以在数据扫描期间pline[y

‑

1]中持续导通输出开关sw

odd1

与输出开关sw

even1

以及持续截止均衡开关sw

eq1

。

[0111]

图8是依照本发明的另一实施例说明图3所示均衡控制电路310、源极驱动电路320与输出切换电路330的电路方块示意图。在图8所示实施例中,驱动装置300还包括数字控制与时序产生电路340、面板控制信号产生电路380、面板电源产生电路360与灰阶产生电路370。图8所示驱动装置300、均衡控制电路310、源极驱动电路320、输出切换电路330、数字控制与时序产生电路340、面板控制信号产生电路380、面板电源产生电路360与灰阶产生电路370可以参照图6所示驱动装置300、均衡控制电路310、源极驱动电路320、输出切换电路330、数字控制与时序产生电路340、面板控制信号产生电路350、面板电源产生电路360与灰阶产生电路370的相关说明类推,故不再赘述。

[0112]

在图8所示实施例中,基于数字控制与时序产生电路340所提供的时序信息,面板控制信号产生电路380可以产生扫描起始脉冲stv、扫描时钟信号sck、发光起始脉冲etv与发光时钟信号eck给栅极驱动器11,以及产生切换信号mux1与切换信号mux2给切换电路12。图8所示oled面板10与栅极驱动器11可以参照图6所示oled面板10与栅极驱动器11的相关说明类推,故不再赘述。

[0113]

图9是依照本发明的一实施例说明图8所示信号的波形示意图。请参照图8与图9。图9所示横轴表示时间。图9所示line[y

‑

1]、line[y]与line[y+1]分别表示第y

‑

1条显示线、第y条显示线与第y+1条显示线的水平期间。图9所示scan[y

‑

1]、scan[y]与scan[y+1]分别

表示第y

‑

1、y与y+1条显示线的扫描信号scan。图9所示init[y]表示第y条显示线的重置信号init。图9所示emi[y]表示第y条显示线的发光信号emi。图9所示pinit[y

‑

1]表示第y条显示线的重置期间pinit。图9所示pline[y]表示第y条显示线line[y]的数据扫描期间。图9所示pscan[y]表示第y条显示线的第二子期间。图9所示pemi[y+1]表示第y条显示线的发光期间pemi。图9所示s

odd

[x][y

‑

1]、s

odd

[x][y]与s

odd

[x][y+1]分别表示数据线s

odd

[x]的先前子像素数据、目前子像素数据与下一个子像素数据。图9所示s

even

[x][y

‑

1]、s

even

[x][y]与s

even

[x][y+1]分别表示数据线s

even

[x]的先前子像素数据、目前子像素数据与下一个子像素数据。图9所示s

odd

[x+1][y

‑

1]、s

odd

[x+1][y]与s

odd

[x+1][y+1]分别表示数据线s

odd

[x+1]的先前子像素数据、目前子像素数据与下一个子像素数据。图9所示s

even

[x+1][y

‑

1]、s

even

[x+1][y]与s

even

[x+1][y+1]分别表示数据线s

even

[x+1]的先前子像素数据、目前子像素数据与下一个子像素数据。

[0114]

图8所示均衡控制电路310包括数据与均衡控制电路315、移位寄存器316、数据锁存器317以及逻辑电路318。数据与均衡控制电路315耦接至数字控制与时序产生电路340,以接收子像素数据串流。基于所述子像素数据串流,数据与均衡控制电路315可以检查第一数据线s[x]的子像素数据以及第二数据线s[x+1]的子像素数据是否满足所述预定条件,以及依据检查的结果而设定均衡控制信号seq_o与seq_e。图8所示数据与均衡控制电路315、移位寄存器316、数据锁存器317以及逻辑电路318可以参照图6所示数据与均衡控制电路311、移位寄存器312、数据锁存器313以及逻辑电路314的相关说明来类推,故不再赘述。

[0115]

移位寄存器316耦接至数据与均衡控制电路315,以接收均衡控制信号seq_o、均衡控制信号seq_e、时钟信号clk与子像素数据data_o/e。数据锁存器317耦接至移位寄存器316,以接收均衡控制信号seq_o、均衡控制信号seq_e与子像素数据data_o/e。数据锁存器317还耦接至数据与均衡控制电路315,以接收锁存信号load、输出致能时钟soe1_prd、输出致能时钟soe2_prd、均衡时钟eq1_prd以及均衡时钟eq2_prd。

[0116]

源极驱动电路320包括数字模拟转换器(dac)321、数字模拟转换器322、输出缓冲器323以及输出缓冲器324。图8所示数字模拟转换器321、数字模拟转换器322、输出缓冲器323以及输出缓冲器324可以参照图6的相关说明来类推,故不再赘述。

[0117]

逻辑电路318依据均衡控制信号seq_o1、均衡控制信号seq_e1、输出致能时钟soe1_prd、输出致能时钟soe2_prd、均衡时钟eq1_prd以及均衡时钟eq2_prd产生开关信号seq

odd1

与soe

odd1

,以控制输出切换电路330。图8所示输出切换电路330包括输出开关sw

odd1

、输出开关sw

even1

与均衡开关sw

eq1

。图8所示输出开关sw

odd1

、输出开关sw

even1

与均衡开关sw

eq1

可以参照图6的相关说明来类推,故不再赘述。

[0118]

图10是依照本发明的又一实施例说明图3所示均衡控制电路310、源极驱动电路320与输出切换电路330的电路方块示意图。在图10所示实施例中,驱动装置300还包括数字控制与时序产生电路340、面板控制信号产生电路380、面板电源产生电路360与灰阶产生电路370。图10所示驱动装置300、均衡控制电路310、源极驱动电路320、输出切换电路330、数字控制与时序产生电路340、面板控制信号产生电路380、面板电源产生电路360与灰阶产生电路370可以参照图8的相关说明类推,故不再赘述。在图10所示实施例中,基于数字控制与时序产生电路340所提供的时序信息,面板控制信号产生电路380可以产生扫描起始脉冲stv、扫描时钟信号sck、发光起始脉冲etv与发光时钟信号eck给栅极驱动器11,以及产生切

换信号mux1与切换信号mux2给切换电路13。

[0119]

栅极驱动器11包括多个驱动信道。栅极驱动器11可以产生重置信号init(例如第n条奇数重置线的重置信号init

odd

[n]以及第n条偶数重置线的重置信号init

even

[n])、扫描信号scan(例如第n条奇数显示线的扫描信号scan

odd

[n]以及第n条偶数显示线的扫描信号scan

even

[n])以及发光信号emi(例如第n条奇数发光线的发光信号emi

odd

[n]以及第n条偶数发光线的发光信号emi

even

[n])给oled面板10的子像素。依照设计需求,在一些实施例中,图10所示oled面板10的子像素可以参照图1与图2所述子像素电路的相关说明来类推,故不再赘述。图10所示oled面板10与栅极驱动器11可以参照图6所示oled面板10与栅极驱动器11的相关说明类推,故不再赘述。

[0120]

图11是依照本发明的一实施例说明图10所示信号的波形示意图。请参照图10与图11。图11所示横轴表示时间。图11所示line[y

‑

1]、line[y]与line[y+1]分别表示第y

‑

1条显示线、第y条显示线与第y+1条显示线的水平期间。图11所示scan[y

‑

1]、scan[y]与scan[y+1]分别表示第y

‑

1、y与y+1条显示线的扫描信号scan。图11所示init

odd

[y]表示第y条奇数显示线的重置信号init。图11所示init

even

[y]表示第y条偶数显示线的重置信号init。图11所示emi

odd

[y]表示第y条奇数显示线的发光信号emi。图11所示emi

even

[y]表示第y条偶数显示线的发光信号emi。图11所示pini_o[y

‑

1]表示第y条奇数显示线的重置期间pinit。图11所示pini_e[y

‑

1]表示第y条偶数显示线的重置期间pinit。图11所示pscan_o[y]表示第y条奇数显示线的第二子期间。图11所示pscan_e[y]表示第y条偶数显示线的第二子期间。图11所示pemi_o[y+1]表示第y条奇数显示线的发光期间pemi。图11所示pemi_e[y+1]表示第y条偶数显示线的发光期间pemi。图11所示s

odd

[x][y

‑

1]、s

odd

[x][y]与s

odd

[x][y+1]分别表示数据线s

odd

[x]的先前子像素数据、目前子像素数据与下一个子像素数据。图11所示s

odd

[x+1][y

‑

1]、s

odd

[x+1][y]与s

odd

[x+1][y+1]分别表示数据线s

odd

[x+1]的先前子像素数据、目前子像素数据与下一个子像素数据。图11所示s

even

[x][y

‑

1]、s

even

[x][y]与s

even

[x][y+1]分别表示数据线s

even

[x]的先前子像素数据、目前子像素数据与下一个子像素数据。图11所示s

even

[x+1][y

‑

1]、s

even

[x+1][y]与s

even

[x+1][y+1]分别表示数据线s

even

[x+1]的先前子像素数据、目前子像素数据与下一个子像素数据。

[0121]

图10所示均衡控制电路310包括数据与均衡控制电路319、移位寄存器312、数据锁存器317以及逻辑电路318。数据与均衡控制电路319耦接至数字控制与时序产生电路340,以接收子像素数据串流。基于所述子像素数据串流,数据与均衡控制电路319可以检查第一数据线s

odd

[x]的子像素数据以及第二数据线s

odd

[x+1]的子像素数据是否满足所述预定条件,以及检查第一数据线s

even

[x]的子像素数据以及第二数据线s

even

[x+1]的子像素数据是否满足所述预定条件,以及依据检查的结果而设定均衡控制信号seq。图10所示数据与均衡控制电路319、移位寄存器312、数据锁存器317以及逻辑电路318可以参照图6所示数据与均衡控制电路311、移位寄存器312、数据锁存器313以及逻辑电路314的相关说明来类推,故不再赘述。

[0122]

移位寄存器312耦接至数据与均衡控制电路319,以接收均衡控制信号seq、时钟信号clk、子像素数据data_o与子像素数据data_e。数据锁存器317耦接至移位寄存器312,以接收均衡控制信号seq、子像素数据data_o与子像素数据data_e。数据锁存器317还耦接至数据与均衡控制电路319,以接收锁存信号load、输出致能时钟soe1_prd、输出致能时钟

hdl或vhdl)或其他合适的编程语言来实现为硬件。举例来说,上述均衡控制电路310、数据与均衡控制电路311以及(或是)数字控制与时序产生电路340的相关功能可以被实现于一或多个控制器、微控制器、微处理器、特殊应用集成电路(application

‑

specific integrated circuit,asic)、数字信号处理器(digital signal processor,dsp)、场可编程逻辑门阵列(field programmable gate array,fpga)和/或其他处理单元中的各种逻辑区块、模块和电路。

[0129]

以软件形式和/或固件形式而言,上述均衡控制电路310、数据与均衡控制电路311以及(或是)数字控制与时序产生电路340的相关功能可以被实现为编程码(programming codes)。例如,利用一般的编程语言(programming languages,例如c、c++或汇编语言)或其他合适的编程语言来实现上述均衡控制电路310、数据与均衡控制电路311以及(或是)数字控制与时序产生电路340。所述编程码可以被记录/存放在记录介质中。在一些实施例中,所述记录介质例如包括只读存储器(read only memory,rom)、随机存取存储器(random access memory,ram)以及(或是)存储装置。所述存储装置包括硬盘(hard disk drive,hdd)、固态硬盘(solid

‑

state drive,ssd)或是其他存储装置。在另一些实施例中,所述记录介质可以包括“非临时的计算机可读介质(non

‑

transitory computer readable medium)”。举例来说,带(tape)、盘(disk)、卡(card)、半导体内存、可编程设计的逻辑电路等可以被使用来实现所述非临时的计算机可读取介质。控制器、微控制器或微处理器可以从所述记录介质中读取并执行所述编程码,从而实现上述均衡控制电路310、数据与均衡控制电路311以及(或是)数字控制与时序产生电路340的相关功能。

[0130]

综上所述,上述诸实施例所述驱动装置300可以检查第一数据线和第二数据线的子像素数据是否满足预定条件,进而依据检查的结果而决定是否对第一数据线与第二数据线进行均衡操作。举例来说,当满足预定条件时,输出切换电路330可以进行均衡操作,以减少数据线的充放电操作的电压摆幅(voltage swing)。当没有满足预定条件时,输出切换电路330不进行均衡操作,以避免过充现象的发生。因此,所述驱动装置300可以避免均衡操作所导致的过充现象。

[0131]

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1