电子装置以及像素电路的制作方法

1.本公开是有关于一种电子装置以及其像素电路,特别是有关于一种共用驱动晶体管的像素电路。

背景技术:

2.随着高解析度显示面板的应用日益普及,使得显示面板中像素之间的间距越来越小,而电路布局的面积也越来越受限。为了解决电路布局面积受限的问题,有必要针对像素电路进行优化。

技术实现要素:

3.有鉴于此,本公开提出一种电子装置包括基板、第一发光单元、第二发光单元、驱动晶体管、第一发光晶体管以及第二发光晶体管。第一发光单元以及第二发光单元设置于基板上。驱动晶体管电性连接至电压源,第一发光晶体管电性连接于驱动晶体管以及第一发光单元之间。第二发光晶体管电性连接于驱动晶体管以及第二发光单元之间。

附图说明

4.为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

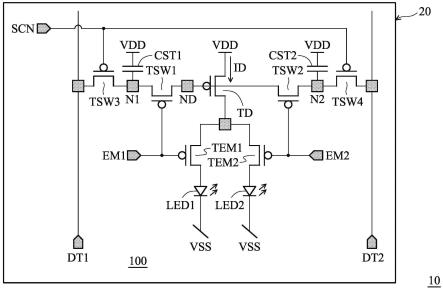

5.图1是显示根据本公开的一实施例所述的像素电路的电路图;

6.图2是显示根据本公开的一实施例所述的像素电路中晶体管结构的示意图;

7.图3是显示根据本公开的一实施例所述的图1的像素电路的波形图;

8.图4是显示根据本公开的另一实施例所述的像素电路的电路图;

9.图5是显示根据本公开的另一实施例所述的像素电路的电路图;

10.图6是显示根据本公开的另一实施例所述的像素电路的电路图;

11.图7是显示根据本公开的另一实施例所述的像素电路的电路图;

12.图8是显示根据本公开的一实施例所述的图7的像素电路的波形图;

13.图9是显示根据本公开的另一实施例所述的图7的像素电路的波形图;以及

14.图10是显示根据本公开的另一实施例所述的像素电路的电路图。

15.符合说明:

16.10:电子装置

17.20:基板

18.100,400,500,600,700,1000:像素电路

19.300,800,900:波形图

20.id:驱动电流

21.vdd:电压源

22.vss:接地位准

23.tsw1:第一开关晶体管

24.tsw2:第二开关晶体管

25.tsw3:第三开关晶体管

26.tsw4:第四开关晶体管

27.cst1:第一储存电容

28.cst2:第二储存电容

29.td:驱动晶体管

30.led1:第一发光单元

31.led2:第二发光单元

32.tem1:第一发光晶体管

33.tem2:第二发光晶体管

34.em1:第一发光信号

35.em2:第二发光信号

36.en1:第一使能信号

37.en2:第二使能信号

38.n1:第一节点

39.n2:第二节点

40.nd:节点

41.a:第一期间

42.b:第二期间

43.c:第三期间

44.d1:第一延迟时间

45.d2:第二延迟时间

46.d3:第三延迟时间

47.d4:第四延迟时间

48.e:第四期间

49.f:第五期间

50.g:第六期间

51.h:第七期间

52.j:第八期间

53.l:第九期间

54.m:第十期间

55.n:第十一期间

56.o:第十二期间

57.p:第十三期间

58.s:源极

59.d:漏极

60.cl:间距

61.smc:半导体层

62.gt:栅极

63.w:宽度

具体实施方式

64.以下说明为本公开的实施例。其目的是要举例说明本公开一般性的原则,不应视为本公开的限制,本公开的范围当以权利要求所界定者为准。

65.能理解的是,虽然在此可使用用语“第一”、“第二”、“第三”等来叙述各种元件、组成成分、区域、层、及/或部分,这些元件、组成成分、区域、层、及/或部分不应被这些用语限定,且这些用语仅是用来区别不同的元件、组成成分、区域、层、及/或部分。因此,在说明书中所称的一第一元件、组成成分、区域、层、及/或部分可在不偏离本公开一些实施例的启示的情况下,于权利要求中被称为一第二元件、组成成分、区域、层、及/或部分。

66.值得注意的是,以下所公开的内容可提供多个用以实践本公开的不同特点的实施例或范例。以下所述的特殊的元件范例与安排仅用以简单扼要地阐述本公开的精神,并非用以限定本公开的范围。此外,以下说明书可能在多个范例中重复使用相同的元件符号或文字。然而,重复使用的目的仅为了提供简化并清楚的说明,并非用以限定多个以下所讨论的实施例以及/或配置之间的关系。此外,以下说明书所述的一个特征连接至、电性连接至以及/或形成于另一特征之上等的描述,实际可包含多个不同的实施例,包括这些特征直接接触,或者包含其它额外的特征形成于这些特征之间等等,使得这些特征并非直接接触。

67.图1是显示根据本公开的一实施例所述的电子装置的示意图。本公开的电子装置可包括显示装置,或是包含显示面板的任何电子装置,例如触控显示装置(touch display)、曲面显示装置(curved display)、可弯折或可挠式显示装置(flexible display)或非矩形显示装置(free shape display),但不以此为限。如图1所示,电子装置10包括像素电路100以及基板20,其中像素电路100是形成于基板20的上。如图1所示,像素电路100包括第一开关晶体管tsw1、第一储存电容cst1、第二开关晶体管tsw2、第三开关晶体管tsw3、第二储存电容cst2、第四开关晶体管tsw4、驱动晶体管td、第一发光单元led1、第二发光单元led2、第一发光晶体管tem1以及第二发光晶体管tem2。根据本公开的一实施例,像素电路100是仅由p型晶体管所实现,但本公开的晶体管类型并不限于此。

68.如图1所示,第一开关晶体管tsw1是电性连接于驱动晶体管td,其中第一开关晶体管tsw1与驱动晶体管td栅极之间可具有一驱动节点nd,第一开关晶体管tsw1与第三开关晶体管tsw3电性连接,且两者之间可具有一第一节点n1,该第一节点n1与第一开关晶体管tsw1与第三开关晶体管tsw3电性连接,且第一开关晶体管tsw1的栅极端是接收第一发光信号em1。第一储存电容cst1是电性连接于电压源vdd以及第一节点n1之间,用以储存第一节点n1的电压。根据本公开的另一实施例,第一储存电容cst1是电性连接于接地位准vss以及第一节点n1之间。根据本公开的其他实施例,第一储存电容cst1可电性连接于任何参考电压以及第一节点n1之间。

69.相似地,第二开关晶体管tsw2是电性连接于驱动晶体管td,其中第二开关晶体管tsw2与第四开关晶体管tsw4电性连接,且两者之间可具有一第二节点n2,该第二节点n2与第二开关晶体管tsw2与第四开关晶体管tsw4电性连接,且第二开关晶体管tsw2的栅极端是接收第二发光信号em2。第二储存电容cst2是电性连接于电压源vdd以及第二节点n2之间,

用以储存第二节点n2的电压。根据本公开的其他实施例,第二储存电容cst2可电性连接于任何参考电压以及第二节点n2之间。

70.第三开关晶体管tsw3是电性连接于第一数据信号dt1以及第一节点n1之间,且第三开关晶体管tsw3的栅极端是接收扫描信号scn。第四开关晶体管tsw4是电性连接于第二数据信号dt2以及第二节点n2之间,且第四开关晶体管tsw4的栅极端是电性连接扫描信号scn。

71.驱动晶体管td是电性连接至电压源vdd,驱动晶体管td的栅极端电性连接至驱动节点nd,且驱动晶体管td基于驱动节点nd的电压高低,而控制驱动电流id的大小。第一发光单元led1以及第二发光单元led2是电性连接至接地位准vss。图2显示了本公开的像素电路中的晶体管的结构的示意图。其中晶体管的一部分半导体层smc位于源极s与漏极d之间并形成一通道区,栅极gt可与通道区于俯视方向上重叠。如图2所示,通道区的有效通道宽度可定义为其宽度w与间距cl间的比值(w/cl)。根据本公开的一实施例,像素电路中驱动晶体管td比像素电路中其他晶体管大,更具体的说,驱动晶体管td的有效通道宽度远大于其他晶体管的有效通道宽度,例如驱动晶体管td的有效通道宽度与其他晶体管的有效通道宽度的比值可介于4到2000(4≦有效通道宽度比值≦2000)。

72.根据本公开的一些实施例,第一发光单元led1以及第二发光单元led2可以包括发光二极管,例如有机发光二极管(organic light-emitting diode,oled)、次毫米发光二极管(mini light-emitting diode,mini-led)、微型发光二极管(micro light-emitting diode,micro led)、量子点发光二极管(quantum dot light-emitting diode,qled/qdled)等,或包含量子点(quantum dot,qd)、磷光粉(phosphors)、荧光材料(fluorescent material)等材料的光源,但发光单元的类型并不限于此。

73.第一发光晶体管tem1是电性连接于驱动晶体管td以及第一发光单元led1之间,并且第一发光晶体管tem1基于第一发光信号em1,而将驱动电流id提供至第一发光单元led1。第二发光晶体管tem2是电性连接于驱动晶体管td以及第二发光单元led2之间,并且第二发光晶体管tem2基于第二发光信号em2,而将驱动电流id提供至第二发光单元led2。也就是说第一开关晶体管tsw1与第一发光晶体管tem1皆接收第一发光信号em1,第二开关晶体管tsw2与第二发光晶体管tem2皆接收第二发光信号em2。

74.换句话说,图1的第一发光单元led1以及第二发光单元led2是共用相同的驱动晶体管td。由于像素电路的驱动晶体管td的有效通道宽度是远大于其他所有晶体管的有效通道宽度的总和,因此当第一发光单元led1以及第二发光单元led2共用相同的驱动晶体管td时可大幅省下电路布局的面积,或提高显示面板的解析度。须说明的是,虽然本公开以二个发光单元led1、led2共用一个驱动晶体管td作为说明,但本公开并不限于此。根据本公开的其他实施例,任意数量的发光单元亦可共用相同的驱动晶体管。

75.图3是显示根据本公开的一实施例所述的图1的像素电路的波形图。以下针对图3的波形图300的叙述,将搭配图1的像素电路100,以利详细说明。

76.如图3所示,在第一期间a中,扫描信号scn是为低逻辑位准,因此第三开关晶体管tsw3以及第四开关晶体管tsw4基于低逻辑位准的扫描信号scn而导通,使得第一数据信号dt1经第三开关晶体管tsw3而提供至第一节点n1,第二数据信号dt2经第四开关晶体管tsw4而提供至第二节点n2,并且第一储存电容cst1储存第一节点n1的第一数据信号dt1,第二储

存电容cst2储存第二节点n2的第二数据信号dt2。

77.如图3所示,在第二期间b中,扫描信号scn是为高逻辑位准,第一发光信号em1是为低逻辑位准,因此第三开关晶体管tsw3以及第四开关晶体管tsw4基于高逻辑位准的扫描信号scn而不导通,而第一开关晶体管tsw1以及第一发光晶体管tem1基于低逻辑位准的第一发光信号em1而导通。储存于第一储存电容cst1的第一数据信号dt1经第一开关晶体管tsw1而提供至驱动节点nd,驱动晶体管td基于提供至驱动节点nd的第一数据信号dt1而产生驱动电流id,而第一发光晶体管tem1基于第一发光信号em1,而将驱动电流id提供至第一发光单元led1。

78.如图3所示,第二期间b与第一期间a之间具有第一延迟时间d1,其中第一延迟时间d1是大于或等于零。换句话说,第一期间a的扫描信号scn的上升缘可与第二期间b的第一发光信号em1的下降缘同时发生,或者第一期间a的扫描信号scn的上升缘是于第二期间b的第一发光信号em1的下降缘之前发生。换句话说,在一发光周期中,对应扫描信号scn的第三开关晶体管tsw3的导通时间早于对应第一发光信号em1的第一开关晶体管tsw1与第一发光晶体管tem1的导通时间。且第三开关晶体管tsw3的导通时段与第一开关晶体管tsw1(及/或第一发光晶体管tem1)的导通时段之间有一间隔。

79.如图3所示,在第三期间c中,扫描信号scn是为高逻辑位准,第一发光信号em1是为高逻辑位准,且第二发光信号em2是为低逻辑位准,因此第三开关晶体管tsw3以及第四开关晶体管tsw4基于高逻辑位准的扫描信号scn而不导通,第一开关晶体管tsw1以及第一发光晶体管tem1基于高逻辑位准的第一发光信号em1而不导通,第二开关晶体管tsw2以及第二发光晶体管tem2基于低逻辑位准的第二发光信号em2而导通。储存于第二储存电容cst2的第二数据信号dt2经第二开关晶体管tsw2而提供至驱动节点nd,驱动晶体管td基于提供至驱动节点nd的第二数据信号dt2而产生驱动电流id,而第二发光晶体管tem2基于第二发光信号em2,而将驱动电流id提供至第二发光单元led2。

80.如图3所示,第三期间c与第二期间b之间具有第二延迟时间d2,其中第二延迟时间d2是大于或等于零。换句话说,第二期间b的第一发光信号em1的上升缘可与第三期间c的第二发光信号em2的下降缘同时发生,或者第二期间b的第一发光信号em1的上升缘是于第三期间c的第二发光信号em2的下降缘之前发生。

81.图4是显示根据本公开的另一实施例所述的像素电路的电路图。其中,像素电路400的架构与图1的像素电路100相似,其差异处在于,像素电路400是仅由n型晶体管所实现。

82.图5是显示根据本公开的另一实施例所述的像素电路的电路图。如图5所示,像素电路500的架构与图1的像素电路100相似,其差异处在于,像素电路500中的驱动晶体管td是由p型晶体管所实现,而其他晶体管是由n型晶体管所实现。

83.图6是显示根据本公开的另一实施例所述的像素电路的电路图。如图6所示,像素电路600的架构与图1的像素电路100相似,其差异处在于,像素电路600中的驱动晶体管td是由n型晶体管所实现,而其他晶体管是由p型晶体管所实现。

84.由于图4的像素电路400、图5的像素电路500与图6的像素电路600是与图1的像素电路100相似,因此该领域熟知此技艺人士者可根据图1的像素电路100以及n型晶体管与p型晶体管的元件特性,对像素电路400、像素电路500或像素电路600进行类似的操作,使得

像素电路400、像素电路500或像素电路600具有图1的像素电路100的相同功能,故在此不再赘述。另外,本公开的像素电路中,各类型晶体管的设置并不以图1、图4、图5与图6所示的实施例为限。

85.图7是显示根据本公开的另一实施例所述的像素电路700的电路图。如图7所示,像素电路700包括第一开关晶体管tsw1、第一储存电容cst1、第二开关晶体管tsw2、第三开关晶体管tsw3、第二储存电容cst2、第四开关晶体管tsw4、驱动晶体管td、第一发光单元led1、第二发光单元led2、第一发光晶体管tem1以及第二发光晶体管tem2。根据本公开的一实施例,像素电路700是仅由p型晶体管所实现。

86.图7所示的像素电路700与图1所示的像素电路100大多相似,因此像素电路700中各元件之间的电性连接方式在此不再赘述。像素电路700与像素电路100的主要差异在于,第一开关晶体管tsw1与第一发光晶体管tem1分别接收不同的信号en1与em1,而且第二开关晶体管tsw2与第二发光晶体管tem2也分别接收不同的信号en2与em2。更具体的说,第一开关晶体管tsw1的栅极端是接收第一使能信号en1,且第二开关晶体管tsw2的栅极端是接收第二使能信号en2。而第一发光晶体管tem1基于第一发光信号em1,而将驱动电流id提供至第一发光单元led1,且第二发光晶体管tem2基于第二发光信号em2,而将驱动电流id提供至第二发光单元led2。

87.将图7的像素电路700与图1的像素电路100相比,由于像素电路700的第一开关晶体管tsw1以及第一发光晶体管tem1(或第二开关晶体管tsw2以及第二发光晶体管tem2)是利用不同的信号所控制,使得在控制像素电路的时序上较具有弹性。

88.图8是显示根据本公开的一实施例所述的图7的像素电路的波形图。以下针对图8的波形图800的叙述,将搭配图7的像素电路700,以利详细说明。

89.如图8所示,在第四期间e中,扫描信号scn是为低逻辑位准,因此第三开关晶体管tsw3以及第四开关晶体管tsw4基于低逻辑位准的扫描信号scn而导通,使得第一数据信号dt1经第三开关晶体管tsw3而提供至第一节点n1,第二数据信号dt2经第四开关晶体管tsw4而提供至第二节点n2,并且第一储存电容cst1储存第一节点n1的第一数据信号dt1,第二储存电容cst2储存第二节点n2的第二数据信号dt2。

90.如图8所示,在第五期间f中,扫描信号scn是为高逻辑位准,第一使能信号en1是为低逻辑位准,第一发光信号em1是为低逻辑位准,更具体的说,第一使能信号en1以及第一发光信号em1自高逻辑位准转变至低逻辑位准。因此,第三开关晶体管tsw3以及第四开关晶体管tsw4基于高逻辑位准的扫描信号scn而不导通,而第一开关晶体管tsw1基于低逻辑位准的第一使能信号en1而导通,且第一发光晶体管tem1基于低逻辑位准的第一发光信号em1而导通。换句话说,对应扫描信号scn的第三开关晶体管tsw3的导通时间早于对应第一使能信号en1的第一开关晶体管tsw1的导通时间,也早于对应第一发光信号em1的第一发光晶体管tem1的导通时间。

91.储存于第一储存电容cst1的第一数据信号dt1经第一开关晶体管tsw1而提供至驱动节点nd,驱动晶体管td基于提供至驱动节点nd的第一数据信号dt1而产生驱动电流id。此外,第一发光晶体管tem1基于第一发光信号em1,而将驱动电流id提供至第一发光单元led1。

92.如图8所示,第五期间f与第四期间e之间具有第三延迟时间d3,其中第三延迟时间

d3是大于或等于零。换句话说,第四期间e的扫描信号scn的上升缘可与第五期间f的第一使能信号en1的下降缘同时发生,或者第四期间e的扫描信号scn的上升缘是于第五期间f的第一使能信号en1的下降缘之前发生。

93.如图8所示,在第六期间g中,第一使能信号en1是为高逻辑位准,且第一发光信号em1维持在低逻辑位准。因此,当第一开关晶体管tsw1基于高逻辑位准的第一使能信号en1而不导通时,经第一开关晶体管tsw1所提供至驱动节点nd的第一数据信号dt1是储存于驱动晶体管td本身的寄生电容,使得驱动晶体管td依然基于驱动节点nd的第一数据信号dt1而产生驱动电流id,并透过第一发光晶体管tem1而将驱动电流id提供至第一发光单元led1。须说明的是,在一些实施例中,驱动晶体管td可另外电性连接一电容以储存由第一开关晶体管tsw1所提供的第一数据信号dt1,使得驱动晶体管td依然可基于驱动节点nd的第一数据信号dt1而产生驱动电流id。

94.如图8所示,在第七期间h中,扫描信号scn、第一使能信号en1以及第一发光信号em1是为高逻辑位准,并且第二使能信号en2以及第二发光信号em2自高逻辑位准转变至低逻辑位准。

95.因此,第三开关晶体管tsw3以及第四开关晶体管tsw4基于高逻辑位准的扫描信号scn而不导通,第一开关晶体管tsw1基于高逻辑位准的第一使能信号en1而不导通,第一发光晶体管tem1基于高逻辑位准的第一发光信号em1而不导通,第二开关晶体管tsw2基于低逻辑位准的第二使能信号en2而导通,第二发光晶体管tem2基于低逻辑位准的第二发光信号em2而导通。

96.储存于第二储存电容cst2的第二数据信号dt2经第二开关晶体管tsw2而提供至驱动节点nd,驱动晶体管td基于提供至驱动节点nd的第二数据信号dt2而产生驱动电流id。此外,第二发光晶体管tem2基于第二发光信号em2,而将驱动电流id提供至第二发光单元led2。

97.如图8所示,第七期间h与第六期间g之间具有第四延迟时间d4,其中第四延迟时间d4是大于或等于零。换句话说,第六期间g的第一发光信号em1的上升缘可与第七期间h的第二使能信号en2的下降缘以及第二发光信号em2的下降缘可同时发生,或者第六期间g的第一发光信号em1的上升缘是于第七期间h的第二使能信号en2的下降缘以及第二发光信号em2的下降缘之前发生。

98.如图8所示,在第八期间j中,第二使能信号en2是为高逻辑位准,且第二发光信号em2维持在低逻辑位准。因此,当第二开关晶体管tsw2基于高逻辑位准的第二使能信号en2而不导通时,经第二开关晶体管tsw2所提供至驱动节点nd的第二数据信号dt2是储存于驱动晶体管td的寄生电容,使得驱动晶体管td依然基于驱动节点nd的第二数据信号dt2而产生驱动电流id,并透过第二发光晶体管tem2而将驱动电流id提供至第二发光单元led2。

99.图9是显示根据本公开的另一实施例所述的图7的像素电路的波形图。以下针对图9的波形图900的叙述,将搭配图7的像素电路700,以利详细说明。

100.如图9所示,在第九期间l中,扫描信号scn是为低逻辑位准,因此第三开关晶体管tsw3以及第四开关晶体管tsw4基于低逻辑位准的扫描信号scn而导通,使得第一数据信号dt1经第三开关晶体管tsw3而提供至第一节点n1,第二数据信号dt2经第四开关晶体管tsw4而提供至第二节点n2,并且第一储存电容cst1储存第一节点n1的第一数据信号dt1,第二储

存电容cst2储存第二节点n2的第二数据信号dt2。

101.如图9所示,在第十期间m中,扫描信号scn是为高逻辑位准,第一使能信号en1是为低逻辑位准,并且当扫描信号scn自低逻辑位准转变至高逻辑位准时,第一使能信号en1自高逻辑位准转变至低逻辑位准。因此,第三开关晶体管tsw3以及第四开关晶体管tsw4基于高逻辑位准的扫描信号scn而不导通,而第一开关晶体管tsw1基于低逻辑位准的第一使能信号en1而导通。储存于第一储存电容cst1的第一数据信号dt1经第一开关晶体管tsw1而提供至驱动节点nd,驱动晶体管td基于提供至驱动节点nd的第一数据信号dt1而产生驱动电流id。须说明的是,虽然依图9所示,扫描信号scn自低逻辑位准转变至高逻辑位准与第一使能信号en1自高逻辑位准转变至低逻辑位准的时间点为同时,但在一些实施例中,两信号逻辑位准改变的时间点之间可以具有如图8中所示的延迟时间。

102.如图9所示,在第十一期间n中,第一使能信号en1是为高逻辑位准,且第一发光信号em1是为低逻辑位准,并且当第一使能信号en1自低逻辑位准转变至高逻辑位准时,第一发光信号em1自高逻辑位准转变至低逻辑位准。因此,当第一开关晶体管tsw1基于高逻辑位准的第一使能信号en1而不导通时,经第一开关晶体管tsw1所提供至驱动节点nd的第一数据信号dt1是储存于驱动晶体管td的寄生电容,使得驱动晶体管td依然基于驱动节点nd的第一数据信号dt1而产生驱动电流id。此外,第一发光晶体管tem1基于第一发光信号em1,而将驱动电流id提供至第一发光单元led1。须说明的是,虽然依图9所示,第一使能信号en1自低逻辑位准转变至高逻辑位准与第一发光信号em1自高逻辑位准转变至低逻辑位准的时间点为同时,但在一些实施例中,两信号逻辑位准改变的时间点之间可以具有一延迟时间。另外,由图9可知,在一发光周期中,对应扫描信号scn的第三开关晶体管tsw3的导通时间早于对应第一使能信号en1的第一开关晶体管tsw1的导通时间,而第一开关晶体管tsw1的导通时间则早于对应第一发光信号em1的第一发光晶体管tem1的导通时间。

103.如图9所示,在第十二期间o中,第一发光信号em1是为高逻辑位准,第二使能信号en2是为低逻辑位准,并且当第一发光信号em1自低逻辑位准转变至高逻辑位准时,第二使能信号en2是自高逻辑位准转变至低逻辑位准。须说明的是,虽然依图9所示,第一发光信号em1自低逻辑位准转变至高逻辑位准与第二使能信号en2自高逻辑位准转变至低逻辑位准的时间点为同时,但在一些实施例中,两信号逻辑位准改变的时间点之间可以具有一延迟时间。

104.因此,第一发光晶体管tem1基于高逻辑位准的第一发光信号em1而不导通,第二开关晶体管tsw2基于低逻辑位准的第二使能信号en2而导通,使得储存于第二储存电容cst2的第二数据信号dt2经第二开关晶体管tsw2而提供至驱动节点nd。驱动晶体管td基于提供至驱动节点nd的第二数据信号dt2而产生驱动电流id。

105.如图9所示,在第十三期间p中,第二使能信号en2是为高逻辑位准,第二发光信号em2是为低逻辑位准,并且当第二使能信号en2自低逻辑位准转变至高逻辑位准时,第二发光信号em2自高逻辑位准转变至低逻辑位准。因此,当第二开关晶体管tsw2基于高逻辑位准的第二使能信号en2而不导通时,经第二开关晶体管tsw2所提供至驱动节点nd的第二数据信号dt2是储存于驱动晶体管td的寄生电容,使得驱动晶体管td依然基于驱动节点nd的第二数据信号dt2而产生驱动电流id。此外,第二发光晶体管tem2基于低逻辑位准的第二发光信号em2,而将驱动电流id提供至第二发光单元led2。须说明的是,虽然依图9所示,第一发

光信号em1自低逻辑位准转变至高逻辑位准与第二使能信号en2自高逻辑位准转变至低逻辑位准的时间点为同时,但在一些实施例中,两信号逻辑位准改变的时间点之间可以具有一延迟时间。

106.将图9的波形图900与图8的波形图800相比,图9中第一发光信号em1自高逻辑位准转变至低逻辑位准的时间点比第一使能信号en1自高逻辑位准转变至低逻辑位准的时间晚,相似地,第二发光信号em2自高逻辑位准转变至低逻辑位准的时间点比第二使能信号en2自高逻辑位准转变至低逻辑位准的时间晚。这使得当驱动晶体管td基于第一数据信号dt1或第二数据信号dt2而输出稳定的驱动电流id时,第一发光晶体管tem1以及第二发光晶体管tem2才将驱动电流id分别提供至第一发光单元led1以及第二发光晶体管led2。因此,波形图900的操作方式将有助于提升发光单元的亮度的稳定性。

107.图10是显示根据本公开的另一实施例所述的像素电路的电路图。将图10所示的像素电路1000与图7的像素电路700相比,像素电路1000是仅由n型晶体管所实现。然而,该领域熟知此技艺人士者可根据图7的像素电路700、图8的波形图800、图9的波形图900的操作原理以及n型晶体管与p型晶体管的元件特性,对像素电路1000进行类似的操作,使得像素电路1000具有图7的像素电路700的相同功能,故在此不再重复赘述。另外,本公开的像素电路中,各类型晶体管类型的设置与变化并不以图10所示的实施例为限,在一些实施例中,像素电路可同时包含一个或多个n型晶体管与一个或多个p型晶体管。

108.本公开在此提出了电子装置以及像素电路,透过多个发光单元共用相同的驱动晶体管,以降低整体像素电路的布局面积。

109.此外,透过利用不同的控制信号来控制第一开关晶体管以及第一发光晶体管(或为第二开关晶体管以及第二发光晶体管),有助于增加像素电路的控制弹性。并且,驱动晶体管可先基于第一数据信号或第二数据信号而产生驱动电流,待驱动电流稳定时,再提供至第一发光单元或第二发光单元,因而提升发光单元的亮度的稳定性。

110.虽然本公开的实施例及其优点已公开如上,但应该了解的是,任何本领域技术人员,在不脱离本公开的精神和范围内,当可作组合、更动、替代与润饰。此外,本公开的保护范围并未局限于说明书内所述特定实施例中的制程、机器、制造、物质组成、装置、方法及步骤,任何本领域技术人员可从本公开一些实施例的揭示内容中理解现行或未来所发展出的制程、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结果皆可根据本公开一些实施例使用。因此,本公开的保护范围包括上述制程、机器、制造、物质组成、装置、方法及步骤。另外,每一权利要求构成个别的实施例,且本公开的保护范围也包括各个权利要求及实施例的组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1