一种扫描电路及显示电路的制作方法

本发明涉及显示驱动,尤其涉及一种扫描电路及显示电路。

背景技术:

1、在平板显示技术中,用于显示的阵列基板,也即像素补偿电路,由多个像素行组成,每个像素行由多个发光二极管构成,每一行像素行都由一个goa驱动单元(gate driveron array,阵列基板行驱动扫描电路)和一个eoa驱动单元(emitgate driver on array,发光控制信号驱动电路)来控制发光二极管导通和关闭,以及显示不同亮度和颜色;现有技术中,每一像素行均由一个goa驱动单元发送扫描信号实现像素行中二极管的导通和关断,一个eoa驱动单元发送光控制信号实现控制二极管是否发光,而这种双电路控制导致电路结构复杂,为了容纳上述电路,使得显示屏的边框面积必须足够大,这就使得显示屏的成本增加,也降低了美观性。

技术实现思路

1、基于此,有必要针对上述问题,提出了一种扫描电路及显示电路。

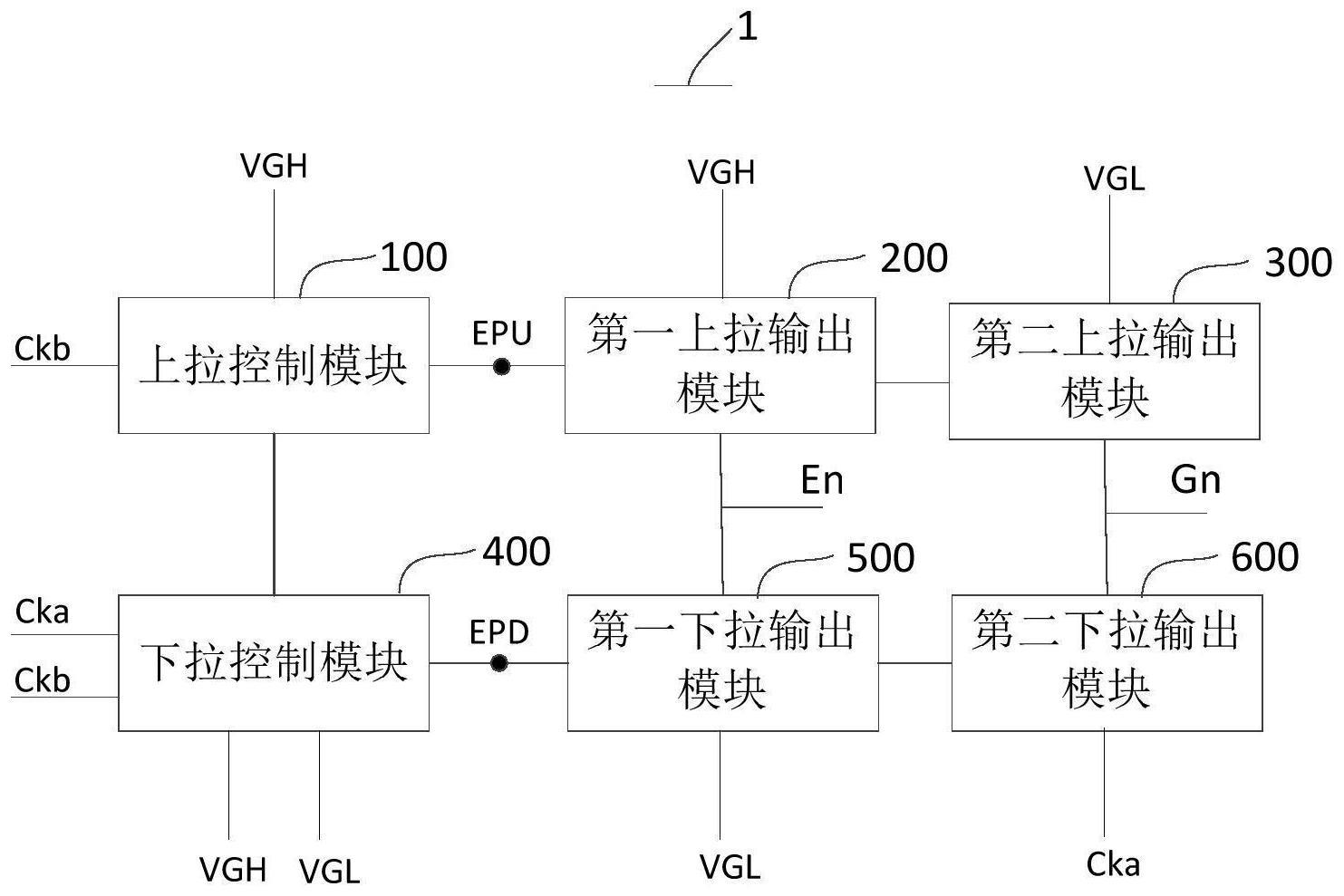

2、一种扫描电路,用于驱动像素补偿电路中的像素行,所述扫描电路包括:

3、上拉控制模块、通过第一节点与所述上拉控制模块连接的第一上拉输出模块和第二上拉输出模块;所述上拉控制模块与信号发生单元和下拉控制模块连接;所述第一上拉输出模块用于输出控制所述像素行是否发光的光控制信号;所述第二上拉输出模块用于输出控制发光数据写入所述像素行的扫描信号;

4、下拉控制模块、通过第二节点与所述下拉控制模块连接的第一下拉输出模块和第二下拉输出模块;所述下拉控制模块与所述信号发生单元和所述上拉控制模块连接;所述第一下拉输出模块用于输出控制所述像素行是否发光的光控制信号;所述第二下拉输出模块用于输出控制发光数据写入所述像素行的扫描信号;

5、在上拉阶段,所述第一上拉输出模块及所述第二上拉输出模块分别输出所述光控制信号及所述扫描信号,所述第一下拉输出模块及所述第二下拉输出模块截止;

6、在下拉阶段,所述第一上拉输出模块及所述第二上拉输出模块截止,所述第一下拉输出模块及所述第二下拉输出模块分别输出所述光控制信号及所述扫描信号。

7、在一个实施例中,所述信号发生单元用于向所述上拉控制模块输出第二电平信号和常高电平;向所述第一上拉输出模块输出常高电平;向所述第二上拉输出模块输出常低电平;向所述下拉控制模块输出第一电平信号、第二电平信号、常高电平和常低电平;向所述第一下拉输出模块输出常低电平;向所述第二下拉输出模块输出第一电平信号。

8、在一个实施例中,所述第一电平信号和所述第二电平信号在同一时间其电平相反;

9、所述上拉阶段包括:初始化阶段和信号维持阶段;所述下拉阶段包括信号输出阶段,其中:

10、所述初始化阶段,用于对所述像素行进行初始化,以消除上一阶段存储的发光数据,所述发光数据为所述信号发生单元向所述像素行发送的,用于控制所述像素行的亮度;

11、所述信号输出阶段,用于向所述像素行输出所述发光数据;和

12、所述信号维持阶段,用于向所述像素行输出所述光控制信号,以控制所述像素行发光。

13、在一个实施例中,在所述初始化阶段,所述第二电平信号为高电平,所述上拉控制模块控制所述第一节点为高电平,以使所述第一上拉输出模块输出高电平的光控制信号,使所述第二上拉输出模块输出低电平的扫描信号;

14、所述第一电平信号为低电平,上一像素行对应的扫描电路在所述维持阶段输出的扫描信号为高电平,并输出给所述下拉控制模块,以使所述第一下拉输出模块和第二下拉输出模块截止。

15、在一个实施例中,在所述信号输出阶段,所述第二电平信号为高电平,所述下拉控制模块控制所述第二节点为高电平;以使所述第一下拉输出模块输出低电平的光控制信号,使所述第二下拉输出模块输出高电平的扫描信号;

16、所述第一电平信号为低电平,所述上拉控制模块控制所述第一节点为低电平,以使所述第一上拉输出模块和第二上拉输出模块截止。

17、在一个实施例中,在所述信号维持阶段,所述第二电平信号为高电平,所述上拉控制模块控制所述第一节点为高电平,以使所述第一上拉输出模块输出高电平的光控制信号,使所述第二上拉输出模块输出低电平的扫描信号;

18、所述下拉控制模块接收所述上拉控制模块输出的常高电平后导通,并根据接入的所述常低电平控制所述第二节点为低电平,以使所述第一下拉输出模块和第二下拉输出模块截止。

19、在一个实施例中,所述上拉控制模块包括:第一薄膜晶体管;

20、所述第一上拉输出模块包括:第二薄膜晶体管;

21、所述第二上拉输出模块包括:第三薄膜晶体管;

22、所述第一薄膜晶体管的栅极接入所述第二电平信号,所述第一薄膜晶体管的第一极与所述下拉控制模块连接,所述第一薄膜晶体管的第二极接入所述常高电平;

23、所述第二薄膜晶体管的栅极与所述第一薄膜晶体管的第二极连接于所述第一节点,所述第二薄膜晶体管的第一极输出所述光控制信号,所述第二薄膜晶体管的第二极接入所述常高电平;

24、所述第三薄膜晶体管的栅极与所述第一节点连接,所述第三薄膜晶体管的第一极输出所述扫描信号,所述第三薄膜晶体管的第二极接入所述常低电平。

25、在一个实施例中,所述下拉控制模块包括:第四薄膜晶体管、第五薄膜晶体管、第六薄膜晶体管、第七薄膜晶体管、第十薄膜晶体管、第十一薄膜晶体管和第十二薄膜晶体管;

26、所述第五薄膜晶体管和所述第六薄膜晶体管的栅极均与所述第十二薄膜晶体管的第二极连接于所述第二节点,所述第五薄膜晶体管的第一极与所述第六薄膜晶体管的第二极连接,所述所述第五薄膜晶体管的第二极与所述第一薄膜晶体管的第一极连接;所述第六薄膜晶体管的第一极与所述第四薄膜晶体管的第一极连接;

27、所述第四薄膜晶体管的栅极与所述第一薄膜晶体管的第一极连接,所述第四薄膜晶体管的第二极接入所述常高电平;

28、所述第七薄膜晶体管的栅极与所述第十薄膜晶体管的第一极连接,所述第七薄膜晶体管的第一极与所述第二节点连接,所述第七薄膜晶体管的第二极接入所述第一电平信号;

29、所述第十薄膜晶体管的栅极接入所述第二电平信号,所述第十薄膜晶体管的第二极接入上一像素行对应的扫描电路输出的扫描信号;

30、所述第十一薄膜晶体管的栅极与所述第一节点连接,所述第十一薄膜晶体管的第一极接入所述常低电平,所述第十一薄膜晶体管的第二极与所述第二节点连接;

31、所述第十二薄膜晶体管的栅极接入所述第二电平信号,所述第十二薄膜晶体管的第一极接入所述常低电平。

32、在一个实施例中,所述第一下拉输出模块包括:第十三薄膜晶体管;

33、所述第二下拉输出模块包括:第十四薄膜晶体管;

34、所述第十三薄膜晶体管的栅极与所述第二节点连接,所述第十三薄膜晶体管的第一极接入所述常低电平,所述第十三薄膜晶体管的第二极输出所述光控制信号;

35、所述第十四薄膜晶体管的栅极与所述第二节点连接,所述第十四薄膜晶体管的第一极接入所述第一电平信号,所述第十四薄膜晶体管的第二极输出所述扫描信号。

36、在一个实施例中,所述第一下拉输出模块包括:第十三薄膜晶体管;

37、所述第二下拉输出模块包括:第十四薄膜晶体管;

38、所述第十三薄膜晶体管的栅极与所述第二节点连接,所述第十三薄膜晶体管的第一极接入所述常低电平,所述第十三薄膜晶体管的第二极输出所述光控制信号;

39、所述第十四薄膜晶体管的栅极与所述第七薄膜晶体管的栅极连接于第三节点,所述第十四薄膜晶体管的第一极接入所述第一电平信号,所述第十四薄膜晶体管的第二极输出所述扫描信号。

40、一种显示电路,包括多个如权利要求1-9任一项所述的扫描电路、信号发生单元和像素补偿电路;

41、所述的扫描电路接收所述信号发生单元输出的第一电平信号、第二电平信号、常高电平和常低电平;并在所述第一电平信号、第二电平信号、常高电平和常低电平的作用下向所述像素补偿电路输出扫描信号和光控制信号,以控制所述像素补偿电路发光。

42、在一个实施例中,所述像素补偿电路包括多个像素行,每个扫描电路通过控制线向两个相邻的所述像素行输出扫描信号和光控制信号;

43、所述信号发生单元通过数据线向每个像素行的二极管发送发光数据,每个所述数据线传输的发光数据不同,则控制所述二极管的发光亮度不同。

44、实施本发明实施例,将具有如下有益效果:

45、本发明采用上拉控制模块、第一上拉输出模块、第二上拉输出模块、下拉控制模块、第一下拉输出模块和第二下拉输出模块构成一个简化的单电路,以实现向像素补偿电路发送控制其导通或关断的扫描信号以及控制其发光的光控制信号,替代了现有技术中驱动像素补偿电路导通、关闭以及发光的双电路,减小了显示屏边框的面积,降低了扫描电路的成本。

- 还没有人留言评论。精彩留言会获得点赞!