像素电路的制作方法

1.本发明提供一种利用多个晶体管和多个电容延长补偿时间且能使发光单元完全关闭来提升画面对比度的像素电路。

背景技术:

2.有机发光二极管具有自发光、高亮度、高对比度、制程简单等优点,已逐渐应用于各种类型显示器。有机发光二极管本身为电流驱动组件,通过给予像素电路不同数据电压产生不同驱动电流来控制有机发光二极管的亮度,然而,像素电路的晶体管因为关闭时仍有漏电流,导致有机发光二极管有闪烁的现象,导致画面对比度的下降。

3.综观前所述,本发明之发明者思索并设计一种像素电路,以期针对习知技术之缺失加以改善,进而增进产业上之实施利用。

技术实现要素:

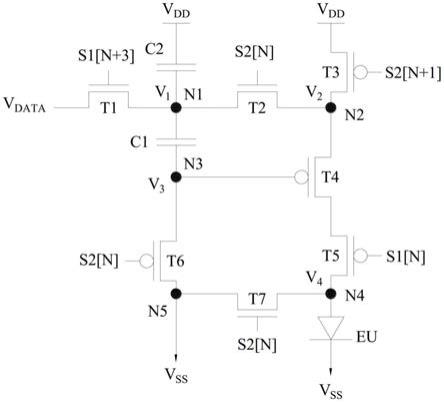

4.基于上述目的,本发明提供一种像素电路,其包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第一电容、第二电容以及发光单元。第一晶体管的第一端耦接数据线,第一晶体管的控制端耦接后三级第一信号线,第一晶体管的第二端耦接第一节点。第二晶体管的第一端耦接第一节点,第二晶体管的控制端耦接本级第二信号线,第二晶体管的第二端耦接第二节点。第一电容的一端耦接第一节点,第一电容的另一端耦接第三节点。第二电容的一端耦接第一节点,第二电容的另一端耦接第一电压线。第三晶体管的第一端耦接第一电压线,第三晶体管的控制端耦接后一级第二信号线,第三晶体管的第二端耦接第二节点。第四晶体管的第一端耦接第二节点,第四晶体管的控制端耦接第三节点。第五晶体管的第一端耦接第四晶体管的第二端,第五晶体管的控制端耦接本级第一信号线,第五晶体管的第二端耦接第四节点。第六晶体管的第一端耦接第三节点,第六晶体管的控制端耦接本级第二信号线,第六晶体管的第二端耦接第五节点,第五节点耦接第二电压线。第七晶体管的第一端耦接第四节点,第七晶体管的控制端耦接本级第二信号线,第七晶体管的第二端耦接第四节点。发光单元的一端耦接第四节点,发光单元的另一端耦接第二电压线。

5.在本发明的实施例中,第一晶体管、第二晶体管、第六晶体管和第七晶体管的材料包括第一材料,第三晶体管、第四晶体管和第五晶体管的材料包括第二材料,第一材料相异于第二材料。

6.在本发明的实施例中,第一晶体管、第二晶体管、第六晶体管和第七晶体管为n型晶体管,第三晶体管、第四晶体管和第五晶体管为p型晶体管。

7.在本发明的实施例中,本级第一信号线传输第一信号,本级第二信号线传输第二信号,后三级第一信号线传输后三级第一信号,后一级第二信号线传输后一级第二信号。

8.在本发明的实施例中,在重置期间,第一信号使第五晶体管关闭,第二信号使第二晶体管、第六晶体管和第七晶体管导通,后三级第一信号使第一晶体管关闭,后一级第二信

号使第三晶体管导通,第一节点的电压和第二节点的电压相同于第一电压线所传输的第一电压,第三节点的电压和第四节点的电压相同于第二电压线所传输的第二电压。

9.在本发明的实施例中,在补偿期间,第一信号使第五晶体管导通,第二信号使第二晶体管、第六晶体管和第七晶体管导通,后三级第一信号使第一晶体管关闭,后一级第二信号使第三晶体管关闭,第一节点的电压和第二节点的电压皆大于第二电压线所传输的第二电压,第三节点的电压和第四节点的电压相同于第二电压。

10.在本发明的实施例中,在数据输入期间,第一信号使第五晶体管关闭,第二信号使第二晶体管、第六晶体管和第七晶体管关闭,后三级第一信号使第一晶体管导通,后一级第二信号使第三晶体管关闭,第一节点的电压为数据线所传输的数据电压,第三节点的电压小于数据电压,第二节点的电压大于第二电压线所传输的第二电压,第四节点的电压相同于第二电压。

11.在本发明的实施例中,在发光期间,第一信号使第五晶体管导通,第二信号使第二晶体管、第六晶体管和第七晶体管关闭,后三级第一信号使第一晶体管关闭,后一级第二信号使第三晶体管导通,第一节点的电压为数据线所传输的数据电压,第三节点的电压小于数据电压,第二节点的电压相同于第一电压线所传输的第一电压,发光单元发光。

12.承上所述,本发明的像素电路,可延长补偿时间来提升补偿准确度,于重置阶段可使发光单元完全关闭以提升画面对比度。

附图说明

13.图1为本发明的像素电路的配置图。

14.图2a为本发明的像素电路于重置期间的示意图。

15.图2b为本发明的像素电路于重置期间的信号波形图。

16.图3a为本发明的像素电路于补偿期间的示意图。

17.图3b为本发明的像素电路于补偿期间的信号波形图。

18.图4a为本发明的像素电路于数据输入期间的示意图。

19.图4b为本发明的像素电路于数据输入期间的信号波形图。

20.图5a为本发明的像素电路于发光期间的示意图。

21.图5b为本发明的像素电路于发光期间的信号波形图。

22.图6为本发明的像素电路的第一节点的电压之变化图。

23.【符号说明】

24.c1:第一电容

25.c2:第二电容

26.eu:发光单元

27.n1:第一节点

28.n2:第二节点

29.n3:第三节点

30.n4:第四节点

31.n5:第五节点

32.p1:重置期间

33.p2:补偿期间

34.p3:数据输入期间

35.p4:发光期间

36.s1[n]:本级第一信号线

[0037]

s2[n]:本级第二信号线

[0038]

s1[n+3]:后三级第一信号线

[0039]

s2[n+1]:后一级第二信号线

[0040]

t1:第一晶体管

[0041]

t2:第二晶体管

[0042]

t3:第三晶体管

[0043]

t4:第四晶体管

[0044]

t5:第五晶体管

[0045]

t6:第六晶体管

[0046]

t7:第七晶体管

[0047]v1

:第一节点的电压

[0048]v2

:第二节点的电压

[0049]v3

:第三节点的电压

[0050]v4

:第四节点的电压

[0051]vdata

:数据电压

[0052]vdd

:第一电压

[0053]vss

:第二电压

[0054]

δv

th

:第四晶体管的临界电压变异量

具体实施方式

[0055]

本发明之优点、特征以及达到之技术方法将参照例示性实施例及所附图式进行更详细地描述而更容易理解,且本发明可以不同形式来实现,故不应被理解仅限于此处所陈述的实施例,相反地,对所属技术领域具有通常知识者而言,所提供的实施例将使本揭露更加透彻与全面且完整地传达本发明的范畴,且本发明将仅为所附加的申请专利范围所定义。

[0056]

应当理解的是,尽管术语「第一」、「第二」等在本发明中可用于描述各种组件、部件、区域、层及/或部分,但是这些组件、部件、区域、层及/或部分不应受这些术语的限制。这些术语仅用于将一个组件、部件、区域、层及/或部分与另一个组件、部件、区域、层及/或部分区分开。因此,下文讨论的「第一组件」、「第一部件」、「第一区域」、「第一层」及/或「第一部分」可以被称为「第二组件」、「第二部件」、「第二区域」、「第二层」及/或「第二部分」,而不悖离本发明的精神和教示。

[0057]

另外,术语「包括」及/或「包含」指所述特征、区域、整体、步骤、操作、组件及/或部件的存在,但不排除一个或多个其他特征、区域、整体、步骤、操作、组件、部件及/或其组合的存在或添加。

[0058]

除非另有定义,本发明所使用的所有术语(包括技术和科学术语)具有与本发明所

属技术领域的普通技术人员通常理解的相同含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的定义,并且将不被解释为理想化或过度正式的意义,除非本文中明确地这样定义。

[0059]

请参阅图1,其为本发明的像素电路的配置图。如图1所示,本发明的像素电路,其包括第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6、第七晶体管t7、第一电容c1、第二电容c2以及发光单元eu。第一晶体管t1的第一端耦接数据线(其为数据电压v

data

对应的电压线),第一晶体管t1的控制端耦接后三级第一信号线s1[n+3],第一晶体管t1的第二端耦接第一节点n1。第二晶体管t2的第一端耦接第一节点n1,第二晶体管t2的控制端耦接本级第二信号线s2[n],第二晶体管t2的第二端耦接第二节点n2。第一电容c1的一端耦接第一节点n1,第一电容c1的另一端耦接第三节点n3。第二电容c2的一端耦接第一节点n1,第二电容c2的另一端耦接第一电压线(其为第一电压vdd对应的电压线)。第三晶体管t3的第一端耦接第一电压线,第三晶体管t3的控制端耦接后一级第二信号线s2[n+1],第三晶体管t3的第二端耦接第二节点n2。第四晶体管t4的第一端耦接第二节点n2,第四晶体管t4的控制端耦接第三节点n3。第五晶体管t5的第一端耦接第四晶体管t4的第二端,第五晶体管t5的控制端耦接本级第一信号线s1[n],第五晶体管t5的第二端耦接第四节点n4。第六晶体管t6的第一端耦接第三节点n3,第六晶体管t6的控制端耦接本级第二信号线s2[n],第六晶体管t6的第二端耦接第五节点n5,第五节点n5耦接第二电压线(其为第二电压vss对应的电压线)。第七晶体管t7的第一端耦接第四节点n4,第七晶体管t7的控制端耦接本级第二信号线s2[n],第七晶体管t7的第二端耦接第四节点n4。发光单元eu的一端耦接第四节点n4,发光单元eu的另一端耦接第二电压线(其为第二电压vss对应的电压线)。

[0060]

其中,本级第一信号线s1[n]传输第一信号,本级第二信号线s2[n]传输第二信号,后三级第一信号线s1[n+3]传输后三级第一信号,后一级第二信号线s2[n+1]传输后一级第二信号。

[0061]

其中,第一晶体管t1、第二晶体管t2、第六晶体管t6和第七晶体管t7的材料包括第一材料,第一材料可包括氧化铟锡(indium tin oxide,ito)、氧化锌(zno)、氧化铝镓铟锡(algainsno)、氧化铝锌(aluminium-doped zinc oxide,azo)、氧化锡(sno2)、氧化铟(in2o3)或氧化铟镓锌(indium gallium zinc oxide,igzo),第三晶体管t3、第四晶体管t4和第五晶体管t5的材料包括第二材料,第二材料包括多晶硅或低温多晶硅(low temperature poly-silicon,ltps),第一材料相异于第二材料。第一晶体管t1、第二晶体管t2、第六晶体管t6和第七晶体管t7为n型晶体管,第三晶体管t3、第四晶体管t4和第五晶体管t5为p型晶体管。由于第一电容c1和第二电容c2的附近为导电氧化物所形成的晶体管,可改善漏电流现象,进而改善漏电流造成显示器闪烁的问题。

[0062]

第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6、第七晶体管t7的种类可包括底闸极式(bottom-gate)晶体管、顶闸极式(top-gate)晶体管或立体式的晶体管(vertical tft),当然其也可为其他合适的晶体管,并未局限于本发明所列举的范围。发光单元eu可包括有机发光二极管或无机发光二极管,无机发光二极管可包括水平式发光二极管、覆晶式发光二极管、垂直式发光二极管,当然其也可为其他类型的无机发光二极管,并未局限于本发明所列举的范围。

[0063]

请参阅图2a和图2b,为本发明的像素电路于重置期间的示意图和本发明的像素电路于重置期间的信号波形图。如图2a和图2b所示,在重置期间p1,第一信号使第五晶体管t5关闭,第二信号使第二晶体管t2、第六晶体管t6和第七晶体管t7导通,后三级第一信号使第一晶体管t1关闭,后一级第二信号使第三晶体管t3导通,第一节点n1的电压v1和第二节点n2的电压v2相同于第一电压线所传输的第一电压v

dd

,第三节点n3的电压v3和第四节点n4的电压v4相同于第二电压线所传输的第二电压v

ss

,第三节点n3的电压v3使第四晶体管t4的第一端s4和控制端g4之间的偏压大于其临界电压,使第四晶体管t4导通而重置,由于第四节点n4的电压v4相同于第二电压vss,使发光单元eu逆偏而不发光。

[0064]

请参阅图3a和图3b,其为本发明的像素电路于补偿期间的示意图以及本发明的像素电路于补偿期间的信号波形图。如图3a和图3b所示,在补偿期间p2,第一信号使第五晶体管t5导通,第二信号使第二晶体管t2、第六晶体管t6和第七晶体管t7导通,后三级第一信号使第一晶体管t1关闭,后一级第二信号使第三晶体管t3关闭,由于第一晶体管t1关闭,补偿期间p2的长短不受数据电压v

data

所影响,可将补偿期间p2加以延长,第三节点n3的电压v3和第四节点n4的电压v4相同于第二电压v

ss

,因第五晶体管t5导通,使第二节点n2的电压v2为第二电压v

ss

和第四晶体管t4的临界电压之和,第四晶体管t4的第一端s4和控制端g4之间的偏压大于其临界电压,第四晶体管t4进而导通,第一节点n1的电压v1的电压等于第二节点n2的电压v2,当第一电容c1和第二电容c2充饱电时,第一节点n1的电压v1稳定,进而使第二节点n2的电压v2稳定而等同于第一节点n1的电压v1,第一节点n1的电压v1和第二节点n2的电压v2皆大于第二电压线所传输的第二电压vss。

[0065]

请参阅图4a和图4b,其为本发明的像素电路于数据输入期间的示意图以及本发明的像素电路于数据输入期间的信号波形图。如图4a和图4b所示,在数据输入期间p3,第一信号使第五晶体管t5关闭,第二信号使第二晶体管t2、第六晶体管t6和第七晶体管t7关闭,后三级第一信号使第一晶体管t1导通,后一级第二信号使第三晶体管t3关闭,由于第五晶体管t5和第三晶体管t3的关闭,使第四晶体管t4的第一端并无电压输入,进而使第四晶体管t4关闭,由于第一晶体管t1的导通,使数据电压v

data

输入至本发明的像素电路,第一节点n1的电压v1为数据线所传输的数据电压v

data

,第二节点n2的电压v2因补偿期间p2的第一电容c1和第二电容c2充完电的缘故而维持第二电压v

ss

和第四晶体管t4的临界电压之和,第二节点n2的电压v2大于第二电压线所传输的第二电压v

ss

,第三节点n3的电压v3为数据电压v

data

和第四晶体管t4的临界电压之差而小于数据电压v

data

,第四节点n4的电压v4相同于第二电压v

ss

。

[0066]

请参阅图5a和图5b,其为本发明的像素电路于发光期间的示意图以及本发明的像素电路于发光期间的信号波形图。如图5a和图5b所示,在发光期间p4,第一信号使第五晶体管t5导通,第二信号使第二晶体管t2、第六晶体管t6和第七晶体管t7关闭,后三级第一信号使第一晶体管t1关闭,后一级第二信号使第三晶体管t3导通,第一节点n1的电压v1为数据线所传输的数据电压v

data

,第二节点n2的电压v2相同于第一电压线所传输的第一电压v

dd

,第三节点n3的电压v3为数据电压v

data

和第四晶体管t4的临界电压之差而小于数据电压v

data

,第四晶体管t4进而导通,发光单元eu顺偏而发光,发光单元eu的电流为k为第四晶体管t4的制程参数,发光单元eu的电流不受第四晶体管t4的

临界电压所影响。

[0067]

请参阅图6,其为本发明的像素电路的第一节点的电压的变化图。如图6所示,随着第四晶体管t4的临界电压减小(第四晶体管t4的临界电压δv

th

=-0.5),第一节点n1的电压v1跟随第二电容c2的充放电有所起伏,第一节点n1的电压v1相对于原先未变化第四晶体管t4的临界电压时的第一节点n1的电压v1增加,第三节点n3的电压v3跟随第一电容c1的充放电有所起伏,第三节点n3的电压v3相对于原先未变化第四晶体管t4的临界电压时的第三节点n3的电压v3减少。随着第四晶体管t4的临界电压增加(第四晶体管t4的临界电压δv

th

=+0.5),第一节点n1的电压v1跟随第二电容c2的充放电有所起伏,第一节点n1的电压v1相对于原先未变化第四晶体管t4的临界电压时的第一节点n1的电压v1减少,第三节点n3的电压v3跟随第一电容c1的充放电有所起伏,第三节点n3的电压v3相对于原先未变化第四晶体管t4的临界电压时的第三节点n3的电压v3增加。藉由补偿期间p2的第一节点n1的电压v1的数值变化,得知第四晶体管t4的临界电压的变化,在发光期间p4的第一节点n1的电压v1成功通过第一电容c1耦合至第三节点n3的电压v3。

[0068]

承上所述,本发明的像素电路,可延长补偿期间p2来提升补偿准确度,于重置期间p1可使发光单元eu完全关闭以提升画面对比度。

[0069]

以上所述仅为举例性,而非为限制性者。任何未脱离本发明的精神与范畴,而对其进行之等效修改或变更,均应包含于所附的权利要求书中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1