信号电平转换电路、驱动电路、显示驱动器以及显示装置的制作方法

1.本发明涉及一种信号电平转换电路、包含所述信号电平转换电路的驱动电路、包含所述驱动电路的显示驱动器及显示装置,所述信号电平转换电路将输入信号转换为正极性的高电压信号及负极性的高电压信号。

背景技术:

2.目前,在电视(television,tv)、监视器(monitor)、个人计算机(personal computer,pc)、汽车导航(car navigation)等各种用途的显示装置中,作为显示器件,正采用使用有源矩阵(active matrix)驱动方式的液晶屏的液晶显示装置。这些液晶显示装置逐年推进大画面化或高品质化,高分辨率及高驱动频率的要求高涨。

3.在液晶屏,交叉配置有沿二维画面的垂直方向分别伸长的多个数据线、及沿二维画面的水平方向分别伸长的多个栅极线。进而,在这些多个数据线与多个栅极线的各交叉部,形成有连接于数据线及栅极线的像素部。

4.液晶显示装置中,包含所述液晶屏并且包含数据驱动器,所述数据驱动器将具有与各像素的亮度电平对应的模拟电压值的、灰阶数据信号,以一水平扫描期间单位的数据脉冲(data pulse)供给于数据线。

5.数据驱动器为了防止液晶屏的劣化而进行极性反转驱动,即,将第一极性(正极)的灰阶数据信号与第二极性(负极)的灰阶数据信号在以规定的帧期间为单位交替供给于液晶屏。

6.作为进行此种极性反转驱动的数据驱动器,提出了包括下述驱动电路的数据驱动器,所述驱动电路以0v基准来切换正极的驱动电压及负极的驱动电压并输出(例如参照专利文献1的图8~图10)。专利文献1所记载的驱动电路通过使用此文献的图8所示的开关sw1~开关sw12,从而由从输出焊盘out1输出正极电压信号(5v)的状态(所述文献的图8的状态),切换为从输出焊盘out1输出负极电压信号(-5v)的状态(所述文献的图10的状态)。

7.进而,在进行此种极性切换时,所述驱动电路如所述文献的图9那样,暂且将各开关的一端设定为0v的状态后,切换为所述文献的图10所示的状态。由此,可利用液晶驱动电压范围的约1/2的低耐压元件来构成各开关(晶体管)的通常使用耐压。

8.[现有技术文献]

[0009]

[专利文献]

[0010]

[专利文献1]日本专利特开2008-102211号公报

技术实现要素:

[0011]

[发明所要解决的问题]

[0012]

此处,专利文献1所记载的开关sw1为正极电压信号(0v~5v)通过的开关(例如互补金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)晶体管开关),在正极电压范围内运作。开关sw9为将正极电压信号通过的节点重置为0v的开关(例如n通

道金属氧化物半导体(negative-channel metal oxide semiconductor,nmos)晶体管开关),在正极电压范围内运作。开关sw5在接通时将正极电压信号(0v~5v)输出至输出端子out1,在断开时以在输出端子out1输出的负极电压信号(0v~-5v)不进入正极电压信号输出电路侧的方式阻断。因此,开关sw5包含p通道金属氧化物半导体(positive-channel metal oxide semiconductor,pmos)晶体管开关。此时,pmos晶体管开关sw5使正极电压信号(0v~5v)通过,因而必须将pmos晶体管开关sw5的栅极控制于元件耐压内的负极电压范围(0v~-5v)内。而且,开关sw2为负极电压信号(0v~-5v)通过的开关(例如cmos晶体管开关),在负极电压范围内运作。开关sw10为将负极电压信号通过的节点重置为0v的开关(例如pmos晶体管开关),在负极电压范围内运作。开关sw6在接通时将负极电压信号(0v~-5v)输出至输出端子out1,在断开时以在输出端子out1输出的正极电压信号(0v~5v)不进入负极电压信号输出电路侧的方式进行阻断。因此,开关sw6包含nmos晶体管开关。另外,nmos晶体管开关sw6使负极电压信号(0v~-5v)通过,因而nmos晶体管开关sw6的栅极必须控制于元件耐压内的正极电压范围内(0v~5v)。

[0013]

如以上那样,专利文献1所记载的驱动电路中,在将正极电压信号输出至输出端子out1的情况下,需要利用正极电压范围的控制信号来控制开关sw1及开关sw9,且利用负极电压范围的控制信号来控制开关sw5。而且,在将负极电压信号输出至输出端子out1的情况下,需要利用负极电压范围的控制信号来控制开关sw2及开关sw10,且利用正极电压范围的控制信号来控制开关sw6。

[0014]

进而,所述驱动电路中,在正确进行极性切换时,需要使正极侧的控制信号与负极侧的控制信号的时序同步。

[0015]

但是,正极侧的控制信号在正极侧的耐压范围内(0v~5v)构成电路(正极侧控制电路),负极侧的控制信号在负极侧的耐压范围内(0v~-5v)构成电路(负极侧控制电路),且从低成本化的观点来看,无法使用耐压跨正负两极性的电压范围的元件。而且,在电路结构上,也有时正极侧控制电路的电路延迟与负极侧控制电路的电路延迟不一致。

[0016]

此时,若正极侧的控制信号与负极侧的控制信号的时序未取得同步,则在利用所述驱动电路进行的驱动控制中,有时伴随驱动电路内产生贯通电流而信号噪声或消耗电力增加,或者在极性切换时为了防止元件超过耐压而延长将开关的一端驱动为0v的期间,导致在应对高驱动频率的方面产生限制。

[0017]

因此,本案发明的目的在于提供一种信号电平转换电路、包含所述信号电平转换电路的驱动电路、显示驱动器及显示装置,所述信号电平转换电路可使用元件耐压较输出电压范围更低的开关元件,将低电压的输入电压信号转换第一极性的高电压信号及第二极性的高电压信号,并分别以同步的时序输出。

[0018]

[解决问题的技术手段]

[0019]

本发明的信号电平转换电路对输入电压信号的振幅进行电平移位(level shift),且包括:第一电平移位部,生成将所述输入电压信号的振幅转换为第一电源电压及第二电源电压之间的振幅的、电压信号,所述第一电源电压相对于规定的基准电源电压而呈第一极性,所述第二电源电压相对于所述基准电源电压而呈与所述第一极性为相反极性的第二极性;第二电平移位部,生成将所述电压信号的振幅转换为所述基准电源电压及所述第一电源电压间的振幅的信号,作为第一极性电压信号;第三电平移位部,输出将所述第

一极性电压信号的振幅转换为第三电源电压及所述基准电源电压间的振幅的信号,作为第一极性的高电压信号,所述第三电源电压为第一极性,与所述基准电源电压的电压差大于所述第一电源电压。或者,所述信号电平转换电路还包括:第四电平移位部,生成将由所述第一电平移位部生成的所述电压信号的振幅转换为所述基准电源电压及所述第二电源电压间的振幅的信号,作为第二极性电压信号;以及第五电平移位部,输出将所述第二极性电压信号的振幅转换为第四电源电压及所述基准电源电压间的振幅的信号,作为第二极性的高电压信号,所述第四电源电压为第二极性,与所述基准电源电压的电压差大于所述第二电源电压。

[0020]

而且,本发明的信号电平转换电路对第一输入电压信号及第二输入电压信号的振幅进行电平移位,且包括:第一电平移位部,生成将所述第一输入电压信号的振幅转换为第一电源电压及第二电源电压之间的振幅的、第一电压信号,所述第一电源电压相对于规定的基准电源电压而呈第一极性,所述第二电源电压相对于所述基准电源电压而呈与所述第一极性为相反极性的第二极性;第二电平移位部,生成将所述第一电压信号的振幅转换为所述基准电源电压及所述第一电源电压间的振幅的信号,作为第一极性电压信号;第三电平移位部,输出将所述第一极性电压信号的振幅转换为第三电源电压及所述基准电源电压间的振幅的信号,作为第一极性的高电压信号,所述第三电源电压为第一极性,与所述基准电源电压的电压差大于所述第一电源电压;第四电平移位部,生成将所述第二输入电压信号的振幅转换为所述第一电源电压及所述第二电源电压间的振幅的、第二电压信号;第五电平移位部,生成将所述第二电压信号的振幅转换为所述基准电源电压及所述第二电源电压间的振幅的信号,作为第二极性电压信号;以及第六电平移位部,输出将所述第二极性电压信号的振幅转换为第四电源电压及所述基准电源电压间的振幅的信号,作为第二极性的高电压信号,所述第四电源电压为第二极性,与所述基准电源电压的电压差大于所述第二电源电压。

[0021]

而且,本发明的驱动电路基于低电压的控制信号群来控制驱动时序,在负载驱动时,将相对于规定的基准电源电压而呈第一极性的、高电压的第一极性驱动电压信号从输出端子输出,且所述驱动电路包括:输出部,接收第一极性的高电压输入信号,根据第一极性的高电压控制信号,将放大所述第一极性的高电压输入信号而成的所述第一极性驱动电压信号输出至第一节点;第一导电型的晶体管开关,在接通状态时将所述第一节点的电压供给于所述输出端子,另一方面,在断开状态时阻断所述第一节点与所述输出端子的连接;控制部,根据相对于所述基准电源电压而呈第二极性的高电压控制信号,将对所述第一导电型的晶体管开关进行通断控制的、第二极性的高电压输出控制信号,供给于所述第一导电型的晶体管开关的控制端;以及信号电平转换部,包含第一信号电平转换电路及第二信号电平转换电路,且所述第一信号电平转换电路将所述低电压的控制信号群的第一控制信号的振幅暂且转换为第一极性的第一电源电压及第二极性的第二电源电压间的振幅后,转换为与所述基准电源电压的电压差大于所述第一电源电压的第一极性的第三电源电压及所述基准电源电压间的振幅,将所生成的信号作为所述第一极性的第一高电压控制信号供给于所述第一输出部,所述第二信号电平转换电路将所述低电压的控制信号群的第二控制信号的振幅暂且转换为第一极性的所述第一电源电压及第二极性的所述第二电源电压间的振幅后,转换为与所述基准电源电压的电压差大于所述第二电源电压的第二极性的第四

电源电压及所述基准电源电压间的振幅,将所生成的信号作为所述第二极性的第一高电压控制信号供给于所述第一控制部。

[0022]

而且,本发明的驱动电路基于低电压的控制信号群来控制驱动时序,在负载驱动时,选择相对于规定的基准电源电压而呈第一极性的高电压的第一极性驱动电压信号、及呈第二极性的高电压的第二极性驱动电压信号中的一者,并从输出端子输出,且所述驱动电路包括:第一输出部,接收第一极性的高电压输入信号,根据第一极性的第一高电压控制信号,将放大所述第一极性的高电压输入信号而成的所述第一极性驱动电压信号输出至第一节点;第一导电型的晶体管开关,在接通状态时将所述第一节点的电压供给于所述输出端子,另一方面,在断开状态时阻断所述第一节点与所述输出端子的连接;第一控制部,根据第二极性的第一高电压控制信号,将对所述第一导电型的晶体管开关进行通断控制的、第二极性的高电压输出控制信号,供给于所述第一导电型的晶体管开关的控制端;第二输出部,接收第二极性的高电压输入信号,根据第二极性的第二高电压控制信号,将放大所述第二极性的高电压输入信号而成的所述第二极性驱动电压信号输出至第二节点;第二导电型的晶体管开关,在接通状态时将所述第二节点的电压供给于所述输出端子,另一方面,在断开状态时阻断所述第二节点与所述输出端子的连接;第二控制部,根据第一极性的第二高电压控制信号,将对所述第二导电型的晶体管开关进行通断控制的、第一极性的高电压输出控制信号,供给于所述第二导电型的晶体管开关的控制端;以及信号电平转换部,包含第一信号电平转换电路~第四信号电平转换电路,所述第一信号电平转换电路将所述低电压的控制信号群的第一控制信号的振幅暂且转换为第一极性的第一电源电压及第二极性的第二电源电压间的振幅后,转换为与所述基准电源电压的电压差大于所述第一电源电压的第一极性的第三电源电压及所述基准电源电压间的振幅,将所生成的信号作为所述第一极性的第一高电压控制信号供给于所述第一输出部,所述第二信号电平转换电路将所述低电压的控制信号群的第二控制信号的振幅暂且转换为第一极性的所述第一电源电压及第二极性的所述第二电源电压间的振幅后,转换为与所述基准电源电压的电压差大于所述第二电源电压的第二极性的第四电源电压及所述基准电源电压间的振幅,将所生成的信号作为所述第二极性的第一高电压控制信号供给于所述第一控制部,所述第三信号电平转换电路将所述低电压的控制信号群的第三控制信号的振幅暂且转换为第一极性的所述第一电源电压及第二极性的所述第二电源电压间的振幅后,转换为第二极性的所述第四电源电压及所述基准电源电压间的振幅,将所生成的信号作为所述第二极性的第二高电压控制信号供给于所述第二输出部,所述第四信号电平转换电路将所述低电压的控制信号群的第四控制信号的振幅暂且转换为第一极性的所述第一电源电压及第二极性的所述第二电源电压间的振幅后,转换为第一极性的所述第三电源电压及所述基准电源电压间的振幅,将所生成的信号作为所述第一极性的第二高电压控制信号供给于所述第二控制部。

[0023]

而且,本发明的显示驱动器包括:数据寄存锁存器(data register latch),导入表示基于影像信号的各像素的亮度电平的、像素数据片的系列,将所导入的多个所述像素数据片输出;多个电平移位电路群,将从所述数据寄存锁存器输出的所述多个像素数据片各自的信号电平分别转换为正极性的高电压信号及负极性的高电压信号;解码器部,将每个所述像素数据片的所述正极性的高压信号及负极性的高压信号分别转换为正极性的灰阶电压信号及负极性的灰阶电压信号;以及驱动电路群,基于控制驱动时序的、低电压的控

制信号群,将针对每个输出通道交替选择所述正极性的灰阶电压信号及所述负极性的灰阶电压信号的信号作为驱动电压信号经由输出端子而输出,所述驱动电路群包括:信号电平转换部,被供给有驱动基准电源电压、相对于所述基准电源电压而为正极性的低电压正极电源电压及高电压正极电源电压、及相对于所述基准电源电压而为负极性的低电压负极电源电压及高电压负极电源电压,且对所述低电压的控制信号群的电压振幅进行转换而生成高电压的控制信号群,进而所述驱动电路群全部由元件耐压较所述高电压正极电源电压及所述高电压负极电源电压间的电压差更低的晶体管所构成,所述驱动电路群的各驱动电路为所述本发明的驱动电路。

[0024]

而且,本发明的显示装置包括:所述本发明的显示驱动器;以及液晶显示屏,根据从所述显示驱动器的每个所述输出通道的所述输出端子输出的所述驱动电压信号而受到驱动。

[0025]

[发明的效果]

[0026]

本发明的信号电平转换电路中,首先利用第一电平移位部,将低电压的输入信号的振幅向与所述输入信号的极性为相反的极性侧进行电平移位,由此获得振幅为正极性的低电压至负极性的低电压的范围的、电压信号。接下来,利用第二电平移位部,将此种振幅为正极性的低电压至负极性的低电压的范围的电压信号转换为正极性的低电压信号,利用第三电平移位部将所述正极性的低电压信号的振幅进行电平移位为正极性的高电压信号。而且,利用第四电平移位部,将振幅为正极性的低电压至负极性的低电压的范围的电压信号转换为负极性的低电压信号,利用第五电平移位部将所述负极性的低电压信号的振幅进行电平移位为负极性的高电压信号。

[0027]

根据所述结构,可使包含第一电平移位部、第二电平移位部及第三电平移位部的正极性用的信号电平转换部中的处理时间与包含第一电平移位部、第四电平移位部及第五电平移位部的负极性用的信号电平转换部中的处理时间相等。

[0028]

进而,第一电平移位部~第五电平移位部中,分别可使用耐压较负极性的高电压信号至正极性的高电压信号的输出电压范围更低的、开关元件(晶体管)。

[0029]

因此,根据本发明的信号电平转换电路,可使用元件耐压较输出电压范围更低的开关元件,将低电压的输入电压信号转换为第一极性的高电压信号及第二极性的高电压信号,并分别以同步的时序输出。而且,即便在针对多个低电压的输入电压信号分别利用本发明的信号电平转换电路转换为第一极性的高电压信号或第二极性的高电压信号的情况下,也可在维持多个低电压的输入电压信号间的时序的状况下,转换为第一极性的高电压信号或第二极性的高电压信号。

[0030]

而且,通过在根据低电压的控制信号将正极性的高电压的驱动电压信号及负极性的驱动电压信号交替从一个输出端子输出的驱动电路中,采用所述信号电平转换电路,由低电压的控制信号群转换为驱动时序控制用的高电压的正极性及负极性的控制信号群,从而可实现由元件耐压较输出电压范围更低的晶体管构成的、省面积的驱动电路,且可应对需要高精度的驱动时序控制的、高驱动频率。

附图说明

[0031]

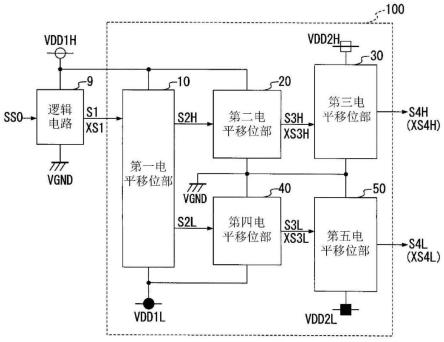

图1为表示作为本发明的第一实施例的信号电平转换电路100的结构的一例的框

图。

[0032]

图2a为表示本发明的第一实施例的信号电平转换电路100的变形例100_h的框图。

[0033]

图2b为表示本发明的第一实施例的信号电平转换电路100的另一变形例100_l的框图。

[0034]

图3为表示作为本发明的第二实施例的信号电平转换电路100_1的结构的电路图。

[0035]

图4为表示作为本发明的第三实施例的驱动电路200_1的结构的框图。

[0036]

图5为表示作为本发明的第四实施例的驱动电路200_2的结构的框图。

[0037]

图6为表示驱动电路200_1或驱动电路200_2的、作为本发明的第五实施例的控制动作的时间图。

[0038]

图7为表示包括包含本发明的信号电平转换电路及驱动电路的数据驱动器的、作为本发明的第六实施例的液晶显示装置400的结构的框图。

[0039]

图8为表示数据驱动器80的结构的框图。

[0040]

[符号的说明]

[0041]

10:第一电平移位部

[0042]

20:第二电平移位部

[0043]

30:第三电平移位部

[0044]

40:第四电平移位部

[0045]

50:第五电平移位部

[0046]

80:数据驱动器

[0047]

100、100_h、100_l、100_1、100a、100b、100c、100d、100e:信号电平转换电路

[0048]

100_2、100_3:信号电平转换部

[0049]

200_1、200_2:驱动电路

[0050]

400:液晶显示装置

具体实施方式

[0051]

[实施例1]

[0052]

图1为表示作为本发明的第一实施例的信号电平转换电路100的结构的一例的框图。

[0053]

信号电平转换电路100例如接收逻辑电路9基于所输入的电压信号ss0而输出的第一极性(正极)的电压信号s1、及使电压信号s1的相位反转的互补信号xs1。此外,下文中由于电压信号ss0及电压信号s1、电压信号xs1分别为逻辑电路用的低电压的信号,因而也称为低电压(low voltage,lv)电压信号ss0及lv电压信号s1、lv电压信号xs1。进而,信号电平转换电路100接收多个电源电压(vdd2l、vdd1l、vgnd、vdd1h、vdd2h)的供给,所述多个电源电压以基准电源电压vgnd为基准,以所述基准电源电压vgnd以上的电压为第一极性(正极),以基准电源电压vgnd以下的电压为第二极性(负极),具有以下的大小关系。在下文中,基准电源电压vgnd将在每个实施例中描述为0v。

[0054]

vdd2l<vdd1l<vgnd<vdd1h<vdd2h

[0055]

(vdd1h-vdd1l)≤vdd2h

[0056]

(vdd1h-vdd1l)≤|vdd2l|

[0057]

此外,下文中将电源电压vdd1h及电源电压vdd1l也称为lv电源电压,关于电源电压vdd2h及电源电压vdd2l,由于为较所述lv电源电压更高的电压,因而也称为高电压(high voltage,hv)电源电压。

[0058]

信号电平转换电路100输入lv电压信号s1及其互补信号xs1,将lv电压信号s1转换为第一极性(正极)的高电压(vdd2h)的电压信号(下文中称为hv电压信号)、及第二极性(负极)的高电压(vdd2l)的hv电压信号。此外,关于构成电平转换电路100的各元件的耐压(通常使用耐压),在将低电压元件设为耐压vdd1m、高电压元件设为耐压vdd2m的情况下,采用满足以下关系的耐压。

[0059]

vdd1m≈vdd1h+δ1

[0060]

vdd1m≈|vdd1l|+δ1

[0061]

vdd2m≈vdd2h+δ2

[0062]

vdd2m≈|vdd2l|+δ2

[0063]

δ1、δ2=电压容限

[0064]

如图1所示,信号电平转换电路100包含第一电平移位部10、第二电平移位部20、第三电平移位部30、第四电平移位部40及第五电平移位部50。

[0065]

第一电平移位部10针对lv电压信号s1、lv电压信号xs1的振幅(vdd1h~vgnd),以基准电源电压vgnd作为基准向第二极性(负极)侧扩展,转换为以此种方式进行电平移位而成的、具有振幅(vdd1l~vdd1h)的电压信号。具体而言,第一电平移位部10将lv电压信号s1、lv电压信号xs1转换为第一极性(正极)用的电压信号s2h(vdd1l、vdd1h)、及第二极性(负极)用的hv电压信号s2l。第一电平移位部10将电压信号s2h供给于第二电平移位部20,并且将电压信号s2l供给于第四电平移位部40。

[0066]

第二电平移位部20针对从第一电平移位部10供给的电压信号s2h的振幅(vdd1l~vdd1h),以基准电源电压vgnd作为基准进行电平移位,转换为具有振幅(vgnd~vdd1h)的、第一极性(正极)的电压信号s3h及其互补信号xs3h,将所述电压信号s3h、电压信号xs3h供给于第三电平移位部30。

[0067]

第三电平移位部30针对电压信号s3h、电压信号xs3h的振幅(vgnd~vdd1h),以基准电源电压vgnd作为基准向第一极性(正极)侧扩展,转换为以此种方式进行电平移位而成的、具有振幅(vgnd~vdd2h)的第一极性(正极)的hv电压信号s4h及其互补信号xs4h,输出hv电压信号s4h、hv电压信号xs4h中的一者或两者。

[0068]

第四电平移位部40针对从第一电平移位部10供给的电压信号s2l的振幅(vdd1l~vdd1h),以基准电源电压vgnd作为基准进行电平移位,转换为具有振幅(vgnd~vdd1l)的、电压信号s3l及其互补信号xs3l,将所述电压信号s3l、电压信号xs3l供给于第五电平移位部50。

[0069]

第五电平移位部50针对电压信号s3l、电压信号xs3l的振幅(vgnd~vdd1l),以将基准电源电压vgnd作为基准向第二极性(负极)侧扩展,转换为以此种方式进行电平移位而成的、具有振幅(vgnd~vdd2l)的第二极性(负极)的hv电压信号s4l及其互补信号xs4l,输出hv电压信号s4l、hv电压信号xs4l中的一者或两者。

[0070]

这样,图1所示的信号电平转换电路100中,通过利用第一电平移位部10将成为信号电平的转换对象的lv电压信号s1、lv电压信号xs1的振幅向负极侧扩展,从而获得具有跨

负极至正极的vdd1h~vdd1l的振幅的、电压信号s2h、电压信号s2l。此时,从第一电平移位部10供给的电压信号s2h、电压信号s2l可彼此为同相信号或互补信号的任一种,将电压信号s2h作为第一极性(正极)用的电压信号而输出,并且将电压信号s2l作为第二极性(负极)用的电压信号而输出。

[0071]

接下来,针对第一极性(正极)用的电压信号s2h,利用第一极性用电平移位部(20、30)转换为将其振幅进行电平移位为vgnd~vdd2h的、第一极性(正极)的hv电压信号s4h(xs4h)。进而,针对第二极性(负极)用的电压信号s2l,利用第二极性用电平移位部(40、50)转换为将其振幅进行电平移位为vgnd~vdd2l的、第二极性(负极)的hv电压信号s4l(xs4l)。

[0072]

重要的是,信号电平转换电路100通过以下的第一电平移位部~第五电平移位部,将低电压的输入电压信号进行电平转换为第一极性的高电压信号及第二极性的高电压信号。即,第一电平移位部(10)生成将输入电压信号(s1、xs1)的振幅转换为负极性的第一负极电源电压(vdd1l)及正极性的第一正极电源电压(vdd1h)间的振幅的、电压信号(s2h、s2l)。第二电平移位部(20)生成将所述电压信号(s2h)的振幅转换为规定的基准电源电压(vgnd)及第一正极电源电压(vdd1h)间的振幅的信号,作为第一极性电压信号(s3h、xs3h)。第三电平移位部(30)输出将第一极性电压信号(s3h、xs3h)的振幅转换为较第一正极电源电压(vdd1h)更高的第二正极电源电压(vdd2h)及基准电压间的振幅的信号,作为第一极性的高电压信号(s4h、xs4h)。第四电平移位部(40)生成将电压信号(s2l)的振幅转换为基准电源电压(vgnd)及第一负极电源电压(vdd1l)间的振幅的信号,作为第二极性电压信号(s3l、xs3l)。第五电平移位部(50)输出将第二极性电压信号(s3l、xs3l)的振幅转换为较第一负极电源电压(vdd1l)更低的第二负极电源电压(vdd2l)及基准电源电压间的振幅的信号,作为第二极性的高电压信号(s4l、xs4l)。这样,信号电平转换电路100在第一电平移位部(10)中,将低电压的输入电压信号暂且转换为跨负极至正极的vdd1l~vdd1h间的振幅的电压信号s2h、电压信号s2l,且包括电平移位部(20、30及40、50),所述电平移位部(20、30及40、50)将电压信号s2h、电压信号s2l相对于基准电源电压vgnd向正极侧与负极侧分别对称地扩展振幅。

[0073]

根据所述结构,信号电平转换电路100可使针对低电压的电压信号(s1、xs1)分别扩展振幅而成的、第一极性的高电压信号(s4h、xs4h)与第二极性的高电压信号(s4l、xs4l)的振幅转换处理时间(时序)一致。进而,针对构成信号电平转换电路100的元件的制造工艺或环境温度等所致的特性变动,也可抑制振幅转换处理时间(时序)的变动。此外,正极侧的电源电压vdd1h及负极侧的电源电压vdd1l优选与基准电源电压vgnd的电压差分别为相同程度。而且,正极侧的电源电压vdd2h及负极侧的电源电压vdd2l也优选与基准电源电压vgnd的电压差分别为相同程度。

[0074]

进而,第一电平移位部10~第五电平移位部50分别可由元件耐压较负极性的高电压信号(s4l)至正极性的高电压信号(s4h)的电源电压范围(vdd2l~vdd2h)更低(例如跨正极至负极的电源电压范围(vdd2l~vdd2h)的约1/2)的晶体管所构成。

[0075]

因此,根据图1所示的信号电平转换电路100,可使用元件耐压较输出电压范围更低的晶体管,将lv电压信号s1进行电平转换为第一极性(正极)的hv电压信号s4h、及第二极性(负极)的hv电压信号s4l,并分别以同步的时序输出。

[0076]

此外,图1中,表示了第一电平移位部10、第三电平移位部30及第五电平移位部50接收彼此互补的两个信号来进行振幅转换的结构例,但也可为仅接收此两个信号中的一者的结构。

[0077]

此外,也可在图1所示的第一极性用电平移位部(20、30)、或第二极性用电平移位部(40、50)中,设置调整两者的输出时序的功能。

[0078]

此外,图1所示的信号电平转换电路100中,以一个lv电压信号s1(xs1)作为信号电平的转换对象,但也可扩展为下述结构,即:以两个或三个以上的多个lv电压信号作为转换对象,分别进行电平转换为第一极性(正极)及第二极性(负极)的hv电压信号。对于针对多个不同的低电压的电压信号分别利用信号电平转换电路100扩展振幅而成的、第一极性及第二极性的高电压信号群,也可抑制制造工艺或环境温度等元件特性变动的影像,使极性间及高电压信号群间的振幅转换处理时间(时序)一致。

[0079]

而且,视需要,第一电平移位部10中也可包含逻辑电路,所述逻辑电路生成用于对第一极性用电平移位部(20、30)及第二极性用电平移位部(40、50)进行同步控制的控制信号。而且,在应对过度的元件特性偏差的情况下,也可将下述功能搭载于信号电平转换电路100,即:通过来自信号电平转换电路100的外部的控制信号,来修正hv电压信号s4h及hv电压信号s4l彼此的时序偏差。

[0080]

而且,将图1的信号电平转换电路100的变形例示于图2a及图2b。图2a为从图1去掉第四电平移位部40及第五电平移位部50的信号电平转换电路100_h。图2a的信号电平转换电路100_h将低电压的电压信号s1、电压信号xs1进行电平转换为第一极性(正极)的高电压信号s4h(xs4h)。而且,图2b为从图1去掉第二进行电平转换及第三电平移位部30的信号电平转换电路100_l。图2b的信号电平转换电路100_l将低电压的电压信号s1、xs1进行电平转换为第二极性(负极)的高电压信号s4l(xs4l)。

[0081]

图2a及图2b的信号电平转换电路100_h、信号电平转换电路100_l可用于将低电压的电压信号的振幅仅向正极侧及负极侧中的一者扩展的情况。在由多个不同的低电压的电压信号群针对各极性生成多个高电压信号群(例如时序控制信号群)的情况下,通过使用信号电平转换电路100、信号电平转换电路100_h、信号电平转换电路100_l来生成多个高电压信号群,从而可在维持多个不同的低电压的电压信号群间的时序的状况下,生成振幅经扩展的高电压信号群。这样生成的第一极性及第二极性的高电压信号群可抑制元件特性变动的影响,使极性间及高电压信号群间的振幅转换处理时间(时序)一致。

[0082]

[实施例2]

[0083]

图3为表示作为本发明的第二实施例的信号电平转换电路100_1的结构的电路图。

[0084]

图3表示图1所示的信号电平转换电路100的第一电平移位部10、第二电平移位部20、第三电平移位部30、第四电平移位部40及第五电平移位部50各自的具体电路例。此外,图3中为了方便起见,表示针对一个lv电压信号ss0生成第一极性(正极)的hv电压信号(s4h、xs4h)、及第二极性(负极)的hv电压信号(s4l、xs4l)的结构。

[0085]

图3中,逻辑电路9包含:逆变器i1,使lv电压信号ss0的逻辑电平反转,作为lv电压信号s1信号而输出。信号电平转换电路100_1的第一电平移位部10接收从逆变器i1输出的lv电压信号s1及其互补信号xs1(=ss0)。此外,图3的逻辑电路9为方便起见而为仅逆变器i1的结构,但可为输出lv电压信号s1、lv电压信号xs1的任意结构。

[0086]

第一电平移位部10包含在各自的源极接收第一极性(正极)的电源电压vdd1h的pmos晶体管q1及pmos晶体管q2、以及在各自的源极接收负极性的电源电压vdd1l的nmos晶体管q3及nmos晶体管q4。

[0087]

pmos晶体管q1的漏极分别连接于nmos晶体管q3的漏极及nmos晶体管q4的栅极。对于pmos晶体管q1的栅极,供给有从逻辑电路9输出的lv电压信号s1。pmos晶体管q2的漏极分别连接于nmos晶体管q4的漏极及nmos晶体管q3的栅极。对于pmos晶体管q2的栅极,供给有lv电压信号xs1。

[0088]

根据所述结构,第一电平移位部10输出在pmos晶体管q2的漏极与nmos晶体管q4的漏极的连接点产生的信号,作为负极用的电压信号s2l。而且,第一电平移位部10输出在pmos晶体管q1的漏极与nmos晶体管q3的漏极的连接点产生的信号、也就是使电压信号s2l的相位反转的互补信号,作为电压信号s2h。此外,电压信号s2l、电压信号s2h也可并非彼此互补的信号。例如,也可将在pmos晶体管q2的漏极与nmos晶体管q4的漏极的连接点产生的信号、或在pmos晶体管q1的漏极与nmos晶体管q3的漏极的连接点产生的信号中的任一者,作为共通的电压信号s2l、电压信号s2h而输出。

[0089]

第二电平移位部20包含串联的逆变器i2及逆变器i3。逆变器i2及逆变器i3接收第一极性(正极)的电源电压vdd1h及基准电源电压vgnd。

[0090]

逆变器i2接收电压信号s2h,在所述电压信号s2h表示第一极性(正极)的电源电压vdd1h的情况下,输出表示基准电源电压vgnd的信号。另一方面,在所述电压信号s2h表示第二极性(负极)的电源电压vdd1l的情况下,逆变器i2输出表示第一极性(正极)的电源电压vdd1h的信号。逆变器i2将如上文所述那样输出的信号作为电压信号s3h供给于逆变器i3及第三电平移位部30。逆变器i3将使电压信号s3h的相位反转的互补信号作为电压信号xs3h供给于第三电平移位部30。

[0091]

第四电平移位部40包含串联的逆变器i4及逆变器i5。逆变器i4及逆变器i5接收基准电源电压vgnd及第二极性(负极)的电源电压vdd1l。

[0092]

逆变器i4接收电压信号s2l,在所述电压信号s2l表示第一极性(正极)的电源电压vdd1h的情况下,输出表示第二极性(负极)的电源电压vdd1l的信号。而且,逆变器i4在电压信号s2l表示第二极性(负极)的电源电压vdd1l的情况下,输出表示基准电源电压vgnd的信号。逆变器i4将如上文所述那样输出的信号作为电压信号xs3l供给于逆变器i5及第五电平移位部50。逆变器i5将使电压信号xs3l的相位反转的互补信号作为电压信号s3l供给于第五电平移位部50。

[0093]

第三电平移位部30包含在各自的源极接收第一极性(正极)的电源电压vdd2h的pmos晶体管q5及pmos晶体管q6、以及在各自的源极接收基准电源电压vgnd的nmos晶体管q7及nmos晶体管q8。

[0094]

pmos晶体管q5的漏极分别连接于pmos晶体管q6的栅极及nmos晶体管q7的漏极。pmos晶体管q6的漏极分别连接于pmos晶体管q5的栅极及nmos晶体管q8的漏极。对于nmos晶体管q7的栅极,供给有从第二电平移位部20输出的电压信号xs3h。对于nmos晶体管q8的栅极,供给有从第二电平移位部20输出的电压信号s3h。

[0095]

根据所述结构,第三电平移位部30输出在pmos晶体管q6的漏极与nmos晶体管q8的漏极的连接点产生的信号,作为第一极性(正极)的hv电压信号s4h。而且,第三电平移位部

30输出在pmos晶体管q5的漏极与nmos晶体管q7的漏极的连接点产生的信号,作为使hv电压信号s4h的相位反转的、第一极性(正极)的hv电压信号xs4h。

[0096]

第五电平移位部50包含在各自的源极接收基准电源电压vgnd的pmos晶体管q9及pmos晶体管q10、以及在各自的源极接收第二极性(负极)的电源电压vdd2l的nmos晶体管q11及nmos晶体管q12。

[0097]

pmos晶体管q9的漏极分别连接于nmos晶体管q12的栅极及nmos晶体管q11的漏极。pmos晶体管q10的漏极分别连接于nmos晶体管q11的栅极及nmos晶体管q12的漏极。对于nmos晶体管q9的栅极,供给有从第四电平移位部40输出的电压信号s3l。对于nmos晶体管q10的栅极,供给有从第四电平移位部40输出的电压信号xs3l。

[0098]

根据所述结构,第五电平移位部50输出在pmos晶体管q10的漏极与nmos晶体管q12的漏极的连接点产生的信号,作为第二极性(负极)的hv电压信号s4l。而且,第五电平移位部50输出在pmos晶体管q9的漏极与nmos晶体管q11的漏极的连接点产生的信号,作为使hv电压信号s4l的相位反转的、第二极性(负极)的hv电压信号xs4l。

[0099]

根据所述结构,可抑制构成各电平移位部的nmos晶体管及pmos晶体管的特性偏差或温度条件的变动等所致的、极性间的hv电压信号的时序偏差。因此,可将lv电压信号s1、lv电压信号xs1转换为第一极性(正极)的hv电压信号(s4h、xs4h)、及第二极性(负极)的hv电压信号(s4l、xs4l),并分别以同步的时序输出。

[0100]

此外,图3所示的信号电平转换电路100_1中,分别利用四元件的mos晶体管来构成作为将所输入的lv电压信号(s1、xs1)的电压振幅放大的电平移位部的第一电平移位部10、第三电平移位部30及第五电平移位部50,但也可采用其他结构。

[0101]

而且,第二电平移位部20及第四电平移位部40优选相对于基准电源电压vgnd而为对称结构,第三电平移位部30及第五电平移位部50也优选相对于基准电源电压vgnd而为对称结构。具体而言,如图3的结构例那样,第四电平移位部40优选设为下述结构,即:将供给于第二电平移位部20的第一极性(正极)的电源电压vdd1h更换为第二极性(负极)的电源电压vdd1l,并且更换构成第二电平移位部20的晶体管的导电型。同样地,第五电平移位部50也优选设为下述结构,即:将供给于第三电平移位部30的第一极性(正极)的电源电压vdd2h更换为第二极性(负极)的电源电压vdd2l,并且更换构成第四电平移位部40的晶体管的导电型。

[0102]

根据所述结构,可抑制电压振幅的转换时的、极性间的hv电压信号的时序偏差。因此,可将lv电压信号s1、lv电压信号xs1转换为第一极性(正极)的hv电压信号(s4h、xs4h)、及第二极性(负极)的hv电压信号(s4l、xs4l),并分别以同步的时序输出。

[0103]

[实施例3]

[0104]

图4为表示作为本发明的第三实施例的驱动电路200_1的结构的框图。

[0105]

此外,驱动电路200_1接收具有正极性的高电压值(vgnd~vdd2h)的正极高电压输入信号vp、及具有负极性的高电压值(vdd2l~vgnd)的负极高电压输入信号vn,作为用于驱动负载的高电压输入信号。而且,驱动电路200_1在被供给有表示极性切换时序的极性切换信号pol、及控制输出时序的多个低电压的控制信号ss的逻辑电路9中,生成驱动电路200_1的驱动控制所需要的lv电压信号群(vgnd~vdd1h)的sa1、sb1、sc1、sd1及各自的互补信号xsa1、互补信号xsb1、互补信号xsc1、互补信号xsd1,在与所述lv电压信号群相应的时序,将

分别放大所述正极高电压输入信号vp及负极高电压输入信号vn而成的高电压的正极驱动电压信号vpa及负极驱动电压信号vna交替切换,并从输出端子dl1输出。而且,驱动电路200_1由元件耐压较在输出端子dl1输出的正极驱动电压信号vpa及负极驱动电压信号vna的输出电压范围(vdd2l~vdd2h)更低的晶体管所构成。

[0106]

如图4所示,驱动电路200_1包含pmos输出开关11及nmos输出开关21、信号电平转换部100_2、正极信号输出部111、负极信号输出部121、正极输出sw控制部112及负极输出sw控制部122。

[0107]

信号电平转换部100_2根据控制信号的种类而包括多系统的图1(图3)、图2a及图2b所示的信号电平转换电路(图4中为100a、100b、100c、100d)。对于信号电平转换部100_2,供给有基准电源电压vgnd、正极性的电源电压vdd1h及负极性的电源电压vdd1l,还供给有相对于基准电源电压vgnd的电压差大于电源电压vdd1h的正极性的电源电压vdd2h、及同样地相对于基准电源电压vgnd的电压差大于电源电压vdd1l的负极性的电源电压vdd2l。

[0108]

信号电平转换电路100a如上文所述,对用于控制时序的lv电压信号sa1、lv电压信号xsa1的振幅进行电平移位。即,信号电平转换电路100a将lv电压信号sa1及lv电压信号xsa1的振幅暂且转换为正极性的电源电压vdd1h及负极性的电源电压vdd1l间的振幅后,转换为正极性的电源电压vdd2h及基准电源电压vgnd间的振幅,将所生成的信号作为正极性的hv电压信号sa4h及hv电压信号xsa4h供给于正极信号输出部111。信号电平转换电路100b将用于控制时序的lv电压信号sb1及lv电压信号xsb1的振幅暂且转换为正极性的电源电压vdd1h及负极性的电源电压vdd1l间的振幅后,转换为负极性的电源电压vdd2l及基准电源电压vgnd间的振幅,将所生成的信号作为负极性的hv电压信号sb4l及hv电压信号xsb4l供给于正极输出sw控制部112。而且,信号电平转换电路100c将用于控制时序的lv电压信号sc1及lv电压信号xsc1的振幅暂且转换为正极性的电源电压vdd1h及负极性的电源电压vdd1l间的振幅后,转换为负极性的电源电压vdd2l及基准电源电压vgnd间的振幅,将所生成的信号作为负极性的hv电压信号sc4l及hv电压信号xsc4l供给于负极信号输出部121。进而,信号电平转换电路100d将用于控制时序的lv电压信号sd1及lv电压信号xsd1的振幅暂且转换为正极性的电源电压vdd1h及负极性的电源电压vdd1l间的振幅后,转换为正极性的电源电压vdd2h及基准电源电压vgnd间的振幅,将所生成的信号供给于负极输出sw控制部122。

[0109]

此外,图4的信号电平转换部100_2中,信号电平转换电路100a~信号电平转换电路100d分别为将lv电压信号转换为正极性或负极性的hv电压信号的信号电平转换电路,例如信号电平转换电路100a及信号电平转换电路100d可适用图2a的结构100_h,信号电平转换电路100b及信号电平转换电路100c可适用图2b的结构100_l。

[0110]

正极信号输出部111接收第一极性(正极)的hv电源电压vdd2h及基准电源电压vgnd,在正极性的hv电压范围内(vgnd~vdd2h)运作。正极信号输出部111根据第一极性(正极)的hv电压信号sa4h、hv电压信号xsa4h中的一者或两者的控制时序,将放大正极高电压输入信号vp而成的正极驱动电压信号vpa经由节点ns11供给于作为pmos晶体管的pmos输出开关11的源极。

[0111]

正极输出sw控制部112接收第二极性(负极)的hv电源电压vdd2l及基准电源电压vgnd,在负极性的hv电压范围内(vdd2l~vgnd)运作。正极输出sw控制部112根据第二极性

(负极)的hv电压信号sb4l、hv电压信号xsb4l中的一者或两者的控制时序,生成可针对正极驱动电压信号vpa在规定的元件耐压内对pmos输出开关11控制通断的、至少二值(例如vgnd及vdd1l)的负极性的高电压输出控制信号gp,并将其供给于pmos输出开关11的栅极。

[0112]

pmos输出开关11为pmos晶体管,自身的漏极连接于输出端子dl1。pmos输出开关11根据对自身的源极供给的正极驱动电压信号vpa、及在自身的栅极接收的负极性的高电压输出控制信号gp,设定为接通状态或断开状态。pmos输出开关11在接通状态时,向输出端子dl1输出从正极信号输出部111供给的正极驱动电压信号vpa。此外,pmos输出开关11的漏极、栅极、源极(及背栅)控制于元件耐压以下的电压差内。

[0113]

负极信号输出部121接收第二极性(负极)的hv电源电压vdd2l及基准电源电压vgnd,在负极性的hv电压范围内(vdd2l~vgnd)运作。负极信号输出部121根据第二极性(负极)的hv电压信号sc4l、hv电压信号xsc4l中的一者或两者的控制时序,将放大负极高电压输入信号vn而成的负极驱动电压信号vna经由节点ns21供给于nmos输出开关21的源极。

[0114]

负极输出sw控制部122接收第一极性(正极)的hv电源电压vdd2h及基准电源电压vgnd,在正极性的hv电压范围内(vgnd~vdd2h)运作。负极输出sw控制部122根据第一极性(正极)的hv电压信号sd4h、hv电压信号xsd4h中的一者或两者的控制时序,生成可针对负极驱动电压信号vpa在规定的元件耐压内对nmos输出开关21控制通断的、至少二值(例如vgnd及vdd1h)的正极性的高电压输出控制信号gn,并将其供给于nmos输出开关21的栅极。

[0115]

nmos输出开关21为nmos晶体管,自身的漏极连接于输出端子dl1。nmos输出开关21根据对自身的源极供给的负极驱动电压信号vna、及在自身的栅极接收的正极性的高电压输出控制信号gn,设定为接通状态或断开状态。nmos输出开关21在接通状态时,向输出端子dl1输出从负极信号输出部121供给的负极驱动电压信号vna。此外,nmos输出开关21的漏极、栅极、源极(及背栅)控制于元件耐压以下的电压差内。

[0116]

根据所述结构,驱动电路200_1中,通过来自信号电平转换电路100_2的hv电压信号群(sa1、sb1、sc1、sd1及各自的互补信号xsa1、互补信号xsb1、互补信号xsc1、互补信号xsd1),来控制正极信号输出部111、负极信号输出部121、正极输出sw控制部112及负极输出sw控制部122进行的向输出端子dl1的驱动电压信号的极性切换。此处,信号电平转换电路100_2可将负责正极侧的输出控制的hv电压信号群(sa4h、sb4h及各自的互补信号)彼此、负责负极侧的输出控制的hv电压信号群(sc4h、sd4h及各自的互补信号)彼此、以及正极及负极间的hv电压信号群彼此以同步的时序输出。

[0117]

因此,根据驱动电路200_1,可也包含信号电平转换电路100_2而在使用元件耐压较输出电压范围(vdd2l~vdd2h)更低的晶体管所构成的驱动电路中,抑制同一极性内及极性间的驱动时序偏差,通过高精度的驱动时序控制,对连接于输出端子dl1的容性负载交替切换负极驱动电压信号vna及正极驱动电压信号vpa并输出。由此,可抑制因驱动时序偏差而产生贯通电流或信号噪声,可应对高驱动频率。

[0118]

以下,对进行pmos输出开关11的通断控制的正极输出sw控制部112、及进行nmos输出开关21的通断控制的负极输出sw控制部122的详细动作进行说明。

[0119]

在pmos输出开关11将具有相对较接近电源电压vdd2h的电压值的正极驱动电压信号vpa输出至输出端子dl1的情况下,正极输出sw控制部112将具有基准电源电压vgnd的负极性的高电压输出控制信号gp供给于pmos输出开关11的栅极。而且,在pmos输出开关11将

具有相对较接近基准电源电压vgnd的电压值的正极驱动电压信号vpa输出至输出端子dl1的情况下,正极输出sw控制部112将具有基准电源电压vgnd与负极性的hv电源电压vdd2l的中间电压的、负极性的高电压输出控制信号gp,供给于pmos输出开关11的栅极。即,正极输出sw控制部112为了控制为pmos输出开关11可在较输出电压范围(vdd2l~vdd2h)更低的元件耐压内进行接通动作的栅极电压,而根据输出至输出端子dl1的正极驱动电压信号vpa的电压值,使用至少二值的电压来切换负极性的高电压输出控制信号gp的电压值。同样地,负极输出sw控制部122为了控制为nmos输出开关21可在较输出电压范围更低的元件耐压内进行接通动作的栅极电压,而根据输出至输出端子dl1的负极驱动电压信号vna的电压值,使用至少二值的电压来切换正极性的高电压输出控制信号gn的电压值。

[0120]

此外,驱动电路200_1的结构不限定于图4所示的结构。

[0121]

重要的是,作为驱动电路200_1,只要具有以下的第一输出部及第二输出部、第一导电型的晶体管开关、第二导电型的晶体管开关、第一控制部及第二控制部、以及包含第一信号电平转换电路~第四信号电平转换电路的信号电平转换部即可。

[0122]

即,第一输出部(111)接收第一极性(正极)的高电压输入信号(vp),根据第一极性的第一高电压控制信号(sa4h、xsa4h),将放大所述第一极性的高电压输入信号而成的第一极性的驱动电压信号(vpa)输出至第一节点(ns11)。第一导电型的晶体管开关(11)在接通状态时,将第一节点的电压供给于输出端子(dl1),另一方面,在断开状态时阻断第一节点与输出端子(dl1)的连接。第一控制部(112)根据第二极性的第一高电压控制信号(sb4l、xsb4l),将对第一导电型的晶体管开关进行通断控制的、第二极性的高电压输出控制信号(gp),供给于所述第一导电型的晶体管开关的控制端(栅极)。第二输出部(121)接收第二极性的高电压输入信号(vn),根据第二极性的第二高电压控制信号(sc4l、xsc4l),将放大所述第二极性的高电压输入信号而成的第二极性的驱动电压信号(vna)输出至第二节点(ns21)。第二导电型的晶体管开关(21)在接通状态时,将第二节点的电压供给于输出端子(dl1),另一方面,在断开状态时阻断第二节点与输出端子的连接。第二控制部(122)根据第一极性的第二高电压控制信号(sd4h、xsd4h),将对第二导电型的晶体管开关(21)进行通断控制的、第一极性的高电压输出控制信号(gn),供给于第二导电型的晶体管开关的控制端(栅极)。

[0123]

第一信号电平转换电路(100a)将低电压的控制信号群(sa1、sb1、sc1、sd1及各自的互补信号)的第一控制信号(sa1、xsa1)的振幅暂且转换为第一极性(正极)的第一电源电压(vdd1h)及第二极性(负极)的第二电源电压(vdd1l)间的振幅后,转换为与基准电源电压(vgnd)的电压差较第一电源电压更大的第一极性的第三电源电压(vdd2h)及基准电源电压间的振幅,将所生成的信号作为第一极性的第一高电压控制信号(sa4h、xsa4h)供给于第一输出部(111)。第二信号电平转换电路(100b)将低电压的控制信号群的第二控制信号(sb1、xsb1)的振幅暂且转换为第一极性的第一电源电压及第二极性的第二电源电压间的振幅后,转换为与基准电源电压的电压差大于第二电源电压的第二极性的第四电源电压(vdd2l)及基准电源电压间的振幅,将所生成的信号作为第二极性的第一高电压控制信号(sb4l、xsb4l)供给于第一控制部(112)。第三信号电平转换电路(100c)将低电压的控制信号群的第三控制信号(sc1、xsc1)的振幅暂且转换为第一极性的第一电源电压及第二极性的第二电源电压间的振幅后,转换为第二极性的第四电源电压及基准电源电压间的振幅,

将所生成的信号作为第二极性的第二高电压控制信号(sc4l、xsc4l)供给于第二输出部(121)。第四信号电平转换电路(100d)将低电压的控制信号群的第四控制信号(sd1、xsd1)的振幅暂且转换为第一极性的第一电源电压及第二极性的第二电源电压间的振幅后,转换为第一极性的第三电源电压及基准电源电压间的振幅,将所生成的信号作为第一极性的第二高电压控制信号(sd4h、xsd4h)供给于所述第二控制部。

[0124]

[实施例4]

[0125]

图5为表示作为本发明的第四实施例的驱动电路200_2的结构的框图。此外,图5所示的驱动电路200_2中,表示图4所示的驱动电路200_1的正极信号输出部111、负极信号输出部121、正极输出sw控制部112及负极输出sw控制部122的内部电路的结构例。而且,图5中,将图4的lv电压信号sb1及lv电压信号sd1设为共通的lv电压信号se1,图5的信号电平转换部100_3包含信号电平转换电路100e代替图4的信号电平转换电路100b、信号电平转换电路100d,所述信号电平转换电路100e接收lv电压信号se1、lv电压信号xse1,转换为正极性的hv电压信号se4h、hv电压信号xse4h及负极性的hv电压信号se4l、hv电压信号xse4l。信号电平转换电路100e例如可适用图1的结构。信号电平转换电路100a、信号电平转换电路100c、pmos输出开关11及nmos输出开关21与图4相同。

[0126]

如图5所示,正极信号输出部111包含放大器131、开关132及开关133。放大器131为将自身的反转输入端子及输出节点连接的、电压跟随器(voltage follower)的操作放大器,从输出节点输出将在自身的非反转输入端子接收的正极高电压输入信号vp放大而成的正极驱动电压信号vpa。开关132例如由cmos开关构成,根据从信号电平转换部100_3的信号电平转换电路100a供给的hv电压信号sa4h、hv电压信号xsa4h而设定为接通状态或断开状态。开关132在设定为接通状态的情况下,将放大器131的输出节点经由节点ns11而与pmos输出开关11的源极连接,另一方面,在设定为断开状态的情况下,将放大器131的输出节点及pmos输出开关11的源极间的连接阻断。开关133例如由nmos开关构成,根据从所述信号电平转换电路100a供给的hv电压信号xsa4h而设定为接通状态或断开状态。开关133在设定为接通状态的情况下,对pmos输出开关11的源极施加基准电源电压vgnd。

[0127]

正极输出sw控制部112包含切换开关(下文中记作切换开关112),此切换开关通过基准电源电压vgnd或负极性的控制电压vgp的切换来生成负极性的高电压输出控制信号gp。切换开关112例如设为逆变器结构,根据从信号电平转换部100_3的信号电平转换电路100e供给的hv电压信号se4l(xse4l),切换基准电源电压vgnd或负极性的控制电压vgn,并将通过切换所生成的负极性的高电压输出控制信号gp供给于pmos输出开关11的栅极。此外,负极性的控制电压vgn也可设为下述控制电压,即:根据正极驱动电压信号vpa,而供给有pmos输出开关11可在规定的元件耐压内进行通断控制的、包含vgnd的多个电压值。

[0128]

图5所示的负极信号输出部121包含放大器141、开关142及开关143。放大器141为将自身的反转输入端子及输出节点连接的、电压跟随器的操作放大器,从输出节点输出将在自身的非反转输入端子接收的负极高电压输入信号vn放大而成的负极驱动电压信号vna。开关142根据从信号电平转换部100_3的信号电平转换电路100c供给的hv电压信号sc4l、hv电压信号xsc4l,而设定为接通状态或断开状态。开关142例如由cmos开关构成,在设定为接通状态的情况下,将放大器141的输出节点经由节点ns21而与nmos输出开关21的源极连接,另一方面,在设定为断开状态的情况下,将放大器141的输出节点及nmos输出开

关21的源极间的连接阻断。开关143例如由pmos开关构成,根据从所述信号电平转换电路100c供给的hv电压信号xs4l而设定为接通状态或断开状态。开关143在设定为接通状态的情况下,对nmos输出开关21的源极施加基准电源电压vgnd。

[0129]

负极输出sw控制部122包含切换开关(下文中记作切换开关122),此切换开关通过基准电源电压vgnd或正极性的控制电压vgp的切换来生成正极性的高电压输出控制信号gn。切换开关122例如设为逆变器结构,根据从信号电平转换部100_3的信号电平转换电路100e供给的hv电压信号se4h(xse4h),切换基准电源电压vgnd或正极性的控制电压vgp,并将通过切换所生成的正极性的高电压输出控制信号gn供给于nmos输出开关21的栅极。此外,正极性的控制电压vgp也可设为下述控制电压,即:根据负极驱动电压信号vna,而供给有nmos输出开关21可在规定的元件耐压内进行通断控制的、包含vgnd的多个电压值。

[0130]

此外,图5所示的正极信号输出部111中,开关132也可设于放大器131的内部。而且,负极信号输出部112中,开关142也可设于放大器141的内部。

[0131]

[实施例5]

[0132]

图6为表示驱动电路200_1或驱动电路200_2的、作为本发明的第五实施例的控制动作的时间图。

[0133]

此外,图6中,表示图5所示的驱动电路200_2在规定的正极驱动期间及负极驱动期间中,交替输出正极驱动电压信号vpa及负极驱动电压信号vna(进行极性反转驱动)的情况下,信号电平转换部100_3、正极输出sw控制部112及负极输出sw控制部122生成的各信号(sa4h、xsa4h、sc4l、xsc4l、se4h、se4l、gp、gn)的一例。此外,cmos开关的控制信号仅表示供给于nmos开关的栅极的控制信号。

[0134]

进而,图6中,表示图5所示的pmos输出开关11的源极所连接的节点ns11的电压v11、nmos输出开关21的源极所连接的节点ns21的电压v21、及输出端子dl1的电压的变化。此外,正极驱动电压信号vpa及负极驱动电压信号vna也可为在与各极性对应的电压范围内具有单一或多个电压电平的阶跃信号或正弦波等模拟信号。

[0135]

如图6所示,驱动期间至少分为四个期间t1~t4,在正极驱动期间t2与负极驱动期间t4之间设有切换期间t1、切换期间t3。图6中,表示从前一个负极驱动期间(未图示)后的切换期间(t1)开始的时间图。

[0136]

图6中,首先在切换期间t1中,根据hv电压信号sa4h及hv电压信号sc4l而开关132及开关142均成为断开状态,来自正极信号输出部111及负极信号输出部121的驱动电压信号的供给被阻断。而且,开关133根据具有电源电压vdd2h的hv电压信号xsa4h而成为接通状态,节点ns11的电压v11成为基准电源电压vgnd。而且,对于开关143,供给有具有第二极性(负极)的电源电压vdd2l的hv电压信号sc4l,因而开关143成为接通状态,如图6所示,节点ns21的电压v21从近前的负极驱动期间的负极驱动电压信号vna向基准电源电压vgnd提升。而且,切换开关112根据具有电源电压vdd2l的hv电压信号se4l,将负极性的高电压输出控制信号gp设为基准电源电压vgnd。其结果为,对于pmos输出开关11的栅极,供给有具有基准电源电压vgnd的负极性的高电压输出控制信号gp,pmos输出开关11成为断开状态。而且,切换开关122根据具有基准电源电压vgnd的hv电压信号se4h,将正极性的高电压输出控制信号gn设为正极的控制电压vgp。其结果为,对于nmos输出开关21的栅极,供给有具有控制电压vgp的正极性的高电压输出控制信号gn,nmos输出开关21成为接通状态。

[0137]

因此,期间t1中,作为节点ns21的电压v21的基准电源电压vgnd经由nmos输出开关21施加于输出端子dl1。

[0138]

此时,如图6所示,为负极驱动电压信号vna的状态的、输出端子dl1的电压经由nmos输出开关21而向基准电源电压vgnd提升。

[0139]

此外,在整个期间t1中,开关133及切换开关122的各端子控制于基准电源电压vgnd与第一极性(正极)的电源电压vdd2h之间。pmos输出开关11、开关143及切换开关112的各端子控制于基准电源电压vgnd与第二极性(负极)的电源电压vdd2l之间。nmos输出开关21的漏极及源极控制于基准电源电压vgnd与第二极性(负极)的电源电压vdd2l之间。对于nmos输出开关21的栅极,供给有相对于负极驱动电压信号vna的状态的漏极及源极而nmos输出开关21成为接通状态的、规定的电压差(耐压)内的控制电压vgp,由于供给于节点ns21的基准电源电压vgnd,nmos输出开关21的各端子间的电压差缩小。因此,pmos输出开关11、nmos输出开关21、开关133、开关143、切换开关112及切换开关122控制于较输出端子dl1的输出电压范围(vdd2l~vdd2h)更低的、规定的元件耐压的范围内。

[0140]

接下来,期间t2中,对开关133供给有具有基准电源电压vgnd的hv电压信号xsa4h,因而开关133成为断开状态。而且,对开关143继续供给有具有电源电压vdd2l的hv电压信号sc4l,因而开关143维持接通状态,节点ns21的电压v21成为基准电源电压vgnd。而且,根据hv电压信号sa4h及hv电压信号sc4l,开关132及开关142中仅开关132切换为接通状态。由此,正极信号输出部111生成的正极驱动电压信号vpa供给于节点ns11。而且,切换开关112根据具有基准电源电压vgnd的hv电压信号se4l,将负极性的高电压输出控制信号gp切换为负极性的控制电压vgn。其结果为,pmos输出开关11成为接通状态。而且,切换开关122根据具有电源电压vdd2h的hv电压信号se4h,将正极性的高电压输出控制信号gn切换为基准电源电压vgnd。其结果为,nmos输出开关21切换为断开状态。

[0141]

因此,期间t2中,从正极信号输出部111输出的正极驱动电压信号vpa经由节点ns11及pmos输出开关11向输出端子dl1输出。

[0142]

此时,nmos输出开关21处于断开状态,并且节点ns21与输出端子dl1的电连接被阻断。因此,如图6所示,节点ns11的电压v11及输出端子dl1的电压从基准电源电压vgnd的状态提升至正极驱动电压信号vpa。另一方面,节点ns21的电压v21如图6所示,维持基准电源电压vgnd的状态。

[0143]

此外,在整个期间t2中,开关133、切换开关122及nmos输出开关21的各端子控制于基准电源电压vgnd与第一极性(正极)的电源电压vdd2h之间。开关143及切换开关112的各端子控制于基准电源电压vgnd与第二极性(负极)的电源电压vdd2l之间。pmos输出开关11的各端子中的漏极及源极控制于基准电源电压vgnd与电源电压vdd2h之间的正极驱动电压信号vpa。对于pmos输出开关11的栅极,施加有针对正极驱动电压信号vpa而pmos输出开关11成为接通状态的、规定的电压差(耐压)内的负极性的控制电压vgn。因此,pmos输出开关11、nmos输出开关21、开关133、开关143、切换开关112及切换开关122控制于较输出端子dl1的输出电压范围(vdd2l~vdd2h)更低的、规定的元件耐压的范围内。

[0144]

接下来,期间t3中,根据hv电压信号s4h及hv电压信号s4l而开关132及开关142均成为断开状态,来自正极信号输出部111及负极信号输出部121的驱动电压信号的供给被阻断。而且,对于开关133,供给有具有电源电压vdd2h的hv电压信号xs4h,因而开关133成为接

通状态,如图6所示,节点ns11的电压v11从正极驱动电压信号vpa向基准电源电压vgnd下降。而且,对开关143继续供给有具有电源电压vdd2l的hv电压信号xs4l,因而维持接通状态,节点ns21的电压v21继续成为基准电源电压vgnd。而且,对pmos输出开关11的栅极持续供给有具有控制电压vgn的负极性的高电压输出控制信号gp,因而如图6所示,pmos输出开关11维持接通状态。而且,根据hv电压信号se4h,将正极性的高电压输出控制信号gn维持于基准电源电压vgnd。其结果为,如图6所示,nmos输出开关21维持断开状态。

[0145]

因此,期间t3中,如图6所示,作为节点ns11的电压v11的基准电源电压vgnd经由pmos输出开关11向输出端子dl1输出。

[0146]

此时,如图6所示,为正极驱动电压信号vpa的、输出端子dl1的电压经由pmos输出开关11向基准电源电压vgnd下降。

[0147]

此外,在整个期间t3中,虽然开关133从断开状态变化为接通状态,但各开关的控制电压范围未变化。因此,与期间t2同样地,pmos输出开关11、nmos输出开关21、开关133、开关143、切换开关112及切换开关122控制于较输出端子dl1的输出电压范围(vdd2l~vdd2h)更低的、规定的元件耐压的范围内。

[0148]

接下来,期间t4中,对开关133继续供给有具有第一极性(正极)的电源电压vdd2h的hv电压信号xsa4h,因而开关133成为接通状态,节点ns11的电压v11继续成为基准电源电压vgnd。而且,对开关143供给有具有基准电源电压vgnd的hv电压信号sc4l,因而开关143成为断开状态。而且,根据hv电压信号sa4h及hv电压信号sc4l,开关132及开关142中仅开关142切换为接通状态。由此,从负极信号输出部121输出的负极驱动电压信号vna供给于节点ns21。而且,切换开关112根据具有电源电压vdd2l的hv电压信号se4l,将负极性的高电压输出控制信号gp切换为基准电源电压vgnd。其结果为,pmos输出开关11成为断开状态。而且,切换开关122根据具有基准电源电压vgnd的hv电压信号se4h,将正极性的高电压输出控制信号gn切换为正极性的控制电压vgp。其结果为,nmos输出开关21切换为接通状态。

[0149]

因此,期间t4中,从负极信号输出部121输出的负极驱动电压信号vna经由节点ns21及nmos输出开关21向输出端子dl1输出。

[0150]

此时,如图6所示,pmos输出开关11处于断开状态,并且节点ns11与输出端子dl1的电连接被阻断。因此,如图6所示,节点ns21的电压v21及输出端子dl1的电压从基准电源电压vgnd的状态下降至负极驱动电压信号vna。另一方面,节点ns11的电压v11如图6所示,维持基准电源电压vgnd的状态。

[0151]

此外,在整个期间t4中,开关143、切换开关112及pmos输出开关11的各端子控制于基准电源电压vgnd与第二极性(负极)的电源电压vdd2l之间。开关133及切换开关122的各端子控制于基准电源电压vgnd与第一极性(正极)的电源电压vdd2h之间。nmos输出开关21的各端子中的漏极及源极控制于基准电源电压vgnd与电源电压vdd2l之间的负极驱动电压信号vna。对于nmos输出开关21的栅极,施加有针对负极驱动电压信号vna而nmos输出开关21成为接通状态的、规定的电压差(耐压)内的正极性的控制电压vgp。因此,pmos输出开关11、nmos输出开关21、开关133、开关143、切换开关112及切换开关122控制于较输出端子dl1的输出电压范围(vdd2l~vdd2h)更低的、规定的元件耐压的范围内。

[0152]

此外,图6的驱动控制中,图5的驱动电路200_2向输出端子dl1以规定的周期切换输出正极性的驱动电压信号vpa或负极性的驱动电压信号vna。因此,例如包括多个图5的驱

动电路200_2的驱动电路中,以相同时序输出不同极性的驱动电压信号的驱动电路200_2彼此也可共享一部分电路。具体而言,也可使以相同时序输出不同极性的驱动电压信号的、两个驱动电路200_2彼此,共享正极信号输出部111的放大器131及负极信号输出部121的放大器141。

[0153]

[实施例6]

[0154]

图7为表示包括包含本发明的信号电平转换部及驱动电路的数据驱动器的、作为本发明的第六实施例的液晶显示装置400的结构的框图。

[0155]

图7中,显示屏20为有源矩阵型的液晶显示屏,形成有沿二维画面的水平方向伸长的m个(m为2以上的自然数)水平扫描线s1~sm、及沿二维画面的垂直方向伸长的n个(n为2以上的自然数)数据线d1~dn。在水平扫描线及数据线的各交叉部,形成有负责像素的显示单元。显示单元至少含有开关元件及像素电极,在根据水平扫描线的扫描脉冲而开关元件成为接通状态时,数据线的灰阶电压信号经由开关元件施加于像素电极,根据施加于像素电极的灰阶电压来控制液晶显示器件的亮度。此外,图7中省略具体的显示单元的结构的记载。

[0156]

显示控制部65接收使控制信号等一体化的影像信号vd,从所述影像信号vd中生成基于水平同步信号的时序信号并供给于扫描驱动器70。而且,显示控制部65基于影像信号vd,将极性反转信号pol、开始脉冲、表示包含时钟信号clk的各种时序信号的控制信号群、及影像数字信号供给于数据驱动器80,所述影像数字信号包含以例如8比特的亮度灰阶指示各像素的亮度电平的、像素数据pd的系列。

[0157]

扫描驱动器70以从显示控制部65供给的控制信号所示的时序,对显示屏20的各水平扫描线s1~sm依次施加水平扫描脉冲。

[0158]

数据驱动器80例如形成为大规模集成电路(large scale integrated circuit,lsi)等半导体装置。数据驱动器80将从显示控制部65供给的影像数字信号所含的像素数据pd,以一水平扫描线、即n个为单位,转换为具有与各像素数据pd对应的灰阶电压的、驱动电压信号g1~驱动电压信号gn。接着,数据驱动器80将所述驱动电压信号g1~驱动电压信号gn施加于显示屏20的数据线d1~数据线dn。此外,扫描驱动器70或数据驱动器80也可电路的一部分或全部与显示屏20一体形成。而且,数据驱动器80也可内置有显示控制部65。而且,数据驱动器80也可由多个lsi构成。

[0159]

图8为表示数据驱动器80的内部结构的一例的框图。

[0160]

如图8所示,数据驱动器80包含正极参照电压产生电路50p、负极参照电压产生电路50n、移位寄存器(shift register)600、数据寄存锁存器700、电平移位电路群800、解码器部900及驱动电路群200_4。此外,驱动电路群200_4包括信号电平转换部100_4。对移位寄存器600及数据寄存锁存器700分别供给有基准电源电压vgnd及正极性的lv电源电压vdd1h。对解码器部900分别供给有基准电源电压vgnd、正极性的hv电源电压vdd2h、负极性的hv电源电压vdd2l。对电平移位电路群800及驱动电路群200_4供给有基准电源电压vgnd、正极性的lv电源电压vdd1h及hv电源电压vdd2h、负极性的lv电源电压vdd1l及hv电源电压vdd2l。

[0161]

移位寄存器600根据开始脉冲,生成用于与时钟信号clk同步地进行锁存器的选择的、多个锁存器时序信号,并供给于数据寄存锁存器700。

[0162]

数据寄存锁存器700接收影像数字信号、极性反转信号pol等控制各种时序的lv控制信号群,基于从移位寄存器600供给的各锁存器时序信号,导入影像数字信号所含的多个像素数据片,并分别以所述锁存器时序供给于电平移位电路群800。此外,数据寄存锁存器700根据极性反转信号pol,将所导入的各像素数据片交替供给于电平移位电路群800所含的正极用的电平移位电路及负极用的电平移位电路。

[0163]

电平移位电路群800将基于逻辑电路用的lv电源电压(vdd1h、vgnd)的、各像素数据片的信号电平,转换为正极hv数字信号(vgnd/vdd2h)及负极hv数字信号(vdd2l/vgnd),并分别供给于解码器部900所含的多个正极解码器90p及多个负极解码器90n。此外,电平移位电路群800也可包含图1(图3)、图2a、图2b所示的信号电平转换电路100、信号电平转换电路100_h、信号电平转换电路100_l、信号电平转换电路100_1中的任一个或组合包含多个。

[0164]

解码器部900例如是对数据驱动器80的每两个输出端子分配一对正极解码器90p及负极解码器90n而构成。此外,在解码器部900内,正极解码器90p及负极解码器90n的排列顺序可变更。例如为了抑制布局面积,也可将同极性的解码器彼此以多个输出的程度汇总而配置。

[0165]

正极参照电压产生电路50p及负极参照电压产生电路50n生成电压值不同的多个参照电压,分别供给于针对数据驱动器80的多个输出端子分别设置的正极解码器90p及负极解码器90n。

[0166]

正极解码器90p及负极解码器90n从所述多个参照电压中,分别选择与正极hv数字信号及负极hv数字信号对应的、正极性的参照电压及负极性的参照电压,并分别作为正极性的灰阶电压及负极性的灰阶电压供给于驱动电路群200_4。

[0167]

驱动电路群200_4接收极性反转信号pol及表示各种时序的lv控制信号群,利用信号电平转换部100_4来生成控制驱动电路群200_4的各驱动电路的时序的、hv电压信号群。信号电平转换部100_4根据lv控制信号群的系统,包括图1(图3)、图2a、图2b所示的信号电平转换电路100、信号电平转换电路100_h、信号电平转换电路100_l、信号电平转换电路100_1中的任一个或组合包括多个。驱动电路群200_4的各驱动电路接收从解码器部900供给的正极性的灰阶电压及负极性的灰阶电压作为正极高电压输入信号(vp)及负极高电压输入信号(vn),并将分别放大而成的正极驱动电压信号(vpa)及负极驱动电压信号(vna)从数据驱动器80的各输出端子输出。此时,驱动电路群200_4在输出不同极性的驱动电压信号的一对驱动电路(例如分别驱动邻接的两个输出端子的一对驱动电路)中,接收极性反转信号pol及时序控制信号作为lv控制信号群,并以与所述lv控制信号群相应的驱动时序,切换从一对驱动电路的各输出端子输出的驱动电压信号的极性。

[0168]

例如,在与极性反转信号pol及时序控制信号相应的驱动时序,由从一对驱动电路中的一者的输出端子输出正极驱动电压信号并且从另一者的输出端子输出负极驱动电压信号的状态,切换为从其中一者的输出端子输出负极驱动电压信号并且从另一者的输出端子输出正极驱动电压信号的状态。

[0169]

此外,电平移位电路群800、解码器部900、驱动电路群200_4分别可由元件耐压较正极及负极的驱动电压范围(vdd2l~vdd2h)更低(例如电压差|vdd2h-vdd2l|的约1/2)的晶体管构成。由此,可缩小驱动器面积,实现低成本化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1