移位寄存器、显示装置、栅极驱动电路及驱动方法与流程

本发明涉及显示,尤其涉及移位寄存器、显示装置、栅极驱动电路及驱动方法。

背景技术:

1、在显示领域,goa(gate on array)是将栅极驱动电路(gate driver ics)制作在阵列基板上的技术。goa电路的本质是移位寄存器,通过级联的移位寄存器控制显示面板的像素逐行扫描,以使得显示面板能够形成显示画面。

2、显示装置采用goa电路,能够有效降低成本、提高良率。

技术实现思路

1、本发明提供一种移位寄存器、显示装置、栅极驱动电路及驱动方法,以实现移位寄存器能够不通过级联信号开启下一行的扫描,能够在外部信号控制下接收并存储一种信号,并在该信号的控制下输出扫描信号,为达到目的,本发明采用如下技术方案:

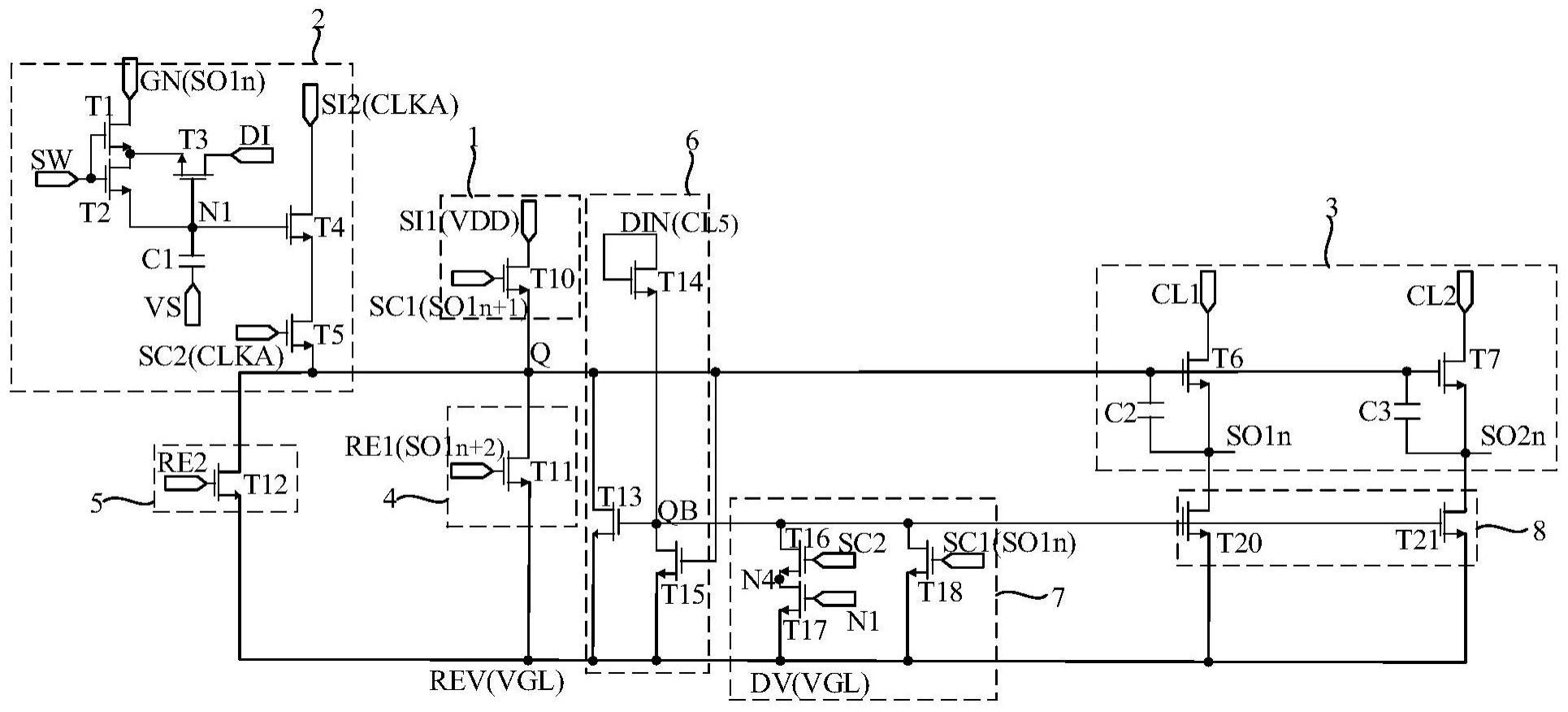

2、一方面,本发明提供一种移位寄存器,包括:存取电路和输出电路。其中,存取电路与信号储存控制端、存取输入控制端、储存信号输入端、存取信号输入端和上拉节点电连接,存取电路被配置为,响应于在储存信号输入端处接收的信号和在信号储存控制端处接收的信号,将在储存信号输入端处接收的信号输入并存储,且存取电路还被配置为,响应于所存储的在储存信号输入端处接收的信号和在存取输入控制端处接收的信号,将在存取信号输入端处接收的信号传输至上拉节点。

3、输出电路与上拉节点、至少一个时钟信号端和至少一个信号输出端电连接,输出电路被配置为,响应于上拉节点的信号,将在至少一个时钟信号端处接收的信号分别传输至至少一个信号输出端。

4、本发明提供的移位寄存器具有存取电路,可实现移位寄存器的上拉节点,在外部信号的控制下储存高电平信号,进而在上拉节点的控制下,使输出电路输出扫描信号。相应地,在多个移位寄存器中具有两种控制模式,多个移位寄存器可以控制显示面板中的像素在一帧图像中形成两种扫描画面。

5、在一些实施例中,所述存取电路被配置为,在所述移位寄存器对应下一帧高清显示区起始位置时,响应于在所述储存信号输入端处接收的信号和在所述信号储存控制端处接收的信号,将在所述储存信号输入端处接收的信号输入并存储;所述至少一个信号输出端中的一个与所述储存信号输入端电连接。在一些实施例中,移位寄存器还包括复位电路,复位电路与上拉节点、复位控制端和复位电压信号端电连接,复位电路被配置为,响应于在复位控制端处接收的信号,将在复位电压信号端处接收的信号传输至上拉节点。

6、在一些实施例中,存取电路包括信号存储子电路和信号提取子电路。其中,信号存储子电路与信号储存控制端、储存信号输入端和第一节点电连接,信号存储子电路被配置为,在移位寄存器对应高清显示区起始位置时,响应于在信号储存控制端处接收的信号,将在储存信号输入端-处接收的信号传输并存储至第一节点。

7、信号提取子电路与第一节点、存取输入控制端和上拉节点电连接,信号提取子电路被配置为,响应于第一节点的信号和在存取输入控制端处接收的信号,将在存取输入控制端处接收的信号传输至上拉节点。

8、在一些实施例中,信号存储子电路包括:第一晶体管、第二晶体管和第一电容。第一晶体管和第二晶体管的控制极均与信号储存控制端电连接,第一晶体管的第一极与储存信号输入端电连接,第一晶体管的第二极与第二晶体管的第一极电连接,第二晶体管的第二极与第一节点电连接,第一电容的第一极与第一节点电连接,第一电容的第二极与稳压信号端电连接。

9、在一些实施例中,信号提取子电路包括:第四晶体管和第五晶体管,第四晶体管的控制极与第一节点电连接,第四晶体管的第一极与存取输入控制端电连接,第四晶体管的第二极与第五晶体管的第一极电连接,第五晶体管的控制极与存取输入控制端电连接,第五晶体管的第二极与上拉节点电连接。

10、在一些实施例中,复位电路包括第十二晶体管,第十二晶体管的控制极与复位控制端电连接,第十二晶体管的第一极与上拉节点电连接,第十二晶体管的第二极与复位电压信号端电连接。

11、在一些实施例中,输出电路包括第一输出电路和第二输出电路,时钟信号端包括第一时钟信号端和第二时钟信号端,信号输出端包括第一信号输出端和第二信号输出端。

12、其中,第一输出电路与上拉节点、第一时钟信号端和第一信号输出端电连接,第一输出电路被配置为,响应于上拉节点的信号,将在第一时钟信号端处接收的信号传输至第一信号输出端;第一信号输出端与储存信号输入端电连接。

13、第一输出电路包括第六晶体管和第二电容,第六晶体管的控制极和第二电容的第一极均与上拉节点电连接,第六晶体管的第一极与第一时钟信号端电连接,第六晶体管的第二极和第二电容的第二极与第一信号输出端电连接。

14、第二输出电路与上拉节点、第二时钟信号端和第二信号输出端电连接,第二输出电路被配置为,响应于上拉节点的信号,将第二时钟信号端处接收的信号传输至第二信号输出端。

15、第二输出电路包括第七晶体管和第三电容,第七晶体管的控制极和第三电容的第一极均与上拉节点电连接,第七晶体管的第一极与第二时钟信号端电连接,第七晶体管的第二极和第三电容的第二极与第二信号输出端电连接。

16、在一些实施例中,输出电路还包括第一稳压电路和/或第二稳压电路。其中,第一稳压电路与第一稳压输入端、上拉节点和第二节点电连接,第二节点还与第六晶体管的控制极和第二电容的第一极电连接,第一稳压电路被配置为,响应于在第一稳压输入端处接收的信号,将上拉节点的信号传输至第二节点;第六晶体管的第一极接收第一时钟信号端处的信号,第一稳压电路还被配置为,响应于在第一稳压输入端处接收的信号和第二节点的信号,将上拉节点和第二节点之间的电流通路中断。

17、第一稳压电路包括第八晶体管,第八晶体管的控制极与第一稳压输入端电连接,第八晶体管第一极与上拉节点电连接,第八晶体管第二极与第二节点电连接。

18、第二稳压电路与第二稳压输入端、上拉节点和第三节点电连接,第三节点还与第七晶体管的控制极和第三电容的第一极电连接,第二稳压电路被配置为,响应于在第二稳压输入端处接收的信号,将上拉节点的信号传输至第三节点;第七晶体管的第一极接收第二时钟信号端处的信号,第二输出稳压电路还被配置为,响应于在第二稳压输入端处接收的信号和第三节点的信号,将上拉节点和第三节点之间的电流通路中断。

19、第二稳压电路包括第九晶体管,第九晶体管的控制极与第二稳压输入端电连接,第九晶体管第一极与上拉节点电连接,第九晶体管第二极与第三节点电连接。

20、在一些实施例中,移位寄存器还包括:输入电路和级联复位电路。其中,输入电路与上拉输入控制端、上拉信号输入端和上拉节点电连接,输入电路被配置为,响应于在上拉输入控制端处接收的信号,将在上拉信号输入端处接收的信号传输至上拉节点。

21、输入电路包括第十晶体管,第十晶体管的控制极与上拉输入控制端电连接,第十晶体管的第一极与第一信号输入端电连接,第十晶体管的第二极与上拉节点电连接。

22、级联复位电路与上拉节点、级联复位控制端和复位电压信号端电连接,级联复位电路被配置为,响应于在级联复位控制端处接收的信号,将在复位电压信号端处接收的信号传输至上拉节点。

23、级联复位电路包括第十一晶体管,第十一晶体管的控制极与级联复位控制端电连接,第十一晶体管的第一极与上拉节点电连接,第十一晶体管的第二极与复位电压信号端电连接。

24、在一些实施例中,移位寄存器单元还包括下拉控制电路,下拉控制电路与下拉信号输入端、上拉节点、下拉节点和下拉电压信号端电连接。下拉控制电路被配置为,响应于上拉节点的信号和在下拉信号输入端处接收的信号,将在下拉电压信号端处接收的信号传输至下拉节点,以及,响应于下拉节点的信号,将在下拉电压信号端处接收的信号传输至上拉节点。

25、下拉控制电路包括第十三晶体管、第十四晶体管和第十五晶体管,第十三晶体管的控制极与上拉节点电连接,第十三晶体管的第一极与下拉节点电连接,第十三晶体管的第二极与下拉电压信号端电连接;第十四晶体管的控制极和第一极均与下拉信号输入端电连接,第十四晶体管的第二极与下拉节点电连接;第十三晶体管的控制极与下拉节点电连接,第十三晶体管的第一极与上拉节点电连接,第十三晶体管的第二极与下拉电压信号端电连接。第十五晶体管的控制极与上拉节点电连接,第十五晶体管的第一极与第十四晶体管的第二极电连接,第十五晶体管的第二极与下拉电压信号端电连接。

26、在一些实施例中,移位寄存器单元还包括下拉复位电路和输出复位电路。下拉复位电路与下拉节点、上拉输入控制端、存取输入控制端、第一节点、下拉电压信号端和下拉节点电连接,下拉复位电路被配置为,响应于在上拉输入控制端处接收的信号或者响应于在存取输入控制端处接收的信号和第一节点的信号,将在下拉电压信号端处接收的信号传输至下拉节点。

27、下拉复位电路包括第十六晶体管、十七晶体管和第十八晶体管。第十六晶体管的控制极与存取输入控制端电连接,第十六晶体管的第一极与下拉节点电连接,第十六晶体管的第二极与第四节点电连接,第十七晶体管的控制极与第一节点的电连接,第十七晶体管的第一极与第四节点电连接,第十七晶体管的第二极与下拉电压信号端电连接。第十八晶体管的控制极与上拉输入控制端电连接,第十八晶体管的第一极与下拉节点电连接,第十八晶体管的第二极与下拉电压信号端电连接;

28、输出复位电路与信号输出端、下拉电压信号端和下拉节点电连接,输出复位电路被配置为,响应于下拉节点的信号,将在下拉电压信号端处接收的信号传输至信号输出端。

29、输出复位电路包括第二十晶体管和第二十一晶体管,第二十晶体管的控制极与下拉节点电连接,第二十晶体管的第一极与第一信号输出端电连接,第二十晶体管的第二极与下拉电压信号端电连接;第二十一晶体管的控制极与下拉节点电连接,第二十一晶体管的第一极与第二信号输出端电连接,第二十一晶体管的第二极与下拉电压信号端电连接。

30、在一些实施例中,下拉复位电路还包括放电电路,放电电路与第四节点、复位控制端和下拉电压信号端电连接,放电电路被配置为,响应于在复位控制端处接收的信号,将在下拉电压信号端处接收的信号传输至第四节点。

31、放电电路包括第十九晶体管,第十九晶体管的控制极与第二复位信号端电连接,第十九晶体管的第一极与第四节点电连接,第十九晶体管的第二极与下拉电压信号端电连接。

32、另一方面,本发明提供一种栅极驱动电路,包括如上述任一项实施例的移位寄存器。

33、本发明的栅极驱动电路采用上述移位寄存器,具有与上述移位寄存器相同的有益效果,在此不做赘述。

34、在一些实施例中,多个移位寄存器分为至少两个移位寄存器组,每个移位寄存器组包括依次排列的至少两个移位寄存器。栅极驱动电路还包括多条复位控制线和多条信号储存控制线,每个移位寄存器组中各移位寄存器的信号储存控制端与一条信号储存控制线电连接,每个移位寄存器组中各移位寄存器的复位控制端与一条复位控制线电连接。

35、在一些实施例中,多个移位寄存器分为两个级联组,每个级联组中的第n级移位寄存器的第一信号输出端与第n+1级移位寄存器的上拉输入控制端电连接。每个级联组中的第m级移位寄存器的信号输出端与第m-2级移位寄存器的第一复位信号端电连接。其中,n为大于或等于1的正整数,m为大于或等于3的正整数。

36、在一些实施例中,栅极驱动电路所包括多个移位寄存器依次排列,相邻h个移位寄存器为一个输出组;第奇数个输出组属于第一级联组,第偶数个输出组属于第二级联组,其中,h为大于或等于3的正整数。

37、在一些实施例中,栅极驱动电路还包括两个时钟信号线组,每个时钟信号线组与一个级联组中的各输出组电连接。每个时钟信号线组包括k×h条时钟信号线,每个时钟信号线组中各时钟信号线,分别与输出组中各移位寄存器的一个时钟信号端其中,k为大于或等于1的正整数。

38、又一方面,本发明提供一种显示装置,包括如上述另一方面中任一项实施例提供的栅极驱动电路。

39、本发明的显示装置采用上述栅极驱动电路,具有与上述栅极驱动电路相同的有益效果,在此不做赘述。

40、再一方面,本发明提供一种应用于如上述另一方面中任一项实施例提供的栅极驱动电路的驱动方法。其中,栅极驱动电路包括多个移位寄存器,分为至少两个移位寄存器组,每个移位寄存器组包括依次排列的至少两个移位寄存器。栅极驱动电路还包括多条第二复位控制线和多条信号储存控制线,每个移位寄存器组中各移位寄存器的信号储存控制端与一条信号储存控制线电连接,每个移位寄存器组中各移位寄存器的复位控制端与一条复位控制线电连接。

41、在一些实施例中,驱动方法包括:每个移位寄存器组中各移位寄存器在与其电连接的信号储存控制线传输的信号的控制下,将在储存信号输入端处接收的信号输入并存储。每个移位寄存器组中各移位寄存器在与其电连接的复位控制线传输的信号的控制下,对各移位寄存器进行复位。

42、本发明提供的的栅极驱动电路的驱动方法可以实现移位寄存器有多种的输入控制方式,满足级联电路可以控制其中的任一个移位寄存器输出扫描信号,相应地,丰富了显示面板中像素的控制模式,即可以控制多行像素中任一行像素发光,形成画面,其它位置的像素为熄灭状态。

43、在一些实施例中,本发明提供的栅极驱动电路的驱动方法的具体图像显示中的方法为:

44、在第一帧图像显示阶段,栅极驱动电路的各移位寄存器输出栅极扫描信号。根据第二帧图像的高清显示区的位置,确定多个移位寄存器中与高清显示区的首个子像素行电连接的移位寄存器,作为首个移位寄存器。在首个移位寄存器的储存信号输入端接收信号时,在与首行移位寄存器电连接的栅极驱动电路的信号储存控制线的控制下,将在储存信号输入端处接收的信号存储至首个移位寄存器中。

45、在第二帧图像显示阶段,包括:高清显示阶段和低清显示阶段。其中,在高清显示阶段,首个移位寄存器在储存信号输入端处接收的信号和存取输入控制端处接收的信号的控制下,输出栅极扫描信号。与高清显示区的子像素电连接的移位寄存器依次输出栅极扫描信号。在低清显示阶段,低清显示区包括第一低清显示区和第二低清显示区,第一低清显示区和第二低清显示区分别位于高清显示区的两侧。与第一低清显示区连接的多个移位寄存器在起始信号线传输的信号的控制下,输出栅极扫描信号。与第二低清显示区连接的多个移位寄存器,在与高清显示区连接的移位寄存器输出的级联信号的控制下,输出栅极扫描信号。在对第一低清显示区扫描结束后,对与第一低清显示区连接的多个移位寄存器进行复位。在对第二低清显示区扫描结束后,对与第二低清显示区连接的多个移位寄存器进行复位。

46、在高清显示阶段或低清显示阶段中,根据下一帧图像的高清显示区位置,确定多个移位寄存器中与高清显示区的首个子像素行电连接的移位寄存器,作为下一帧图像的首个移位寄存器,下一帧图像的首个移位寄存器接收储存信号输入信号并存储;

47、在第三帧图像显示阶段至第e帧图像显示阶段中,重复第二帧图像显示阶段的步骤,其中e是大于或等于4的正整数。

- 还没有人留言评论。精彩留言会获得点赞!