时序控制电路、显示模组及显示装置的制作方法

1.本发明一般涉及液晶显示技术领域,具体涉及显示面板关机时序同步电路,尤其涉及时序控制电路、显示模组及显示装置。

背景技术:

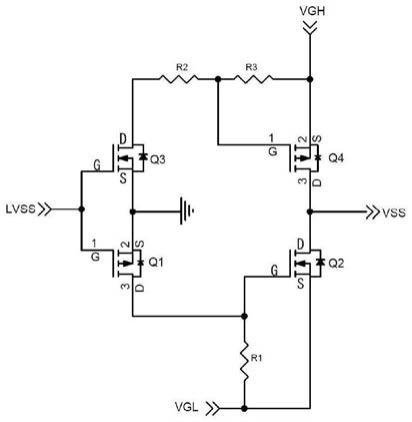

2.在tft液晶面板的goa(gate on array)驱动电路中,通常只需要一路负压电源vss。因大尺寸、高刷新率的tft液晶面板存在充电不足问题,需要两路负压电源lvss和vss,其中lvss电压的绝对值较vss电压绝对值大,其中,lvss为goa电路中clk信号提供负压电源,vss为goa电路中其他信号提供负压电源。

3.如图1和图2所示,现有技术中通常采用图1所示的电路图进行时序控制,其中,vgh、lvss、vgl为输入信号,vss为输出信号,实现了正常工作时vss电压输出vgl及关机时vss与vgh的时序同步,硬件采用了四个晶体管,和三个电阻结构,由于元器件数量较多,发射故障的概率相对较大,维修成本也相应较高。

技术实现要素:

4.鉴于现有技术中的上述缺陷或不足,期望提供一种时序控制电路、显示模组及显示装置。

5.第一方面,提供一种时序控制电路,包括第一负压信号输入端,第二负压信号输入端,和信号输出端,所述第一负压信号输入端电压的绝对值大于所述第二负压信号输入端电压的绝对值,

6.第一开关管和第二开关管,所述第一开关管和所述第二开关管设置在所述第一负压信号输入端和所述信号输出端之间,用于通过所述第一开关管控制所述第二开关管的开闭状态,

7.所述第一开关管和所述第二开关管之间连接所述第二负压信号输入端,用于在所述第二开关管导通时,信号输出端输出所述第二负压信号输入端的电压信号,

8.第三开关管,所述第三开关管设置在所述第一负压信号输入端和所述信号输出端,用于在所述第三开关管导通时,信号输出端输出所述第一负压信号输入端的电压信号。

9.第二方面,提供一种显示模组,包括上述时序控制电路。

10.第三方面,提供一种显示装置,包括上述显示模组。

11.根据本技术实施例提供的技术方案,实现在正常工作时,信号输出端电压输出第二负压信号输入端的电压信号,在关机时,信号输出端输出第一负压信号输出端的电压信号,实现开关机时的电压信号时序同步,并且,本实施例提供的时序控制电路中采用的硬件结构相对简单,元器件数量相对较少,因此,发生硬件的故障概率相对较低。

附图说明

12.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本技术的其它

特征、目的和优点将会变得更明显:

13.图1为现有技术中负压时序控制电路;

14.图2为现有技术电路工作时序图;

15.图3为本实施例中时序控制电路图;

16.图4为本实施中时序控制电路各元器件功能示意图;

17.图5为本实施例中时序控制电路工作时序图。

具体实施方式

18.下面结合附图和实施例对本技术作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与发明相关的部分。

19.需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。

20.请参考图3,本实施例提供一种时序控制电路,包括第一负压信号输入端lvss,第二负压信号输入端,vgl和信号输出端vss,所述第一负压信号输入端lvss电压的绝对值大于所述第二负压信号输入端vgl电压的绝对值,

21.第一开关管q1和第二开关管q2,所述第一开关管q1和所述第二开关管q2设置在所述第一负压信号输入端lvss和所述信号输出端vss之间,用于通过所述第一开关管q1控制所述第二开关管q2的开闭状态,

22.所述第一开关管q1和所述第二开关管q2之间连接所述第二负压信号输入端vgl,用于在所述第二开关管q2导通时,信号输出端vss输出所述第二负压信号输入端vgl的电压信号,

23.第三开关管d1,所述第三开关管d1设置在所述第一负压信号输入端lvss和所述信号输出端vss,用于在所述第三开关管d1导通时,信号输出端输vss出所述第一负压信号输入端lvss的电压信号。

24.本实施提供的时序控制电路实现在正常工作时,信号输出端电压输出第二负压信号输入端的电压信号,在关机时,信号输出端输出第一负压信号输出端的电压信号,实现开关机时的电压信号时序同步,并且,本实施例提供的时序控制电路中采用的硬件结构相对简单,元器件数量相对较少,因此,发生硬件的故障概率相对较低。

25.其中,第一负压信号输入端和lvss信号输出端vss之间连接第一开关管q1和第二开关管q2,通过第一开关管q1控制第二开关管q2的开闭状态,并且当第一开关管q1和第二开关管q2均为导通状态时,实现信号输出端vss的电压为第二负压信号输入端vgl的电压;当第一开关管q1和第二开关管q2为断开状态时,实现信号输出端vss的电压为第一负压信号输入端lvss的电压。其中,第一负压输入信号为lvss,第二负压输入信号为vgl,信号输出端为vss,其中vgl为负压,lvss、vss在正常工作期间分别为lvgl,和vgl电压,关机时,lvss和vss均切换为vgh电压。

26.进一步的,所述第一开关管q1为p型晶体管,所述第一开关管q1的栅极连接至所述第一负压信号输入端lvss,源极接地,漏极连接至所述第二开关管q2的栅极。

27.如图3所示,本实施例中采用p型晶体管作为第一开关管,第一开关管的栅极连接

至第一负压信号输入端,通过输入的第一负压信号控制该p型晶体管的导通和关断,漏极连接至第二开关管的栅极,通过该漏极的电压控制第二开关管的导通和关断。

28.进一步的,所述第二开关管q2为n型晶体管,所述第二开关管q2的栅极连接至所述第一开关管q1的漏极和所述第二负压信号输入端vgl,源极连接至所述第二负压信号输入端vgl,漏极连接至信号输出端vss。

29.如图3所示,本实施例中采用n型晶体管作为第二开关管q2,第二开关管q2的栅极连接至上述p型晶体管,通过第一开关管控制该第二开关管q2的导通和关断,当该n型晶体管为导通状态时,实现输出端的电压信号为连接至源极的第二负压信号输入端vgl的电压信号。

30.进一步的,所述第二负压信号输入端vgl与所述第二开关管q2栅极之间还设有电阻r1。

31.本实施例设置的第二开关管q2主要用于在该晶体管导通时,使得输出端的电压为第二负压信号输入端的电压,并且当第一开关管和第二开关管断开时,第二负压信号输入端的电压不会对信号输出端的电压产生影响,造成干扰。

32.进一步的,所述第三开关管d1为二极管,所述二极管阳极连接至所述第一负压信号输入端lvss,阴极连接至所述信号输出端vss。

33.本实施例在第一负压信号输入端lvss和信号输出端vss之间连接二极管,当第一开关管q1和第二开关管q2都为断开状态时,该二极管为导通状态,实现信号输出端的电压为第一负压信号输入端的电压,通过第一负压信号输入端lvss高低电压的切换,实现信号输出端高低压输出的功能。

34.如图4所示为本实施例中各元器件功能示意图,具体的,在工作状态下,第一负压信号输入端lvss通过q1的导通状态改变q2控制信号的电压,以此控制q2为导通状态,从而实现信号输出端vss的输出电压为第一负压信号输入端的电压vgl,第一负压信号输入端lvss通过控制d1为断开状态,保证lvss电压不会干扰到vss的正常输出;关机掉电时刻,第一负压信号输入端lvss通过q1的断开状态改变q2控制信号的电压,以此控制q2为断开状态,实现第二负压信号输入端vgl的电压不会干扰到信号输出端vss电压,第一负压信号输入端lvss通过控制d1为导通状态,实现信号输出端vss电压为第一负压信号输入端的lvss电压。以上,通过lvss高低电压的切换,实现vss输出为vgl或vgh的功能。

35.如图5所示,为本实施例中时序控制电路的时序图,其中,输入信号为lvss、vgl,输出信号为vss,其中vgl为负压,lvss、vss正常工作期间分别为lvgl和vgl电压,关机时lvss和vss均切换为vgh电压;开机时刻t0后,lvss电压为负压lvgl,因q1源极为0v,因此q1处于导通状态,q2栅极电压为0v,因此q2导通,vss输出为vgl电压,在此期间,因二极管负极电压vss电压大于lvss电压,二极管d1处于截止状态;关机时刻t1后,lvss切换为vgh电压,q1栅极电压大于源极电压,q1由导通状态切换为关闭状态,此时在r1作用下,q2栅极电压为vgl电压,因q2栅极电压等于源极电压,q2由导通状态切换为关闭状态,至此vss不再输出vgl电压,此时因lvss电压为vgh电压,二极管d1由截止状态切换为导通状态,vss输出vgh电压。在本发明技术方案中,面板正常工作期间vss输出为vgl电压,因二极管d1为截止状态,所以lvss与vss的不会受彼此影响。在关机后,因q2为关闭状态,vgl与vss也不会受彼此影响。参考图2中现有技术的时序控制电路,本发明技术方案实现了正常工作时vss电压输出vgl及

关机时vss与vgh的时序同步,同时,采用了更少的元器件。

36.在上述实施例中,lvss等于-12v,vgl等于-6v,vgh等于25v。

37.本实施例还提供一种显示模组,包括上述时序控制电路。

38.本实施例提供的显示模组中,采用上述时序控制电路进行输出信号电压的控制,并且电路硬件结构相对简单、元器件数量相对较少,因而发生硬件的故障概率相对较低。

39.进一步的,所述显示模组包括pcb基板,所述时序控制电路设置在所述pcb基板上。

40.本实施例中的时序控制电路可以直接设置在显示模组的pcb基板上,直接采用各个元器件在pcb基板上进行相应电路的搭建;

41.进一步的,还包括ic芯片,上述ic芯片用于集成上述时序控制电路,所述显示模组包括pcb基板,所述ic芯片设置在所述pcb基板上。

42.或者,将上述时序控制电路制备成ic芯片,将ic芯片安装在相应的pcb基板上。

43.本实施例还提供一种显示装置,包括上述显示模组。

44.该显示装置可以为大尺寸高刷新率的电视、显示器、车载导航等显示设备,其实现原理与技术效果与上述实施例中提供的时序控制电路的实现原理和技术效果相同,在此不再赘述。

45.以上描述仅为本技术的较佳实施例以及对所运用技术原理的说明。本领域技术人员应当理解,本技术中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离所述发明构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本技术中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1