显示基板及其驱动方法、显示装置与流程

本公开涉及显示,特别是涉及一种显示基板及其驱动方法、显示装置。

背景技术:

1、有机发光二极管(organic light-emitting diode,oled)屏幕具有轻薄、亮度高、功耗低、响应快、清晰度高、柔性好以及发光效率高等优点,能满足消费者对显示技术的新需求。

技术实现思路

1、本公开提供了一种显示基板,包括:衬底,以及设置在所述衬底一侧的第一栅极驱动电路、第二栅极驱动电路和阵列排布的多个像素驱动电路,所述第一栅极驱动电路包括相互级联的多个第一移位寄存器,所述第二栅极驱动电路包括相互级联的多个第二移位寄存器,所述像素驱动电路包括:

2、写入模块,与数据端、第一节点以及写入控制端连接,用于根据所述写入控制端的信号,将所述数据端的信号写入所述第一节点;

3、驱动模块,与所述第一节点、第二节点以及第三节点连接,用于根据所述第二节点的电位,将所述第一节点的电压写入所述第三节点,所述第三节点还与发光器件连接;以及

4、补偿模块,与所述第三节点、所述第二节点以及补偿控制端连接,用于根据所述补偿控制端的信号,将所述第三节点的信号写入所述第二节点;

5、其中,所述多个像素驱动电路包括:位于不同行的第一像素驱动电路和第二像素驱动电路,所述第一像素驱动电路的写入控制端与所述第二像素驱动电路的写入控制端分别连接不同的第一移位寄存器,所述第一像素驱动电路的补偿控制端与所述第二像素驱动电路的补偿控制端连接同一第二移位寄存器;并且

6、所述第一像素驱动电路用于驱动第一像素的发光器件发光,所述第二像素驱动电路用于驱动第二像素的发光器件发光,在所述第一像素驱动电路的数据端与所述第二像素驱动电路的数据端写入相同信号的情况下,所述第一像素与所述第二像素的发光亮度之差小于或等于两个灰阶。

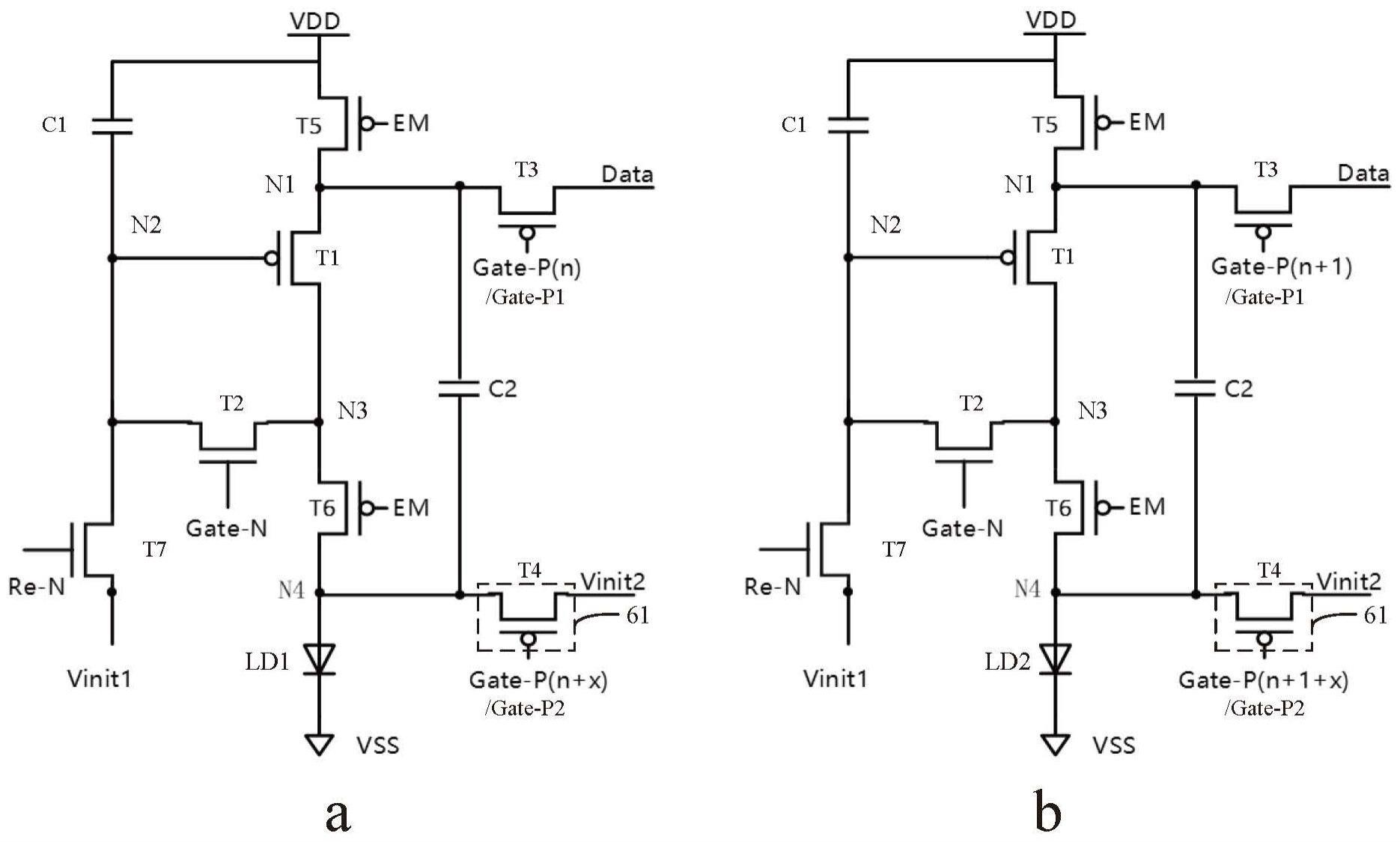

7、在一些实施方式中,所述第一像素驱动电路与所述第二像素驱动电路的结构不同。

8、在一些实施方式中,所述像素驱动电路还包括:

9、第一电容,第一极板与第一电压端连接,第二极板与所述第二节点连接,用于存储所述第二节点的信号;

10、其中,所述第一像素驱动电路中第一电容的容值,与所述第二像素驱动电路中第一电容的容值不同。

11、在一些实施方式中,所述第一像素驱动电路的写入控制端与第n级第一移位寄存器的输出端连接,所述第二像素驱动电路的写入控制端与第n+i级第一移位寄存器的输出端连接,所述n与所述i均为大于或等于1的正整数;

12、其中,所述第一像素驱动电路中第一电容的容值,大于所述第二像素驱动电路中第一电容的容值。

13、在一些实施方式中,所述第一电容的第一极板上具有开口,且所述开口在所述衬底上的正投影位于所述第一电容的第二极板在所述衬底上的正投影范围内;

14、其中,所述第一像素驱动电路中的所述开口在所述衬底上的正投影面积,小于所述第二像素驱动电路中的所述开口在所述衬底上的正投影面积。

15、在一些实施方式中,所述驱动模块包括:

16、第一晶体管,控制极与所述第二节点连接,第一极与所述第一节点连接,第二极与所述第三节点连接;

17、其中,所述第一像素驱动电路中第一晶体管的沟道宽长比,与所述第二像素驱动电路中第一晶体管的沟道宽长比不同。

18、在一些实施方式中,所述第一像素驱动电路的写入控制端与第n级第一移位寄存器的输出端连接,所述第二像素驱动电路的写入控制端与第n+i级第一移位寄存器的输出端连接,所述n与所述i均为大于或等于1的正整数;

19、其中,所述第一像素驱动电路中第一晶体管的沟道宽长比,小于所述第二像素驱动电路中第一晶体管的沟道宽长比。

20、在一些实施方式中,所述第一像素驱动电路与所述第二像素驱动电路的结构相同。

21、在一些实施方式中,所述像素驱动电路还包括:

22、第一复位模块,与复位控制端、第一复位端以及第四节点连接,用于根据所述复位控制端的信号,将所述第一复位端的信号写入所述第四节点,所述第四节点还与发光器件的第一极连接;以及

23、第二电容,第一极板与所述第一节点连接,第二极板与所述第四节点连接;

24、其中,所述第一像素驱动电路的写入控制端与第n级第一移位寄存器的输出端连接,所述第一像素驱动电路的复位控制端与第n+x级第一移位寄存器的输出端连接,所述第二像素驱动电路的写入控制端与第n+i级第一移位寄存器的输出端连接,所述第二像素驱动电路的复位控制端与第n+i+x级第一移位寄存器的输出端连接,所述n、所述x以及所述i均为大于或等于1的正整数。

25、在一些实施方式中,所述x大于或等于2,且小于或等于10。

26、在一些实施方式中,所述补偿模块包括:

27、第二晶体管,控制极与所述补偿控制端连接,第一极与所述第三节点连接,第二极与所述第二节点连接;

28、所述写入模块包括:第三晶体管,控制极与所述写入控制端连接,第一极与所述数据端连接,第二极与所述第一节点连接;

29、其中,所述第二晶体管包括氧化物晶体管,所述第三晶体管包括多晶硅晶体管。

30、在一些实施方式中,所述第一像素驱动电路位于奇数行,所述第二像素驱动电路位于与所述奇数行相邻的偶数行。

31、本公开提供了一种显示装置,包括:发光器件,以及如任一实施方式所述的显示基板,其中,所述显示基板与所述发光器件连接,用于驱动所述发光器件发光。

32、本公开提供了一种驱动方法,应用于如任一实施方式所述的显示基板,所述驱动方法包括:

33、控制所述第一栅极驱动电路向所述第一像素驱动电路的写入控制端输出第一写入控制信号,向所述第二像素驱动电路的写入控制端输出第二写入控制信号,控制所述第二栅极驱动电路向所述第一像素驱动电路的补偿控制端以及所述第二像素驱动电路的补偿控制端输出补偿控制信号,以使所述第一像素驱动电路将其数据端的信号写入其第二节点,所述第二像素驱动电路将其数据端的信号写入其第二节点,其中,在一个帧周期内,所述补偿控制信号的脉冲时段覆盖所述第一写入控制信号的脉冲时段以及所述第二写入控制信号的脉冲时段,且所述第一写入控制信号的脉冲时段与所述第二写入控制信号的脉冲时段无交叠。

34、在一些实施方式中,在一个帧周期内,所述第一写入控制信号的脉冲时段提前于所述第二写入控制信号的脉冲时段,所述补偿控制信号的脉冲后沿与所述第一写入控制信号的脉冲后沿之间的时长为第一时长,所述补偿控制信号的脉冲后沿与所述第二写入控制信号的脉冲后沿之间的时长为第二时长,且所述第一时长与所述第二时长之差,与所述第一时长的比值小于或等于1/8。

35、在一些实施方式中,所述第一时长与所述第二时长之差为1h,所述第一时长大于或等于8h,所述h为所述显示基板扫描一行所述像素驱动电路所需要的时长。

36、在一些实施方式中,所述第一写入控制信号的脉冲宽度与所述第二写入控制信号的脉冲宽度不同。

37、在一些实施方式中,在一个帧周期内,所述第一写入控制信号的脉冲时段提前于所述第二写入控制信号的脉冲时段,所述第一写入控制信号的脉冲宽度小于所述第二写入控制信号的脉冲宽度。

38、在一些实施方式中,在所述控制所述第一栅极驱动电路向所述第一像素驱动电路的写入控制端输出第一写入控制信号,向所述第二像素驱动电路的写入控制端输出第二写入控制信号的步骤之前,还包括:

39、向所述第一栅极驱动电路提供第一时钟信号和第二时钟信号,以使所述第一栅极驱动电路根据所述第一时钟信号生成所述第一写入控制信号,根据所述第二时钟信号生成所述第二写入控制信号,其中,所述第一时钟信号的占空比小于所述第二时钟信号的占空比。

40、在一些实施方式中,当所述像素驱动电路还包括第一复位模块以及第二电容,所述第一复位模块与复位控制端、第一复位端以及第四节点连接,所述第四节点还与发光器件的第一极连接,所述第二电容的第一极板与所述第一节点连接,第二极板与所述第四节点连接,且所述第一像素驱动电路的写入控制端与第n级第一移位寄存器的输出端连接,所述第一像素驱动电路的复位控制端与第n+x级第一移位寄存器的输出端连接,所述第二像素驱动电路的写入控制端与第n+i级第一移位寄存器的输出端连接,所述第二像素驱动电路的复位控制端与第n+i+x级第一移位寄存器的输出端连接,所述n、所述i以及所述x均为大于或等于1的正整数时,在所述控制所述第一栅极驱动电路向所述第一像素驱动电路的写入控制端输出第一写入控制信号,向所述第二像素驱动电路的写入控制端输出第二写入控制信号的步骤之后,还包括:

41、控制所述第一栅极驱动电路向所述第一像素驱动电路的复位控制端输出第一复位控制信号,向所述第二像素驱动电路的复位控制端输出第二复位控制信号,其中,在一个帧周期内,所述补偿控制信号的脉冲时段还覆盖所述第一复位控制信号的脉冲时段以及所述第二复位控制信号的脉冲时段,且所述第一复位控制信号的脉冲时段与所述第二复位控制信号的脉冲时段无交叠。

42、上述说明仅是本公开技术方案的概述,为了能够更清楚了解本公开的技术手段,而可依照说明书的内容予以实施,并且为了让本公开的上述和其它目的、特征和优点能够更明显易懂,以下特举本公开的具体实施方式。

- 还没有人留言评论。精彩留言会获得点赞!