用于处理器设计实验课程的FPGA硬件设计验证方法

本发明属于fpga硬件设计验证,具体涉及用于处理器设计实验课程的fpga硬件设计验证方法。

背景技术:

1、处理器设计一直是计算机科学领域非常重要的研究问题。近年来,随着硬件技术的发展,冯·诺依曼的经典计算机处理器结构开始陷入性能瓶颈,处理器设计开始寻求突破。处理器设计课程是计算机专业的核心课程之一,它涉及到计算机系统的基本原理和结构,以及处理器的功能、性能和优化。处理器设计课程不仅要求学生掌握理论知识,还要求学生具备实践能力,能够通过实验平台进行处理器的设计、实现和测试。处理器设计课程对于培养学生的创新思维、工程素养和团队协作能力有着重要的作用。但与其他计算机课程不同的是,处理器设计课程是一门偏向硬件的基础课程,课程内容偏向硬件设计的知识内容,概念相对具体繁琐。因此,真正想要掌握课程内容需要进行大量的实验。

2、作为处理器设计课程的重要组成部分,实验教学一直以来是较为困难的。目前,处理器设计课程主要有两种实验手段:一种是采用软件仿真的方式来模拟硬件设备运行,另一种是进行真正的硬件设计。软件仿真的方式相较于硬件设计而言,实现较为简单,具有较高的自由度,但由于软件仿真一般仅使用仿真器或仿真软件,并不涉及到电路设计中信号线、寄存器等基础概念,与真实的硬件工程设计相差较远,因此,多数情况下,软件仿真实验只能起到帮助学生理解抽象概念、梳理硬件设备运行流程的作用,不能达到处理器设计课程中提升学生硬件工程素质的课程目标。目前的硬件设计实验广泛地采用fpga来进行。fpga具有开发周期短、并发度高、重构性好等优点,并且fpga开发流程与硬件工程实际较为接近,能够提高学生的硬件系统设计和调试能力。

3、但是,使用fpga进行实验时,设计的正确性验证较为困难。基于fpga的硬件设计验证有两个步骤:仿真验证和板上验证。这两个步骤都需要查看复杂的时序波形图来验证设计的正确性。而时序波形图的信号数量繁多,时序关系复杂,人工检查波形图的工作量非常大、效率很低,并且检查的结果具有很强的随机性。针对板上验证而言,还需要先使用逻辑分析仪或示波器等设备来抓取波形,才能进行时序波形图的观察。

4、由于目前硬件设计所使用的波形验证的方法存在验证效率低,验证周期长等问题,整体流程是比较繁琐且漫长的,并且在纠错检验方面也有一定的难度,学生很难在有限的实验时间内完成课程实验设计。

技术实现思路

1、本发明要解决的问题是解决在处理器设计实验课程过程中人工检查波形的工作,提高处理器设计实验过载中分析推断设计错误的原因的速度,提出用于处理器设计实验课程的fpga硬件设计验证方法。

2、为实现上述目的,本发明通过以下技术方案实现:

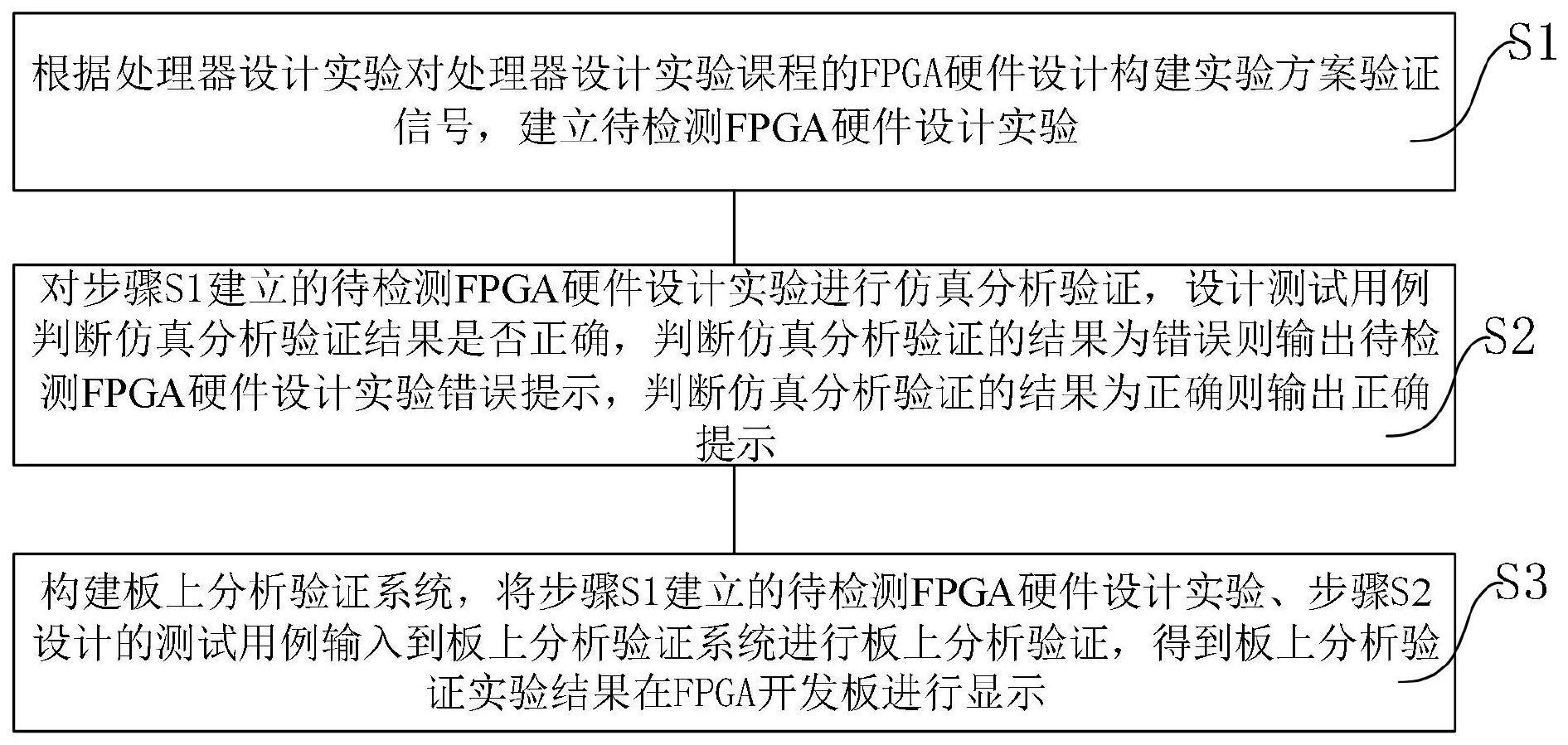

3、一种用于处理器设计实验课程的fpga硬件设计验证方法,包括如下步骤:

4、s1、根据处理器设计实验对处理器设计实验课程的fpga硬件设计构建实验方案验证信号,建立待检测fpga硬件设计实验;

5、s2、对步骤s1建立的待检测fpga硬件设计实验进行仿真分析验证,设计测试用例判断仿真分析验证结果是否正确,判断仿真分析验证的结果为错误则输出待检测fpga硬件设计实验错误提示,判断仿真分析验证的结果为正确则输出正确提示;

6、s3、构建板上分析验证系统,将步骤s1建立的待检测fpga硬件设计实验、步骤s2设计的测试用例输入到板上分析验证系统进行板上分析验证,得到板上分析验证实验结果在fpga开发板进行显示。

7、进一步的,步骤s1的具体实现方法包括如下步骤:

8、s1.1、构建五段流水线cpu的五个流水段分别为取指段、译码段、执行段、访存和写回段,构建指令集包括运算指令、跳转指令、数据存取指令;

9、s1.2、设置运算指令的执行为将运算的结果写回到指令的寄存器中,检测写回的寄存器号和写回的数据;

10、设置跳转指令,检测控制流是否正确,为检测跳转指令跳转前后程序计数器pc的值;

11、设置数据存取指令为存数据指令和取数据指令,设置存数据指令和取数据指令的内存地址相同,通过取数据的方式检测存数据是否正确,取数据的结果写入到寄存器中,检测写回的寄存器号和写回的数据;

12、s1.3、根据步骤s1.2的指令集构建实验方案验证信号为指令执行时程序计数器信号wb_pc、指令是否会写回信号rf_wen、指令写回时的通用寄存器号rf_waddr,指令写回的数据信号rf_wdata;

13、s1.4、建立待检测fpga硬件设计实验。

14、进一步的,步骤s2的具体实现方法包括如下步骤:

15、s2.1、设计处理器实验的测试用例,将正确设计的fpga硬件设计实验的cpu接入到testbench中运行,输入测试用例,获取实验方案验证信号的标准结果序列,构建实验方案验证信号的标准结果数据库;

16、s2.2、将步骤s2得到的待检测fpga硬件设计实验接入到步骤s2.1构建的testbench中运行仿真分析验证,在运行过程中采集实验方案验证信号与实验方案验证信号的标准结果数据库中的实验方案验证信号的标准结果进行对比,对比的计算公式为:

17、res1=(wb_pc==wb_pc_s)

18、res2=(rf_wen==rf_wen_s)

19、res3=(rf_waddr==rf_waddr_s)

20、res4=(rf_wdata==rf_wdata_s)

21、res=(res1)and(res2)and(res3)and(res4)

22、其中,wb_pc_s为指令执行时程序计数器信号标准结果,resl为指令执行时程序计数器信号对比结果,rf_wen_s为指令是否会写回信号标准结果,res2为指令是否会写回信号对比结果,rf_waddr_s为指令写回时的通用寄存器号标准结果,res3为指令写回时的通用寄存器号对比结果,rf_wdata_s为指令写回的数据信号标准结果,res4为指令写回的数据信号对比结果,res为待检测fpga硬件设计实验仿真分析验证结果;

23、s2.3、当采集实验方案验证信号与实验方案验证信号的标准结果数据库中的实验方案验证信号的标准结果进行对比全部相同,则输出res的结果为正确;

24、s2.4、当判断仿真分析验证的结果为错误则输出待检测fpga硬件设计实验错误结果,当实验方案验证信号与实验方案验证信号的标准结果数据库中的实验方案验证信号对比结果不同时,结束testbench运行,记录错误运行指令、错误实验方案验证信号显示于仿真软件的控制台。

25、进一步的,步骤s3中构建板上分析验证系统包括信号抓取模块,数据对比模块,错误检测模块,信息显示模块、顶层模块,其中顶层模块分别连接信号抓取模块,数据对比模块,错误检测模块,信息显示模块,并通过模块例化调用待检测设计;

26、所述信号抓取模块用于预先存储驱动检测运行的特定测试用例;

27、数据对比模块用于将标准数据与待检测fpga硬件设计实验的数据进行比对;

28、错误检测模块用于在数据对比不一致时,根据错误现象进行错误类型判断,并分析待检测fpga硬件设计实验中出现错误的原因;

29、信息显示模块用于根据待检测fpga硬件设计实验是否正确,调用外设显示信息,正确则显示测试通过的信息,错误则将错误检测模块分析的错误原因或错误位置进行显示。

30、进一步的,步骤s3的具体实现方法包括如下步骤:

31、s3.1、在顶层模块中模块例化cpu模块,同时将步骤s2的测试用例存储到寄存器中作为输入,所述步骤s2得到的testbench实验方案验证信号的标准结果用来进行对比;

32、s3.2、将待检测fpga硬件设计实验接入到顶层模块中运行,在运行过程中信号抓取模块采集有效时刻的实验方案验证信号,然后数据对比模块将实验方案验证信号与实验方案验证信号的标准结果进行逐一对比,对比的计算公式为:

33、res1=(wb_pc==wb_pc_s)

34、res2=(rf_wen==rf_wen_s)

35、res3=(rf_waddr==rf_waddr_s)

36、res4=(rf_wdata==rf_wdata_s)

37、其中,wb_pc_s为指令执行时程序计数器信号标准结果,res1为指令执行时程序计数器信号对比结果,rf_wen_s为指令是否会写回信号标准结果,res2为指令是否会写回信号对比结果,rf_waddr_s为指令写回时的通用寄存器号标准结果,res3为指令写回时的通用寄存器号对比结果,rf_wdata_s为指令写回的数据信号标准结果,res4为指令写回的数据信号对比结果;

38、判断对比结果为全部相同,则信息显示模块显示通过验证,判断对比结果为不同,则错误检测模块根据实验方案验证信号的值,计算指标是否符合实验的要求,进行错误类型判断并分析待检测fpga硬件设计实验中出现错误的原因,将错误判断结果在信息显示模块显示。

39、进一步的,信息显示模块为fpga开发板的数码管。

40、本发明的有益效果:

41、本发明所述的一种用于处理器设计实验课程的fpga硬件设计验证方法,主要针对处理器设计课程实验教学中的fpga项目,对fpga硬件设计的两个主要步骤——仿真验证和板上验证进行优化,能够提升实验测试的效率,并且在设计出现错误时给出错误信息,帮助学生进行错误定位和错误原因推断。

42、本发明所述的一种用于处理器设计实验课程的fpga硬件设计验证方法,基于处理器设计课程实验教学的fpga硬件分析验证方案的使用,大大简化了硬件调试的流程,为处理器设计课程实验提供了一种全新的分析验证方式。

- 还没有人留言评论。精彩留言会获得点赞!