栅极驱动电路及显示面板的制作方法

本申请涉及显示,具体涉及一种栅极驱动电路及显示面板。

背景技术:

1、栅极驱动电路可以施加栅极驱动信号至对应的栅极线,以控制对应的晶体管进行工作。

2、然而,具有随机寻址侦测功能的栅极驱动电路在随机侦测阶段可能由于电性偏移等原因降低随机侦测的准确性。

技术实现思路

1、本申请提供一种栅极驱动电路及显示面板,以缓解随机寻址侦测的准确性较低的技术问题。

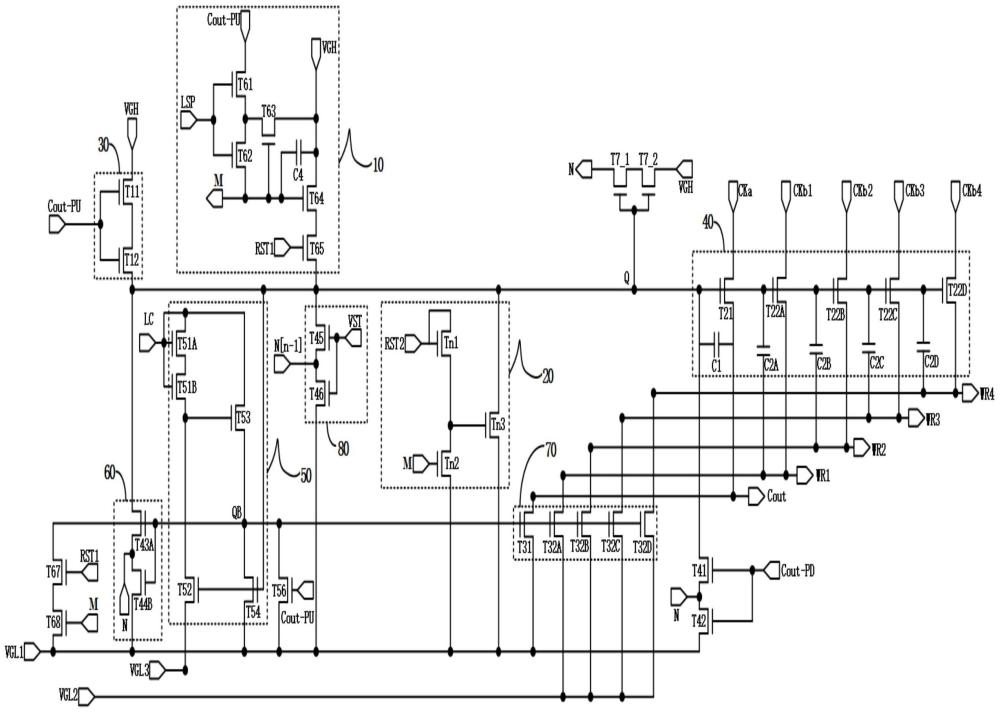

2、第一方面,本申请提供一种栅极驱动电路,该栅极驱动电路包括多个移位寄存器,每个移位寄存器包括随机寻址侦测模块和反相模块,随机寻址侦测模块与上拉节点连接,随机寻址侦测模块根据第一控制信号、上拉控制信号控制第一节点的电位,并根据第一节点的电位、第一复位信号控制上拉节点的电位;反相模块与随机寻址侦测模块、上拉节点连接,反相模块根据第二复位信号、第一节点的电位在随机侦测阶段中维持上拉节点的电位。

3、在其中一些实施方式中,反相模块包括第一晶体管、第二晶体管、以及第三晶体管,第一晶体管的第一极与第一晶体管的栅极连接并接入第二复位信号;第二晶体管的第一极与第一晶体管的第二极连接,第二晶体管的第二极与第一低电位线连接,第二晶体管的栅极与第一节点连接;第三晶体管的第一极与上拉节点连接,第三晶体管的第二极与第一低电位线连接,第三晶体管的栅极与第一晶体管的第二极连接。

4、在其中一些实施方式中,第一晶体管的沟道类型与第二晶体管的沟道类型、第三晶体管的沟道类型相同。

5、在其中一些实施方式中,第一晶体管、第二晶体管、以及第三晶体管均为n沟道型薄膜晶体管。

6、在其中一些实施方式中,随机寻址侦测模块包括第九晶体管、第十晶体管、第十一晶体管、第十二晶体管、第十三晶体管、以及第六电容,第九晶体管的第一极接入上拉控制信号,第九晶体管的栅极接入第一控制信号;第十晶体管的第一极与第九晶体管的第二极连接,第十晶体管的栅极与第九晶体管的栅极连接;第十一晶体管的栅极与第十晶体管的第二极、第一节点连接,第十一晶体管的第一极与高电位线连接;第十二晶体管的第一极与第十一晶体管的第二极连接,第十二晶体管的第二极与上拉节点连接,第十二晶体管的栅极接入第一复位信号;第十三晶体管的第一极与第九晶体管的第二极连接,第十三晶体管的第二极与高电位线连接,第十三晶体管的栅极与第十一晶体管的栅极连接;第六电容的一端与高电位线连接,第六电容的另一端与第十三晶体管的栅极连接。

7、在其中一些实施方式中,在被选中行的移位寄存器的随机侦测阶段中,所述第一控制信号处于低电位,所述第九晶体管、所述第十晶体管处于截止状态;所述第一节点的电位为高电位,所述第一复位信号处于高电位的情况下,高电位信号通过处于导通状态的所述第十一晶体管、所述第十二晶体管为所述上拉节点充电,所述上拉节点的电位随之抬升;所述第一复位信号切换为低电位,所述第十二晶体管处于截止状态;所述第一节点的电位为高电位,所述第二复位信号切换为高电位,所述第一晶体管、所述第二晶体管均处于导通状态,第一低电位信号通过所述第二晶体管将所述第三晶体管的栅极电位拉低,所述第三晶体管处于截止状态,所述上拉节点的电位维持于高电位。

8、在其中一些实施方式中,在未被选中行的移位寄存器的随机侦测阶段中,所述第一控制信号在随机侦测阶段中处于低电位,所述第九晶体管、所述第十晶体管均处于截止状态;所述第一节点的电位为低电位,所述第十一晶体管处于截止状态,所述上拉节点的电位处于低电位;所述第二复位信号切换为高电位以控制所述第一晶体管处于导通状态,所述第一节点的电位保持低电位以控制所述第二晶体管处于截止状态,所述第二复位信号的高电位通过所述第一晶体管控制所述第三晶体管均处于导通状态,所述上拉节点的电位被拉低并维持于低电位。

9、在其中一些实施方式中,移位寄存器还包括上拉控制模块和上拉模块,上拉控制模块根据上拉控制信号控制上拉节点的电位;上拉模块根据上拉节点的电位输出一级联信号和至少一栅极驱动信号。

10、在其中一些实施方式中,上拉模块包括第四晶体管、第一电容、第五晶体管、以及第二电容,第四晶体管的第一极接入第一时钟信号,第四晶体管的栅极与上拉节点连接,第四晶体管的第二极输出级联信号;第一电容的一端与第四晶体管的栅极连接,第一电容的另一端与第四晶体管的第二极连接;第五晶体管的第一极接入第二时钟信号,第五晶体管的栅极与上拉节点连接,第五晶体管的第二极输出第一栅极驱动信号;第二电容的一端与第五晶体管的第一极连接,第二电容的另一端与第五晶体管的第二极连接,第二电容的电容值小于第一电容的电容值。

11、在其中一些实施方式中,上拉模块还包括第六晶体管、第三电容、第七晶体管、第四电容、第八晶体管、以及第五电容,第六晶体管的第一极接入第三时钟信号,第六晶体管的栅极与上拉节点连接,第六晶体管的第二极输出第二栅极驱动信号;第三电容的一端与第六晶体管的第一极连接,第三电容的另一端与第六晶体管的第二极连接,第三电容的电容值小于第一电容的电容值;第七晶体管的第一极接入第四时钟信号,第七晶体管的栅极与上拉节点连接,第七晶体管的第二极输出第三栅极驱动信号;第四电容的一端与第七晶体管的第一极连接,第四电容的另一端与第七晶体管的第二极连接,第四电容的电容值小于第一电容的电容值;第八晶体管的第一极接入第五时钟信号,第八晶体管的栅极与上拉节点连接,第八晶体管的第二极输出第四栅极驱动信号;第五电容的一端与第八晶体管的第一极连接,第五电容的另一端与第八晶体管的第二极连接,第五电容的电容值小于第一电容的电容值。

12、第二方面,本申请提供一种显示面板,该显示面板包括阵列基板和上述至少一实施方式中的栅极驱动电路,栅极驱动电路集成于阵列基板。

13、本申请提供的栅极驱动电路及显示面板,通过随机寻址侦测模块提供的第一节点的电位、第二复位信号控制反相模块在随机侦测阶段中维持上拉节点的电位,可以使得与被选中行连接的移位寄存器的上拉节点维持高电位,从而确保该与被选中行连接的移位寄存器的正常工作;使得与未被选中行连接的移位寄存器的上拉节点维持低电位,从而确保该与未被选中行连接的移位寄存器停止工作,避免了与未被选中行连接的移位寄存器的异常工作,进而提高了随机寻址侦测的准确性。

技术特征:

1.一种栅极驱动电路,其特征在于,所述栅极驱动电路包括多个移位寄存器,每个所述移位寄存器包括:

2.根据权利要求1所述的栅极驱动电路,其特征在于,所述反相模块包括:

3.根据权利要求2所述的栅极驱动电路,其特征在于,所述第一晶体管的沟道类型与所述第二晶体管的沟道类型、所述第三晶体管的沟道类型相同。

4.根据权利要求2所述的栅极驱动电路,其特征在于,所述随机寻址侦测模块包括:

5.根据权利要求4所述的栅极驱动电路,其特征在于,在被选中行的移位寄存器的随机侦测阶段中,所述第一控制信号处于低电位,所述第九晶体管、所述第十晶体管处于截止状态;所述第一节点的电位为高电位,所述第一复位信号处于高电位的情况下,高电位信号通过处于导通状态的所述第十一晶体管、所述第十二晶体管为所述上拉节点充电,所述上拉节点的电位随之抬升;所述第一复位信号切换为低电位,所述第十二晶体管处于截止状态;所述第一节点的电位为高电位,所述第二复位信号切换为高电位,所述第一晶体管、所述第二晶体管均处于导通状态,第一低电位信号通过所述第二晶体管将所述第三晶体管的栅极电位拉低,所述第三晶体管处于截止状态,所述上拉节点的电位维持于高电位。

6.根据权利要求4所述的栅极驱动电路,其特征在于,在未被选中行的移位寄存器的随机侦测阶段中,所述第一控制信号在随机侦测阶段中处于低电位,所述第九晶体管、所述第十晶体管均处于截止状态;所述第一节点的电位为低电位,所述第十一晶体管处于截止状态,所述上拉节点的电位处于低电位;所述第二复位信号切换为高电位以控制所述第一晶体管处于导通状态,所述第一节点的电位保持低电位以控制所述第二晶体管处于截止状态,所述第二复位信号的高电位通过所述第一晶体管控制所述第三晶体管均处于导通状态,所述上拉节点的电位被拉低并维持于低电位。

7.根据权利要求1所述的栅极驱动电路,其特征在于,所述移位寄存器还包括:

8.根据权利要求7所述的栅极驱动电路,其特征在于,所述上拉模块包括:

9.根据权利要求8所述的栅极驱动电路,其特征在于,所述上拉模块还包括:

10.一种显示面板,其特征在于,所述显示面板包括阵列基板和如权利要求1-9任一项所述的栅极驱动电路,所述栅极驱动电路集成于所述阵列基板。

技术总结

本申请公开了一种栅极驱动电路及显示面板,该栅极驱动电路包括多个移位寄存器,每个移位寄存器包括随机寻址侦测模块和反相模块,通过随机寻址侦测模块提供的第一节点的电位、第二复位信号控制反相模块在随机侦测阶段中维持上拉节点的电位,可以使得与被选中行连接的移位寄存器的上拉节点维持高电位,从而确保该与被选中行连接的移位寄存器的正常工作;使得与未被选中行连接的移位寄存器的上拉节点维持低电位,从而确保该与未被选中行连接的移位寄存器停止工作,避免了与未被选中行连接的移位寄存器的异常工作,进而提高了随机寻址侦测的准确性。

技术研发人员:周翔,韩佰祥,李广耀

受保护的技术使用者:深圳市华星光电半导体显示技术有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!