驱动电路和显示装置的制作方法

本发明涉及显示,尤其涉及一种驱动电路和显示装置。

背景技术:

1、oled(有机发光二极管)显示的应用范围已经逐渐从中小尺寸的手表/手机/平板等领域扩展到pc(个人计算机)/monitor(监视器)等领域。为了达成更好的显示效果(降低拖影效果,提高屏幕的响应速度),panel(面板)的刷新率逐渐增加。但是逐渐增加的刷新率也提高了整机gpu(图形处理器)和panel ic(集成电路)的功耗。但是在具体的使用场景下,通常只有部分位置的画面在变化(视频播放、游戏窗口等),其余位置的画面通常是静态不需要高刷新率的(评论区、广告等)。

2、在相关技术中,常用可调脉宽的驱动电路由于其电路特性(输出端无自举结构),因此输出波形下降沿存在台阶,导致输出不稳定、漏电等问题。相关的可调脉宽的驱动电路随着pmos(p型金属-氧化物-半导体)tft(薄膜晶体管)偏负,台阶电压将提高。作为可控制局域刷新的驱动模组,下降沿台阶输入反相器后引发逻辑混乱,导致最终输出宽度增加,产生各种横纹类显示问题。

技术实现思路

1、本发明的主要目的在于提供一种驱动电路和显示装置,解决现有技术中可调脉宽的驱动电路的输出波形下降沿存在台阶,导致输出不稳定、漏电等问题。

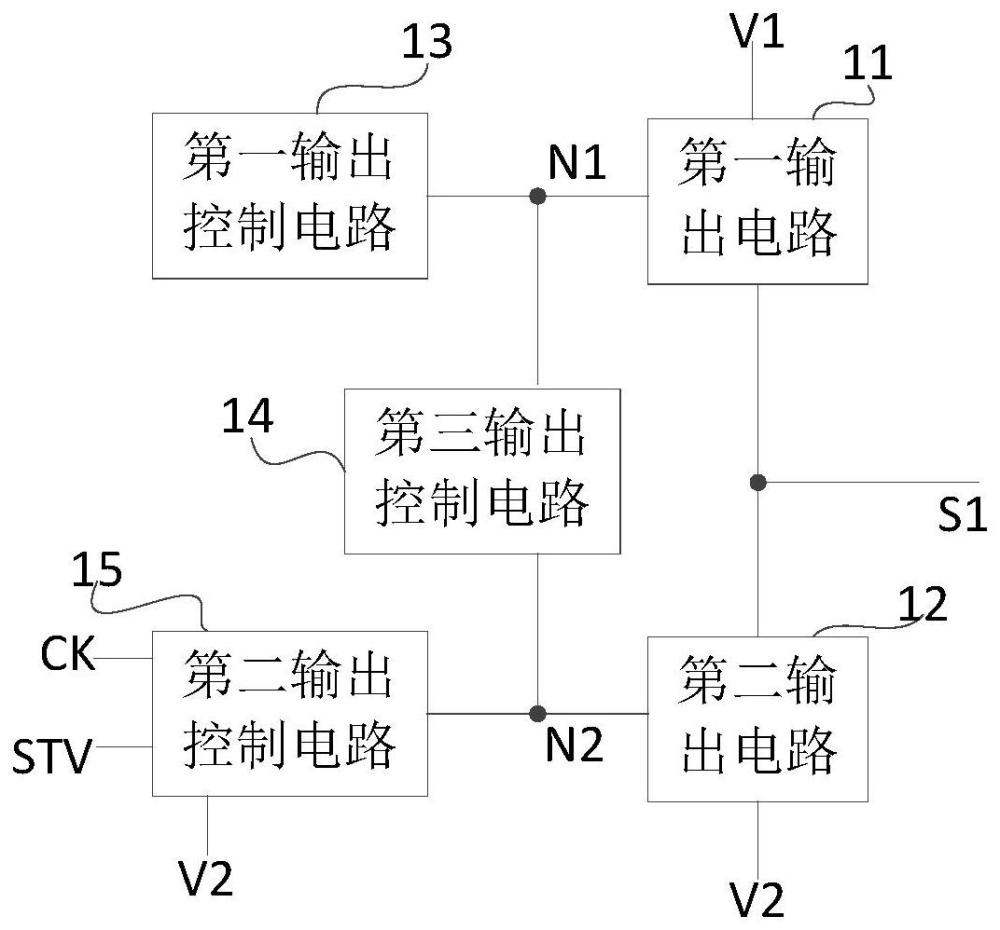

2、在一个方面中,本发明实施例提供一种驱动电路,包括第一输出电路、第二输出电路、第一输出控制电路、第二输出控制电路和第三输出控制电路;

3、所述第一输出电路分别与第一节点、第一电压端和驱动输出端电连接,用于在所述第一节点的电位的控制下,控制所述驱动输出端与所述第一电压端之间连通;

4、所述第二输出电路分别与第二节点、所述驱动输出端和第二电压端电连接,用于在所述第二节点的电位的控制下,控制所述驱动输出端与所述第二电压端之间连通;

5、所述第一输出控制电路与所述第一节点电连接,用于控制所述第一节点的电位;

6、所述第二输出控制电路分别与第一时钟信号端、输入端、第二电压端和所述第二节点电连接,用于在所述第一时钟信号端提供的第一时钟信号和所述输入端提供的输入信号的控制下,控制所述第二节点与所述第二电压端之间连通;

7、所述第三输出控制电路分别与所述第一节点和所述第二节点电连接,用于在所述第一节点的电位的控制下,控制所述第二节点的电位。

8、可选的,所述第二输出电路包括的晶体管,以及,所述第二输出控制电路包括的晶体管都为n型晶体管。

9、可选的,所述第二输出电路包括第一晶体管;

10、所述第一晶体管的栅极与所述第二节点电连接,所述第一晶体管的第一极与所述驱动输出端电连接,所述第一晶体管的第二极与所述第二电压端电连接;

11、所述第一晶体管为n型晶体管。

12、可选的,所述第三输出控制电路还分别与所述第一时钟信号端、所述输入端和第三节点电连接,用于在所述第一时钟信号的控制下,控制所述第三节点与所述输入端之间连通,在所述第三节点的电位的控制下,控制所述第一节点与所述第二节点之间连通。

13、可选的,所述第二输出控制电路包括第二晶体管和第三晶体管;

14、所述第二晶体管的栅极与所述第一时钟信号端电连接,所述第二晶体管的第一极与所述第二电压端电连接,所述第二晶体管的第二极与所述第三晶体管的第一极电连接;

15、所述第三晶体管的栅极与所述输入端电连接,所述第三晶体管的第二极与所述第二节点电连接。

16、可选的,所述第二晶体管和所述第三晶体管为n型晶体管。

17、可选的,所述第三输出控制电路包括第四晶体管和第五晶体管;

18、所述第四晶体管的栅极与所述第一时钟信号端电连接,所述第四晶体管的第一极与所述输入端电连接,所述第四晶体管的第二极与所述第三节点电连接;

19、所述第五晶体管的栅极与所述第三节点电连接,所述第五晶体管的第一极与所述第一节点电连接,所述第五晶体管的第二极与所述第二节点电连接。

20、可选的,所述第一输出控制电路分别与所述第一时钟信号端、第四节点、第五节点、第六节点、第一电压端、第二电压端、第二时钟信号端和所述第三节点电连接,用于在所述第一时钟信号的控制下,控制所述第二电压端与所述第五节点之间连通,在所述第三节点的电位的控制下,控制所述第五节点与所述第一时钟信号端之间连通,在所述第四节点的电位的控制下,控制第六节点与所述第二时钟信号端之间连通,在所述第二时钟信号端提供的第二时钟信号的控制下,控制所述第一节点与所述第六节点之间连通,在所述第三节点的电位的控制下,控制所述第一节点与所述第一电压端之间连通,并维持所述第一节点的电位。

21、可选的,所述第四节点直接与所述第五节点电连接;或者,

22、所述第一输出控制电路还用于在第二电压端提供的第二电压信号的控制下,控制所述第四节点与所述第五节点之间连通。

23、可选的,所述第一输出控制电路包括第六晶体管、第七晶体管、第八晶体管、第九晶体管、第十晶体管、第一电容和第二电容;

24、所述第六晶体管的栅极与所述第一时钟信号端电连接,所述第六晶体管的第一极与所述第二电压端电连接,所述第六晶体管的第二极与所述第五节点电连接;

25、所述第七晶体管的栅极与所述第三节点电连接,所述第七晶体管的第一极与所述第一时钟信号端电连接,所述第七晶体管的第二极与所述第五节点电连接;

26、所述第八晶体管的栅极与所述第四节点电连接,所述第八晶体管的第一极与所述第二时钟信号端电连接,所述第八晶体管的第二极与所述第六节点电连接;

27、所述第九晶体管的栅极与所述第二时钟信号端电连接,所述第九晶体管的第一极与所述第六节点电连接,所述第九晶体管的第二极与所述第一节点电连接;

28、所述第十晶体管的栅极与所述第三节点电连接,所述第十晶体管的第一极与所述第一电压端电连接,所述第十晶体管的第二极与所述第一节点电连接;

29、所述第一电容的第一端与所述第一节点电连接,所述第一电容的第二端与直流电压端电连接;

30、所述第二电容的第一端与所述第四节点电连接,所述第二电容的第二端与所述第六节点电连接。

31、可选的,所述第一输出控制电路还包括第十一晶体管;

32、所述第十一晶体管的栅极与所述第二电压端电连接,所述第十一晶体管的第一极与所述第五节点电连接,所述第十一晶体管的第二极与所述第四节点电连接。

33、可选的,所述第一输出电路包括第十二晶体管;

34、所述第十二晶体管的栅极与所述第一节点电连接,所述第十二晶体管的第一极与所述第一电压端电连接,所述第十二晶体管的第二极与所述驱动输出端电连接。

35、在第二个方面中,本发明实施例提供一种显示装置,包括上述的驱动电路。

36、本发明实施例将所述第二输出电路包括的晶体管和所述第二输出控制电路包括的晶体管设置为都为n型晶体管,通过控制所述第二节点的电位的时序,实现所述驱动输出端输出的驱动信号的输出波形的下降沿无台阶,改善所述输出波形的稳定性和整体漏电,同时改善驱动电路在tft(薄膜晶体管)特性发生漂移的条件下的输出波形稳定性。

- 还没有人留言评论。精彩留言会获得点赞!