改进的光刻方法与流程

1.本技术涉及半导体制造技术领域,具体涉及一种改进的光刻方法。

背景技术:

2.随着集成电路技术的不断缩微,目前主流的集成电路已经进入20nm甚至更小的阶段,用于20nm以下产品的光掩模板是通过非常严格的关键工艺生产得到,而在掩模板生产中发现光掩模板上的图形放置误差(ipe,image placement error)会转移到晶圆上,并且掩模板上的各种光刻标记的放置误差也会转移到晶圆上。

3.然而,目前在使用掩模板进行光刻工艺时,对于整个工艺流程中的校准过程,并没有考虑光刻标记的放置误差,而如果掩模板上的这些光刻标记存在放置误差时,可能会造成不必要的校准更正,进而降低了校准的准确性。

技术实现要素:

4.本技术的目的是针对上述现有技术的不足提出的一种改进的光刻方法,该目的是通过以下技术方案实现的。

5.本技术的第一方面提出了一种改进的光刻方法,所述方法包括:

6.提供一光掩模板;

7.测量所述光掩模板上光刻标记的放置误差;

8.根据所述放置误差执行光刻工艺的校准流程。

9.本技术的第二方面提出了一种电子设备,包括根据上述第一方面所述的改进的光刻方法制备的半导体器件。

10.在本技术实施例中,通过测量光刻标记在光掩模板上的放置误差,并将放置误差应用到后续使用光掩模板的光刻工艺流程中的校准流程,以提高光刻工艺流程中的校准准确性。

附图说明

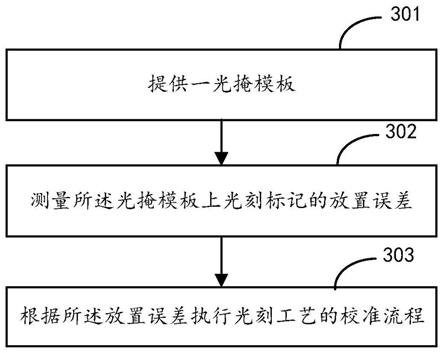

11.此处所说明的附图用来提供对本技术的进一步理解,构成本技术的一部分,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

12.图1为本技术示出的一种相关技术中掩模板的制造工艺流程构流程示意图;

13.图2为本技术示出的一种相关技术中的光刻工艺流程示意图;

14.图3为本技术根据一示例性实施例示出的一种改进的光刻方法的实施例流程图;

15.图4为本技术根据图3所示实施例示出的一种掩模板的制造工艺流程示意图;

16.图5为本技术根据图3所示实施例示出的一种光刻工艺流程示意图。

具体实施方式

17.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性

的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

18.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

19.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

20.目前,用于20nm以下产品的光刻掩模(photo mask)是通过非常严格的关键工艺生产的,但光刻掩模上的图形放置误差会转移到晶圆上,而且有时会因工艺条件放大图形放置误差,因此在制作光刻掩模时会以最大程度的减少图形放置误差。

21.发明人发现,在制作光刻掩模过程中,既然光刻掩模上的电路图形存在图形放置误差,那么光刻掩模上的光刻标记同样也存在放置误差。

22.在现有技术中,通过晶圆对准流程来校准晶圆的对准误差,并通过套刻对准流程来校准图层的套刻误差。但是,当存在标记放置误差时,对于晶圆对准流程和套刻对准流程可能会进行不必要的校准更正,从而降低了校准的准确性。

23.参见图1所示,为现有技术中掩模板的制造工艺,工艺步骤包括:

24.1、提供一个掩模板(mask plate);

25.2、在掩模板上涂覆一层光刻胶;

26.3、使用ebeam光刻机进行曝光(ebeam exposure);

27.4、显影(develop)、烘干(dry)及剥离(strip);

28.5、特征尺寸的均匀性检测(cd uniformity check);

29.6、电路图形的图形放置误差(ipe,image placement error)检测;

30.7、条宽偏差(cd mtt,mean to target)检测;

31.8、各种缺陷的检测。

32.参见图2所示,为使用上述图1所示的光刻掩模制造工艺制备的光刻掩模进行的光刻工艺流程,步骤包括:

33.1、晶圆加载(wafer loading);

34.2、晶圆对准(wafer alignment);

35.3、测量并更正(measurement&correction);

36.4、曝光;

37.5、旋转烘焙并显影(spinner bake/develop);

38.6、套刻精度测量(overlay measurement)。

39.由上述描述可知,在使用掩模板进行光刻工艺时,对于整个工艺流程中的校准过程,并没有考虑光刻标记的放置误差,而如果掩模板上存在标记放置误差时,可能会造成不必要的校准更正,进而降低了校准的准确性。

40.为解决上述技术问题,本技术提出一种改进的光刻方法,通过测量主要光刻标记在光掩模板上的放置误差,并将放置误差应用到后续使用光掩模板的光刻工艺流程中的校准流程,以提高光刻工艺流程中的校准准确性。

41.下面以具体实施例对本技术提出的改进的光刻方案进行详细阐述。

42.图3为本技术根据一示例性实施例示出的一种改进的光刻方法的实施例流程图,如图3所示,所述改进的光刻方法包括如下步骤:

43.步骤301:提供一光掩模板。

44.其中,所述光掩模板为包含电路图形结构和光刻标记的光掩模板。

45.在本技术中,光刻标记(也称为配准标记)可以是对准标记(alginment mark),或者也可以是套刻标记(overlay mark)。

46.需要说明的是,本技术中涉及的光刻标记位于划片槽(scribe lane)中。

47.步骤302:测量所述光掩模板上光刻标记的放置误差。

48.其中,通常在光掩模板上有至少几十个对准标记和套刻标记,每个标记的位置对晶圆对准和套刻校正起着非常重要的作用,因此需要测量每个标记的放置误差。

49.示例性的,可以使用测量工具测量光掩模板上每个光刻标记的放置误差。

50.参见图4所示的掩模板制造工艺流程,工艺步骤包括:

51.1、提供一个掩模板;

52.2、在掩模板上涂覆一层光刻胶;

53.3、使用ebeam光刻机进行曝光;

54.4、显影、烘干及剥离;

55.5、特征尺寸的均匀性检测;

56.6、电路图形的图形放置误差检测;

57.7、条宽偏差检测;

58.8、各种缺陷的检测。

59.9、测量光刻标记的图形放置误差。

60.将图4所示的掩模板制造工艺流程与上述图1所示的掩模板制造工艺流程对比,本技术增加了光刻标记在掩模板上的放置误差的测量步骤。

61.步骤303:根据所述放置误差执行光刻工艺的校准流程。

62.在本实施例中,所述光刻工艺的校准流程包括晶圆校准流程和套刻校准流程。

63.基于此,对于晶圆校准流程,为根据对准标记的放置误差执行光刻工艺的晶圆校准流程;对于套刻校准流程,为根据套刻标记的放置误差执行光刻工艺的套刻校准流程。

64.以晶圆校准流程为例,参见图5所示,为应用上述图4所示的光刻掩模制造工艺制备的光刻掩模进行的光刻工艺流程,步骤包括:

65.1、晶圆加载;

66.2、根据对准标记的放置误差进行晶圆对准;

67.3、测量并更正;

68.4、曝光;

69.5、旋转烘焙并显影;

70.6、套刻精度测量。

71.将图5所示的光刻工艺流程与上述图2所示的光刻工艺流程对比,本技术将对准标记的放置误差应用到晶圆校准流程中了。

72.在一实施例中,所述校准流程的校准过程可以是根据放置误差和光刻标记的预期位置获得光刻标记的实际位置,进而根据所述光刻标记的实际位置执行光刻工艺的校准流程。

73.以光掩模板上的对准标记(reticle keys)为例,如表1所示,光掩模板上包含5个对准标记:key1~key5,key1在光掩模板上的预期位置的坐标为(32132.1,32145.1),key2在光掩模板上的预期位置的坐标为(45678.1,54321.1),key3在光掩模板上的预期位置的坐标为(12345.1,98765.1),key4在光掩模板上的预期位置的坐标为(23456.1,67845.1),key5在光掩模板上的预期位置的坐标为(12567.1,45678.1);在制造光掩模板后,测量得到key1的放置误差为(0.1,-0.1),key2的放置误差为(0.3,-0.1),key3的放置误差为(0.3,0.2),key4的放置误差为(0.1,0.1),key5的放置误差为(0.1,0.3)。从而得到key1在光掩模板上的实际位置的坐标为(32132.2,32145.0),key2在光掩模板上的实际位置的坐标为(45678.4,54321.0),key3在光掩模板上的实际位置的坐标为(12345.4,98765.3),key4在光掩模板上的实际位置的坐标为(23456.2,67845.2),key5在光掩模板上的实际位置的坐标为(12567.2,45678.4)。

74.掩模标记xyerror xerror ynew xnew ykey132132.132145.10.1-0.132132.232145.0key245678.154321.10.3-0.145678.454321.0key312345.198765.10.30.212345.498765.3key423456.167845.10.10.123456.267845.2key512567.145678.10.10.312567.245678.4

75.表1

76.由上述描述可知,输入到光刻机作业文件中的光刻标记的坐标位置相对于预期坐标位置存在放置误差,而如果不测量标记的放置误差,直接输入光刻标记的预设坐标位置,必然会降低校准的准确性。

77.下面以不同的实验示例来说明使用与不使用光掩模板上的标记放置误差的结果差异:

78.第一个例子,应用/未应用标记放置误差对晶圆对准结果的影响对比,如表2所示,光掩模板上的对准标记key1~key5的放置误差分别为:-0.009、0.003、0.005、0.01、0.007,group1对应的数据为应用标记放置误差的对准标记位置数据,晶圆对准结果存在偏差,需要对对准结果进行校正,group2对应的数据为未应用标记放置误差的对准标记位置数据,晶圆对准结果无偏差,不需要对对准结果进行校正。也就是说,group1的对准结果更准确。

[0079][0080]

表2

[0081]

第二个例子,对准标记和放置误差反应/未反应状态的坐标对比,表3中的第三列表示光刻机曝光时有没有进行位置修正,group1对应的坐标指的是利用放置误差对对准标记的相对坐标进行了校正,第三列表示对准标记在掩模板上有偏差,光刻机在曝光时未进行校正;group2对应的坐标指的是未利用放置误差对对准标记的相对坐标进行校正,第三列表示对准标记在掩模板上无偏差,光刻机在曝光时进行校正。

[0082] 相对坐标x相对坐标y误差group112345.000112345.0005误差保留group21234512345误差修正

[0083]

表3

[0084]

第三个例子,套刻标记的放置误差反应/未反应状态的坐标示例,表4中的group1对应的套刻精度量测的x方向和y方向的偏差值未应用放置误差值,光刻机未对套刻标记位置的偏移作出反应,group2对应的套刻精度量测的x方向和y方向的偏差值应用放置误差值,光刻机对套刻标记位置的偏移作出了反应。

[0085] x偏差值y偏差值y区分group1-0.01nm0.02nm误差未反应group200误差反应

[0086]

表4

[0087]

至此,完成图3所示的光刻流程,通过上述图3所示的光刻流程,由于将光刻标记在掩模上的放置误差应用到光刻的校准流程中,因此可以避免标记的放置误差的影响,进而提高了光刻工艺中的校准流程的准确性。

[0088]

与前述改进的光刻方法的实施例相对应,本技术还提供了一种电子设备,所述电子设备包括根据上述图3所述的改进的光刻方法制备的半导体器件。

[0089]

在一些实施例中,所述电子设备可以包括智能电话、计算机、平板电脑、可穿戴智

能设备、人工智能设备、移动电源。

[0090]

在以上的描述中,对于各层的构图、刻蚀等技术细节并没有做出详细的说明。但是本领域技术人员应当理解,可以通过各种技术手段,来形成所需形状的层、区域等。另外,为了形成同一结构,本领域技术人员还可以设计出与以上描述的方法并不完全相同的方法。另外,尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。

[0091]

以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1