封装及半导体器件及其形成方法与流程

1.本发明的实施例是有关于封装及半导体器件及其形成方法。

背景技术:

2.光子集成电路(photonic integrated circuit,pic)(例如高性能服务器)利用光子及电子元件来实施关于数据处理及计算的各种功能。而电子元件可包括中央处理器(central processing unit,cpu)、图形处理单元(graphics processing unit,gpu)、输入/输出缓冲器等;光子元件可包括波导、光放大器、调制器、光电二极管、及用于产生、发射、传输、调制、信号处理、放大、和/或检测光的其他元件。在pic中,包括光子元件的光子管芯通常通过包括电子元件的电子管芯而驱动。

3.在现有的pic中,光子管芯及电子管芯被集成在例如印刷电路板(printed circuit board,pcb)等板上。因此,电子管芯中的计算或处理元件必需通过电路板上的导线及器件以与光子管芯通信;且没有通过电子管芯驱动光子管芯中的调制器的直接机制。这导致在pic中用于信号处理和通信的集成面积更大、延迟更高、功耗更高、且带宽更低。

技术实现要素:

4.本发明实施例的一种封装包括封装衬底、第一层及第二层。第一层包括位于所述封装衬底上的电子管芯。第二层包括光子管芯,其中所述第二层结合到所述第一层上,使得所述光子管芯结合到所述电子管芯上。

5.本发明实施例的一种半导体器件包括衬底、第一层以及第二层。第一层包括位于所述衬底上的多个电子管芯。第二层包括位于所述第一层上的多个光子管芯,其中所述多个光子管芯中的每一者位于所述多个电子管芯中的相应一者上且与所述多个电子管芯中的所述相应一者接触。

6.本发明实施例的一种用于形成半导体器件的方法,包括:形成包括电子管芯的第一层;形成包括光子管芯的第二层,其中所述电子管芯包括至少一个用于所述光子管芯的驱动器;将所述第二层结合到所述第一层上以产生结合堆叠,其中所述光子管芯结合到所述电子管芯上;使用导电凸块将所述结合堆叠机械贴合且电贴合到封装衬底上,其中所述第一层利用所述导电凸块贴合到所述封装衬底。

附图说明

7.结合附图阅读以下详细说明,会最好地理解本公开的各个方面。应注意,各种特征未必按比例绘制。事实上,为使说明清晰起见,可任意增大或减小各种特征的尺寸及几何形状。

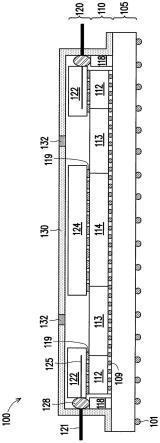

8.图1a示出根据本公开一些实施例的示例性集成电路(integrated circuit,ic)封装的剖视图。

9.图1b示出根据本公开一些实施例的示例性ic封装的俯视图。

10.图2a示出根据本公开一些实施例的关于光子或电子元件的管芯选择的示例性决策标准。

11.图2b示出根据本公开一些实施例的关于光子或电子元件的管芯选择的另一示例性决策标准。

12.图2c示出根据本公开一些实施例的关于光子或电子元件的管芯选择的又一示例性决策标准。

13.图3a到图3l示出根据本公开一些实施例的在制造工艺的各种阶段的示例性ic封装的剖视图。

14.图4示出根据本公开一些实施例的用于光子及电子元件的封装集成的示例性方法。

15.图5a示出根据本公开一些实施例的另一示例性集成电路(ic)封装的剖视图。

16.图5b示出根据本公开一些实施例的另一示例性ic封装的俯视图。

17.图6a到图6l示出根据本公开一些实施例的在制造工艺的各种阶段的另一示例性ic封装的剖视图。

18.图7示出根据本公开一些实施例的用于光子及电子元件的封装集成的另一示例性方法。

具体实施方式

19.以下公开内容描述了用于实施主题的不同特征的各种示例性实施例。以下阐述组件和配置的具体实例以简化本公开。当然,这些仅仅是实例,而不旨在进行限制。举例来说,应理解,当一个元件被称为“连接到”或“耦合到”另一个元件时,所述元件可直接连接到或耦合到所述另一个元件,或可存在一个或多个中间元件。

20.本教示内容公开了使用异构三维(three-dimensional,3d)封装解决方案的高性能计算(high performance computing,hpc)处理器、光子管芯、及电子管芯的集成。具有先进工艺节点的计算管芯及光子管芯位于组合件顶部上的顶层中。底层包括例如输入/输出(input/output,i/o)缓冲器、存储器控制器、快速外围组件内连(peripheral component interconnect express,pcie)控制器及其他芯片组功能节点等成熟节点。具有模拟功能的一个或多个电子管芯也位于底层中,用作光子管芯的接口和/或驱动器。这使得计算管芯与光子管芯在封装内非常接近。

21.所公开的方法及封装可应用于任何具有3d芯片组集成及高带宽数据传输的应用。举例来说,所公开的集成可很好地应用于具有高带宽数据传输需求的下一代服务器。光子管芯与计算管芯的紧密集成使得能够实现低功率消耗及高传输带宽,例如用于通过光纤连接的服务器之间的数据传输。

22.在一个实施例中,封装通过直接混合结合(direct hybrid bonding)来集成异构处理器元件及光子元件。所述处理器元件可包括例如中央处理器(cpu)、图形处理单元(gpu)、现场可编程门阵列(field programmable gate array,fpga)、机器学习引擎等。所述光子元件可包括调制器、光电二极管、波导、光放大器等。光子管芯和具有先进节点的计算元件位于异构堆叠的顶层上;具有模拟和芯片组功能及成熟工艺节点的电子管芯(或光子接口管芯)位于异构堆叠的底层上。顶层和底层的直接混合结合使得能够实现面对面堆

叠,这使得在处理器元件与光子元件之间具有高带宽通信,且使得能够在管芯之间实现简单低功率信号传递。此外,在先进节点与成熟节点之间分割计算及芯片组/模拟功能可节省ic封装的成本。

23.图1a示出根据本公开一些实施例的示例性集成电路(ic)封装100的剖视图。应注意,封装100仅仅是实例,且并不旨在限制本公开。因此,应理解,可在图1a的封装100中设置附加的功能块或将附加的功能块耦合到图1a的封装100,且一些其他的功能块在本文中可仅作简要描述。

24.参考图1a,封装100包括封装衬底105、位于封装衬底105上的第一层110、及结合到第一层110上的第二层120。第一层110包括一个或多个电子管芯112;且第二层120包括一个或多个光子管芯122。如图1a所示,在第二层120结合到第一层110上的情况下,使用混合结合(hybrid bonds)119将光子管芯122结合到相应的电子管芯112上。直接结合可引起小于10微米的超细间距。也就是说,电子管芯112与相应的光子管芯122之间的间距或垂直距离可小于10微米。电子管芯112可包括用于相应光子管芯122的驱动器,这意味着电子管芯112可将信号发送到光子管芯122中用于计算及处理。

25.如图1a所示,第一层110还包括底部管芯114,所述底部管芯114通过通孔113(例如硅穿孔(through silicon via,tsv))与每一相邻的电子管芯112分隔开。tsv 113可包括垂直地延伸穿过第一层110且在第二层120与封装衬底105之间提供电连接的导电路径。

26.第二层120还包括使用混合结合119结合到底部管芯114上的顶部管芯124。在一个实施例中,在结合之后底部管芯114与顶部管芯124之间的间距可小于10微米。如图1a所示,在第二层120中,顶部管芯124与相邻的光子管芯122分隔开。在一个实施例中,顶部管芯124可为具有比光子管芯122更高的操作频率的计算或处理器管芯。

27.在一个实施例中,底部管芯114及电子管芯112在成熟节点中制造,且含有包括用于光子管芯122的驱动器的模拟及芯片组功能。在通过3d混合结合使电子管芯112与位于顶部的光子管芯122面对面地堆叠时,可在封装阶段的较早阶段对每一底部管芯114和/或电子管芯112进行测试,以选出已知良好的管芯(known good dies)。

28.如图1a所示,第一层110利用凸块109(例如使用倒装式芯片(c4)内连方法)贴合到封装衬底105。封装衬底105可利用封装凸块101进一步耦合到印刷电路板(pcb)。在一个实施例中,tsv 113可包括导电路径,所述导电路径垂直地延伸以在第二层120中的顶部管芯124与封装衬底105上的凸块109之间提供电连接。

29.如图1a所示,封装100还包括在第一层110中与每一电子管芯112相邻的底座118。底座118形成在封装衬底105上。封装100还包括沉积在每一底座118上的聚合物透镜128。每一聚合物透镜128与第二层120中的相应光子管芯122对准,且被配置成引导光进出光子管芯122。

30.如图1a所示,封装100还包括光纤121,光纤121与每一聚合物透镜128对准且贴合到每一聚合物透镜128,以通过可位于聚合物透镜128内的边缘耦合器或光栅耦合器引导光进出聚合物透镜128。聚合物透镜128设置在一位置处以耦合光纤121与光子管芯122之间的光传输。在一个实施例中,边缘耦合器或光栅耦合器位于光纤121与聚合物透镜128之间。在另一实施例中,边缘耦合器或光栅耦合器位于聚合物透镜128与光子管芯122之间。在另一实施例中,一个边缘耦合器或光栅耦合器位于光纤121与聚合物透镜128之间;且另一边缘

耦合器或光栅耦合器位于聚合物透镜128与光子管芯122之间。

31.如图1a所示,封装100还包括形成在第二层120上且与第二层120接触的散热器130。散热器130包括多个热隔断132,所述多个热隔断132中的每一者位于顶部管芯124与和顶部管芯124相邻的光子管芯122之间。绝缘的热隔断132可避免或减少顶部管芯124与相邻光子管芯122之间的热传递。根据各种实施例,散热器130可由例如铜、银、铝等导热材料制成;而热隔断132可由例如多孔膜、蜡膜、管芯贴合膜(die attach film,daf)、气凝胶、胶带、焊料膏、粘合剂和/或热脂等热绝缘材料制成。

32.图1b示出根据本公开一些实施例的示例性ic封装100的俯视图。图1a中封装100的剖视图是沿图1b所示的a-a’方向截取的。如图1b所示,封装100包括多个透镜阵列,所述多个透镜阵列中的每一者包括多个透镜128且与第二层或顶层中的相应光子管芯122对准。封装100包括多个光纤阵列,所述多个光纤阵列中的每一者包括多个贴合到相应透镜阵列的光纤121。每一光纤121可为单模光纤或多模光纤。如图1b所示,透镜128的数量与光纤121的数量相同,使得每一光纤与相应的透镜128对准且贴合到相应的透镜128,所述相应的透镜128被配置成引导相应的光子管芯122与相应的光纤121之间的光传输。

33.在操作期间,从贴合在光纤阵列一端上的远程服务器接收的光信号可通过透镜阵列耦合到位于光子管芯122上的相应光电探测器。作为另外一种选择,从光子管芯122中的光源管芯或光源接收的光信号可通过透镜阵列耦合到光纤阵列,所述光信号可进一步传输到远程服务器。

34.在一些实施例中,每一光子管芯122可包括例如激光驱动器、数字控制电路、光电探测器、波导、小型可插拔(small form-factor pluggable,sfp)收发器、高速相位调制器(high-speed phase modulator,hspm)、校准电路、分布式马赫曾德尔干涉仪(mach-zehnder interferometer,mzi)、光栅耦合器、光源(即,激光)等组件(未示出)。光栅耦合器使得能够在光纤阵列与光子管芯122上的相应光电探测器之间实现光信号的耦合。每一光栅耦合器可包括多个光栅及波导,所述多个光栅及波导具有用来减小折射率对比度以减小背面反射损耗的设计。

35.在一些实施例中,每一电子管芯112可包括电路(未示出),所述电路包括放大器、控制电路、数字处理电路、提供封装100所需的电子功能的至少一个电子电路、及用于控制相应的光子管芯122中的元件的驱动器电路。

36.在一些实施例中,顶部管芯124可包括组件(未示出),例如cpu、gpu、人工智能(artificial intelligence,ai)处理器、机器学习(machine learning,ml)处理器、高带宽存储器(high bandwidth memory,hbm)、高速缓冲存储器和/或具有高操作频率的其他组件。在一些实施例中,底部管芯114可包括例如i/o缓冲器、芯片组、存储器控制器、驱动器电路、和/或具有低操作频率的其它组件等组件(未示出)。在电路设计期间,每一组件可依据不同的标准放入封装的顶部管芯或底部管芯中。在各种实施例中,与底部管芯中的组件相比,顶部管芯中的每一组件具有以下中的至少一者:更高的操作频率、更高的时钟频率、更好的电路区缩放能力(这意味着在未来的技术时代中更容易缩减或减小电路面积和管芯面积)、或更高的存储速度。因此,封装100通过3d混合结合将异构类型的光子或电子元件集成。

37.图2a示出根据本公开一些实施例的关于光子或电子元件的管芯选择的示例性决

策标准。如图2a所示,在步骤211处将元件的操作频率与频率阈值f_th进行比较。当操作频率大于频率阈值f_th时,将元件放入顶部管芯中。否则,当操作频率不大于频率阈值f_th时,将元件放入底部管芯中。根据各种实施例,频率阈值f_th可在2ghz与4ghz之间进行选择。

38.图2b示出根据本公开一些实施例的关于光子或电子元件的管芯选择的另一示例性决策标准。如图2b所示,在步骤221处将元件的缩放能力与缩放阈值s_th进行比较。当缩放能力大于缩放阈值s_th时,将元件放入顶部管芯中。否则,当缩放能力不大于缩放阈值s_th时,将元件放入底部管芯中。在一个实施例中,如果元件从一代缩放到另一代,便将元件放入顶部管芯中;否则,将元件放入底部管芯中。

39.图2c示出根据本公开一些实施例的关于光子或电子元件的管芯选择的又一示例性决策标准。如图2c所示,在步骤231处将元件的存储速度与阈值m_th进行比较。当存储速度大于阈值m_th时,将元件放入顶部管芯中。否则,当存储速度不大于阈值m_th时,将元件放入底部管芯中。在各种实施例中,阈值m_th为2ghz。

40.图3a到图3l示出根据本公开一些实施例的在制造工艺的各种阶段的示例性ic封装的剖视图。图3a是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-1的剖视图,所述封装300-1包括第一衬底302及设置在第一衬底302上的第一层310。第一层310可由硅或另一半导体材料形成。

41.图3b是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-2的剖视图,所述封装300-2包括在第一衬底302上的第一层310中形成的底部管芯314及两个电子管芯312。根据各种实施例,虽然在图3b中示出了一个底部管芯和两个电子管芯,但在第一层310中也可形成其他数量的底部管芯和/或电子管芯。如图3b所示,底部管芯314通过通孔313与每一相邻的电子管芯312分隔开。底部管芯314及电子管芯312中的每一者可通过以下方式形成:基于光刻法从光掩模向第一层310界定几何图案;基于所述几何图案刻蚀第一层310以确定第一层310中的刻蚀区域;在所述刻蚀区域中外延生长一种或多种半导体材料以形成底部管芯或电子管芯;及执行化学机械抛光(chemical mechanical polishing,cmp)以使第一层310的表面平滑。通孔313中的每一者可通过湿法或干法刻蚀过程形成。第一层310可包括具有芯片组和光子接口功能的元件。在一个实施例中,所有电子管芯312、底部管芯314及通孔313通过以下方式一起形成:基于光刻法从光掩模界定几何图案;基于所述几何图案刻蚀第一层310以确定第一层310中的刻蚀区域;在刻蚀区域中外延生长一种或多种半导体材料以形成电子管芯312、底部管芯314及通孔313。

42.图3c是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-3的剖视图,所述封装300-3包括第二衬底303及设置在第二衬底303上的第二层320。第二层320可由硅或另一半导体材料形成。

43.图3d是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-4的剖视图,所述封装300-4包括形成在第二衬底303上的第二层320中的顶部管芯324及两个光子管芯322。根据各种实施例,虽然在图3d中示出了一个顶部管芯和两个光子管芯,但在第二层320中也可形成其他数量的顶部管芯和/或光子管芯。顶部管芯324及光子管芯322中的每一者可通过以下方式形成:基于光刻法从光掩模向第二层320界定几何图案;基于所述几何图案刻蚀第二层320以确定第二层320中的刻蚀区域;在刻蚀区域中外延生长一种或多种

半导体材料以形成顶部管芯或光子管芯;及执行化学机械抛光(cmp)以使第二层320的表面平滑。第二层320可包括具有处理器及光子功能(photonic functionalities)的元件。在一个实施例中,包括光子管芯322及顶部管芯324的所有元件通过以下方式一起形成:基于光刻法从光掩模界定几何图案;基于所述几何图案刻蚀第二层320以确定第二层320中的刻蚀区域;在刻蚀区域中外延生长一种或多种半导体材料以形成光子管芯322及顶部管芯324。在一个实施例中,可在第二层320中的光子管芯322与顶部管芯324之间的间隙中嵌置一些热绝缘材料。

44.图3e是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-5的剖视图,所述封装300-5包括面对面堆叠在第一层310上的第二层320。如图3e所示,将第二层翻转且通过混合结合319结合到第一层。在混合结合之后,顶部管芯324结合到底部管芯314上且与底部管芯314接触;且每一光子管芯322结合到相应的电子管芯312上并与所述相应的电子管芯312接触,所述相应的电子管芯312可包括用于控制光子管芯322中的元件的驱动器电路。

45.图3f是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-6的剖视图,其中在结合之后,移除第二衬底303及第一衬底302。这可基于刻蚀工艺、抛光工艺或薄化工艺来执行。抛光工艺可为化学机械抛光(cmp)工艺。在移除第二衬底303及第一衬底302之后,封装300-6包括结合堆叠或结合管芯。

46.图3g是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-7的剖视图,其中结合堆叠或结合管芯贴合到封装衬底305。这可通过利用凸块309(例如,使用利用铜凸块的倒装式芯片(c4)内连方法)将第一层310贴合到封装衬底305上来执行。在一个实施例中,封装衬底305可由氧化硅或另一氧化物材料形成。根据各种实施例,封装衬底305可利用封装凸块301耦合到pcb板(未示出)。

47.图3h是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-8的剖视图,其中底座318沉积在封装衬底305上且与第一层310中的每一电子管芯312相邻。这可通过利用图案化的光掩模外延生长半导体材料或聚合物材料以形成底座318来执行。

48.图3i是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-9的剖视图,其中透镜328形成在每一底座318上且与第二层320中的相应光子管芯322对准。这可通过在每一底座318上沉积一种或多种聚合物材料以形成贴合到相应的光子管芯322的聚合物透镜328来执行。聚合物透镜328以相同的高度对准相应的光子管芯322,这意味着光可被引导穿过聚合物透镜328且进入光子管芯322中的波导,且从波导被引导进入聚合物透镜328且穿过聚合物透镜328。

49.图3j是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-10的剖视图,其中光纤321贴合到第二层320中的每一聚合物透镜328。这可通过将光纤321以对准的高度贴合到每一聚合物透镜328来执行,使得光可通过透镜328及光纤321被引导进出相应的光子管芯322。聚合物透镜328设置在一位置处以耦合光纤321与相应的光子管芯322之间的光传输。

50.图3k是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-11的剖视图,其中散热器330沉积在第二层320上且可能部分地沉积在封装衬底305上。这可通过在第二层320上沉积导热材料(例如铜、银或铝)并使所述导热材料与第二层320接触来执

行。

51.图3l是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装300-12的剖视图,其中在散热器330中形成一个或多个热隔断332。这可通过以下方式来执行:基于光刻法从光掩模向散热器330界定几何图案;刻蚀散热器330以确定散热器330中的刻蚀区域;在刻蚀区域中沉积热绝缘材料以形成热隔断332;及执行化学机械抛光(cmp)以使热隔断332及散热器330的表面平滑。如图3l所示,在顶部管芯324与相邻的光子管芯322之间形成至少一个热隔断332,以避免或减少顶部管芯324与相邻的光子管芯322之间的热传递。

52.图4示出根据本公开一些实施例的用于光子及电子元件的封装集成的示例性方法400。所述方法开始于操作402处,其中在第一衬底上的第一层中形成电子管芯及底部管芯且通过通孔分隔开所述电子管芯与所述底部管芯。在操作404处,在第二衬底上的第二层中形成光子管芯及顶部管芯且分隔开所述光子管芯与所述顶部管芯。在操作406处,将第二层结合到第一层上,其中将光子管芯结合到电子管芯上。在操作408处,刻蚀第一衬底及第二衬底以形成结合堆叠。在操作410处,将结合堆叠的第一层机械贴合且电贴合到封装衬底上。

53.在操作412处,在封装衬底上且邻近第一层中的电子管芯形成底座。在操作414处,将聚合物透镜对准并贴合到第二层中的光子管芯,其中聚合物透镜形成在底座上。在操作416处,将光纤对准并贴合到聚合物透镜,用于通过透镜引导光进出光子管芯。因此,聚合物透镜可耦合光纤与光子管芯之间的光传输。在操作418处,在第二层上并部分地在封装衬底上沉积散热器。在操作420处,在顶部管芯与光子管芯之间在散热器中形成热隔断。图4中所示的操作顺序可根据本公开的不同实施例而改变。

54.图5a示出根据本公开一些实施例的另一示例性集成电路(ic)封装500的剖视图。应注意,封装500仅仅是实例,且并不旨在限制本公开。因此,应理解,可在图5a的封装500中设置附加的功能块或将附加的功能块耦合到图5a的封装500,且一些其他的功能块在本文中可仅作简要描述。

55.除了封装500包括聚合物波导528代替聚合物透镜来对准并贴合到第二层520中的光子管芯122之外,图5a中的封装500具有与图1a中的封装100相似的结构。

56.如图5a所示,封装500包括与第一层510中的每一电子管芯112相邻的模具518。模具518形成在封装衬底105上,且用作聚合物波导528的支撑。在一个实施例中,模具518具有50微米与100微米之间的高度。在每一模具518上沉积聚合物波导528。每一聚合物波导528对准第二层520中的相应光子管芯122,且被配置成引导光进出光子管芯122。在一个实施例中,聚合物波导528与第二层520中的光子管芯122中的硅波导对准,且被配置成引导光进出光子管芯122中的硅波导。沿着光的传播方向,聚合物波导可比硅波导宽。在一个实施例中,每一聚合物波导528具有2微米与10微米之间的宽度。在一个实施例中,每一聚合物波导528具有2微米与10微米之间的高度。

57.如图5a所示,封装500还包括对准并贴合到每一聚合物波导528的光纤121,以通过可位于聚合物波导528内的边缘耦合器或光栅耦合器引导光进出聚合物波导528。在一个实施例中,边缘耦合器或光栅耦合器位于光纤121与聚合物波导528之间。在另一实施例中,边缘耦合器或光栅耦合器位于聚合物波导528与光子管芯122之间。在另一实施例中,一个边缘耦合器或光栅耦合器位于光纤121与聚合物波导528之间;且另一边缘耦合器或光栅耦合

器位于聚合物波导528与光子管芯122之间。图5a中的封装500中的其它组件与图1a中的封装100中的组件相似。

58.图5b示出根据本公开一些实施例的另一示例性ic封装500的俯视图。图5a中的封装500的剖视图是沿图5b中所示的b-b’方向截取的。除了封装500包括整件式聚合物波导528代替聚合物透镜来对准并贴合到每一光子管芯122之外,图5b中的封装500具有与图1b中的封装100相似的结构。

59.如图5b所示,封装500包括多个聚合物波导528,所述聚合物波导中的每一者与相应的光子管芯122对准。在一个实施例中,每一聚合物波导528与第二层中的相应光子管芯122中的硅波导(未示出)对准。

60.封装500包括多个光纤阵列,所述多个光纤阵列中的每一者包括多个光纤121,且对准并贴合到相应的聚合物波导528。每一光纤121可为单模光纤或多模光纤。每一聚合物波导528被配置成引导相应的光子管芯122与相应的光纤阵列之间或相应的光子管芯122中的硅波导与相应的光纤阵列之间的光传输。图5b中的封装500中的其它组件与图1b中的封装100中的组件相似。

61.图6a到图6l示出根据本公开一些实施例的在制造工艺的各种阶段的示例性ic封装的剖视图。图6a到图6g中所示的阶段与图3a到图3g中所示的阶段相同,且参照以上关于图3a到图3g的阐述。

62.图6h是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装600-8的剖视图,其中模具618沉积于封装衬底305上且与第一层310中的每一电子管芯312相邻。这可通过利用图案化的光掩模沉积材料(例如氧化硅或另一玻璃材料)以形成模具618来执行。

63.图6i是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装600-9的剖视图,其中聚合物波导628形成在每一模具618上,且对准第二层320中的相应光子管芯322。这可通过在每一模具618上沉积一种或多种聚合物材料(例如硅聚合物)以形成贴合到相应的光子管芯322的聚合物波导628来执行。聚合物波导628可在相同高度处对准相应的光子管芯322,这意味着光可被引导穿过聚合物波导628并进入光子管芯322中的硅波导,和/或从硅波导被引导进入聚合物波导628并穿过聚合物波导628。

64.图6j是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装600-10的剖视图,其中光纤阵列621贴合到第二层320中的每一聚合物波导628。这可通过将光纤阵列621以对准的高度贴合到每一聚合物波导628来执行,使得光可通过聚合物波导628和光纤阵列621被引导进出相应的光子管芯322。聚合物波导628设置在一位置处以耦合光纤阵列621与相应的光子管芯322之间的光传输。

65.与图3k中所示的阶段类似,图6k是根据本公开一些实施例的在制造的各种阶段中的一个阶段的封装600-11的剖视图,其中散热器330沉积在第二层320上且可能部分地沉积在封装衬底305上。这可通过在第二层320上沉积导热材料(例如铜、银或铝)且使所述导热材料与第二层320接触来执行。

66.与图3l中所示的阶段类似,图6l是根据本公开一些实施例的封装600-12的剖视图,其中在散热器330中形成一个或多个热隔断332。如图6l所示,在顶部管芯324与相邻的光子管芯322之间形成至少一个热隔断332,以避免或减少顶部管芯324与相邻的光子管芯

322之间的热传递。

67.图7示出根据本公开一些实施例的用于光子元件及电子元件的封装集成的另一示例性方法700。所述方法开始于操作702处,其中在第一衬底上的第一层中形成电子管芯及底部管芯且通过通孔分隔开所述电子管芯与所述底部管芯。在操作704处,在第二衬底上的第二层中形成光子管芯及顶部管芯且将所述光子管芯与所述顶部管芯分隔开。在操作706处,将第二层结合到第一层上,其中将光子管芯结合到电子管芯上。在操作708处,刻蚀第一衬底及第二衬底以形成结合堆叠。在操作710处,将结合堆叠的第一层机械贴合且电贴合到封装衬底上。

68.在操作712处,在封装衬底上且邻近第一层中的电子管芯沉积模具。在操作714处,在模具上沉积聚合物波导且使所述聚合物波导对准第二层中的光子管芯。在操作716处,将光纤阵列对准并贴合到聚合物波导,用于通过聚合物波导引导光进出光子管芯。因此,聚合物波导可耦合光纤阵列与光子管芯之间的光传输。在操作718处,在第二层上且部分地在封装衬底上沉积散热器。在操作720处,在顶部管芯与光子管芯之间在散热器中形成热隔断。图7中所示的操作顺序可根据本公开的不同实施例而改变。

69.在一个实施例中,公开了一种封装。所述封装包括:封装衬底;第一层,包括位于所述封装衬底上的电子管芯;及第二层,包括光子管芯,其中所述第二层结合到所述第一层上,使得所述光子管芯结合到所述电子管芯上。在一实施例中,电子管芯包括用于光子管芯的驱动器。在一实施例中,第一层包括底部管芯,底部管芯通过通孔与电子管芯分隔开,其中通孔在第二层与封装衬底之间提供电连接。在一实施例中,第二层包括结合到底部管芯上的顶部管芯;且在第二层中,顶部管芯与光子管芯分隔开。

70.在一实施例中,底部管芯包括第一多个组件;顶部管芯包括第二多个组件;与底部管芯中的组件相比,顶部管芯中的每个组件具有更高的操作频率、更高的时钟频率、更好的电路区缩放能力或更高的存储速度中的至少一者。在一实施例中,封装还包括聚合物透镜及底座。聚合物透镜贴合到第二层中的光子管芯且被配置成引导光进出光子管芯;底座与第一层中的电子管芯相邻,其中聚合物透镜位于底座上。在一实施例中,封装还包括光纤。光纤贴合到聚合物透镜,以通过边缘耦合器或光栅耦合器引导光进出聚合物透镜,其中聚合物透镜设置在一位置处以耦合光纤与光子管芯之间的光传输。在一实施例中,封装还包括聚合物波导及模具。聚合物波导贴合到第二层中的光子管芯中的硅波导且被配置成引导光进出光子管芯中的硅波导,其中沿着光的传播方向,聚合物波导比硅波导宽;模具与第一层中的电子管芯相邻,其中聚合物波导形成在模具上。在一实施例中,封装还包括光纤。光纤贴合到聚合物波导,以通过边缘耦合器或光栅耦合器引导光进出聚合物波导,其中聚合物波导设置在一位置处以耦合光纤与光子管芯之间的光传输。

71.在另一实施例中,公开了一种半导体器件。所述半导体器件包括:衬底;第一层,包括位于所述衬底上的多个电子管芯;以及第二层,包括位于所述第一层上的多个光子管芯,其中所述多个光子管芯中的每一者位于所述多个电子管芯中的相应一者上且与所述多个电子管芯中的所述相应一者接触。在一实施例中,半导体器件还包括多个透镜阵列及多个光纤阵列。多个透镜阵列中的每一者包括m个贴合到第二层中的多个光子管芯中的相应一者的透镜;多个光纤阵列中的每一者包括m个光纤且贴合到多个透镜阵列中的相应一者,其中m个光纤中的每一者贴合到m个透镜中的相应一者,其中m个透镜中的每一者被配置成引

导相应的光子管芯与相应的光纤之间的光传输。在一实施例中,半导体器件还包括多个聚合物波导及多个光纤阵列。多个聚合物波导中的每一者贴合到第二层中的多个光子管芯中的相应一者中的硅波导;多个光纤阵列中的每一者包括多个光纤且贴合到多个聚合物波导中的相应一者,其中多个聚合物波导中的每一者被配置成引导相应的光子管芯中的硅波导与相应的光纤阵列之间的光传输。在一实施例中,第一层包括底部管芯及多个通孔;多个电子管芯中的每一者通过多个通孔中的相应通孔与底部管芯分隔开;多个通孔中的每一者在第二层与衬底之间提供电连接;第二层包括顶部管芯,顶部管芯结合到底部管芯上;且顶部管芯与第二层中的多个光子管芯中的每一者分隔开。在一实施例中,半导体器件还包括散热器。散热器形成在第二层上且与第二层接触,其中散热器包括多个热隔断,多个热隔断中的每一者位于顶部管芯与和顶部管芯相邻的光子管芯之间。

72.在又一实施例中,公开了一种用于形成半导体器件的方法。该方法包括:形成包括电子管芯的第一层;形成包括光子管芯的第二层,其中所述电子管芯包括至少一个用于所述光子管芯的驱动器;将所述第二层结合到所述第一层上以产生结合堆叠,其中所述光子管芯结合到所述电子管芯上;使用导电凸块将所述结合堆叠机械贴合且电贴合到封装衬底上,其中所述第一层利用所述导电凸块贴合到所述封装衬底。在一实施例中,形成第一层包括在第一衬底上的第一层中沉积硅;基于光刻法从光掩模确定几何图案;基于几何图案刻蚀硅以确定刻蚀区域;及在刻蚀区域中外延生长一种或多种半导体材料以形成:电子管芯、具有模拟和芯片组功能的底部管芯、及在底部管芯与第一层中的电子管芯之间的通孔,其中通孔在结合之后在第二层与封装衬底之间提供电连接。在一实施例中,形成第二层包括在第二衬底上的第二层中沉积硅;基于光刻法从光掩模界定几何图案;基于几何图案刻蚀硅以确定刻蚀区域;及在刻蚀区域中外延生长一种或多种半导体材料以形成光子管芯及具有计算元件的顶部管芯。在一实施例中,方法还包括在第二层上沉积散热器;及在顶部管芯与光子管芯之间在散热器中形成热隔断。在一实施例中,方法还包括在封装衬底上且邻近第一层中的电子管芯形成底座;将聚合物透镜贴合到第二层中的光子管芯,其中聚合物透镜定位在底座上;及将光纤贴合到聚合物透镜,使得聚合物透镜耦合光纤与光子管芯之间的光传输。在一实施例中,方法还包括在封装衬底上且邻近第一层中的电子管芯沉积模具;在模具上沉积聚合物波导,其中聚合物波导贴合到第二层中的光子管芯;及将光纤阵列贴合到聚合物波导,使得聚合物波导耦合光纤与光子管芯之间的光传输。

73.以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,他们可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,此种等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下对本文作出各种改变、代替及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1