一种减小硅光芯片热串扰的CMOS兼容结构

一种减小硅光芯片热串扰的cmos兼容结构

技术领域

1.本发明属于硅基光电子集成系统领域,具体涉及一种减小硅光芯片热串扰的cmos兼容结构。

背景技术:

2.近年来,微电子学一直是现代信息社会发展的驱动力。但是微电子芯片的微缩周期因受到物理、技术、经济各方面的限制而逐渐变慢,摩尔定律面临失效。然而,现代社会对信息高速处理的需求却并未因微电子技术的滞后而降低,信息拥堵问题成为最先凸显出的矛盾。

3.光子作为信息传递的载体,相比电子,具有稳定可控的调制和复用维度,如振幅、相位、波长、偏振态、模式等,具有更大的带宽、更高的频谱利用率和通信容量。它的优势来源于成熟微电子技术和宽带光电子技术在微纳范畴内的有机结合。其应用也从最初的微电子扩展到通信、计算、传感、人工智能,乃至消费领域。在以大数据为基础的现代信息社会,硅基光电子已经成为最具潜力的高效率、低成本片上解决方案。

4.在硅基光电子芯片上,可集成信息吞吐所需的各种光子、电子、光电子器件,包括光波导、调制器、探测器和晶体管集成电路等。然而硅的热光系数,比氮化硅、氧化硅等无源材料大1个数量级(室温下约为1.85

×

10-4

k-1

)。环境温度变化和芯片热量堆积对硅基光电器件的性能影响较为明显,而温控将增大芯片的能耗。因此减小硅光芯片之间的热串扰成为一个非常大的挑战。

技术实现要素:

5.本发明的目的是提供一种减小硅光芯片热串扰的cmos兼容结构,该结构仅在设计的基础上不添加额外的温控来减小热串扰。

6.为了实现以上设计目标,本发明的技术方案如下:

7.一种减小硅光芯片热串扰的cmos兼容结构,包括设于外层的金属圆柱环层和设于内层的空气圆柱环层;

8.所述金属圆柱环层的材料可以是铜、铝、钨等cmos工艺线包括的金属材料。

9.理想情况下所述金属圆柱环层和空气圆柱环层的深度由包层(cladding)顶部到box层和硅衬底(si substrate)交界面。但是金属圆柱环层和空气圆柱环层的深度和尺寸大小可以根据实际的工艺水平来调节。

10.采用各向同性以及cmos兼容的材料制备所述减小硅光芯片热串扰的cmos兼容结构,制备过程为:就新加坡微电子研究所(institute of microelectronics,ime)的标准工艺而言,光源采用245nm的深紫外光源,晶圆半径大小为8英寸,顶层硅厚度220nm,底下的二氧化硅层为2μm,工艺的标准线宽最小为200μm。

11.(1)无源三次刻蚀:首先先清洗晶圆,并在晶圆上用化学气相沉积(plasma enhanced chemical vapor deposition,pecvd)生长75nm的二氧化硅,然后在上面旋涂光

刻胶(photo resist,pr),光刻显影之后,通过刻蚀将光刻版的图形转移到二氧化硅上,这部分二氧化硅将作为硬掩膜(每次刻蚀完不被去胶)用于之后的硅刻蚀。去除光刻胶之后,利用感应耦合等离子体刻蚀机(inductively couple plasma etch,icp),向下局部刻蚀70nm,即可完成垂直耦合光栅的刻蚀。之后重新旋涂光刻胶,光刻显影选择性在垂直耦合光栅上方保留一部分光刻胶,然后利用icp向下刻蚀90nm,即可完成脊波导的刻蚀。最后旋涂光刻胶,然后光刻显影选择性地在垂直耦合光栅和脊波导上方保留一部分光刻胶,然后利用icp向下刻蚀60nm,即可完成最后一步——条波导的刻蚀。

12.(2)heater层和引线层的制作:先清除之前的光刻胶,然后在表面生长一层600nm厚的二氧化硅层,然后利用化学机械平坦化(chemical mechical planarization,cmp)使表面厚度一致,光刻显影,然后通过刻蚀600nm的二氧化硅形成从表面到硅层的通孔(via1层),然后分别沉积50nm厚的tan、750nm厚的al、50nm厚的tan和50nm氮化物,然后光刻显影生成掩模,然后刻蚀表面的金属层,形成第一层互连线(matal 1层)。再pecvd生长1400nm二氧化硅、5nm钛、120nm氮化钛和60nm氮化物。然后光刻显影生成掩模,刻蚀掉表面的金属层,可以得到氮化钛的heater。再生长1μm厚的二氧化硅,然后光刻显影生成掩模,通过刻蚀可以形成从表面到氮化钛heater或是matel 1层的通孔(via2层),pecvd生长25nm的tan和2000nm的al。然后通过光刻显影和刻蚀,形成matel2。然后生长二氧化硅层,然后光刻显影刻蚀,可以开出一个“窗口”(bond open层),使matel2层有一部分裸露到空气中,方便引线。

13.以上就是器件的刻蚀制备过程,而本发明的结构的空气圆柱环层就是在上述过程结束之后刻深槽(deep trench)(深槽位于金属圆柱环层内侧,需避开器件,空气圆柱环层的内侧为需减小热串扰的结构),金属圆柱环层视工艺情况而制备,比如在ime只能由metal 1和metal 2拼接形成。而最佳的情况是像虚线框内的金属一样,直接刻蚀到硅衬底层(si substrate)。

14.本发明的有益效果在于:

15.本发明的一种减小硅光芯片热串扰的cmos兼容结构,可以有效屏蔽芯片上其他有源器件产生的热串扰,进而保证温度敏感的硅光器片的工作性能,比如硅光滤波器。而非为了降低热串扰将二者之间的距离加大,这样会增大整体尺寸,不利于系统的片上集成化;也可以在不加温控的情况下降低热串扰,有效避免了能耗增加。本发明的结构即双层圆柱环层的厚度可以很薄,是根据内部滤波器的大小而设计。实际制备时,考虑工艺的最小尺寸,在保持工作性能的情况下,可以适当加厚到符合工艺水平。

附图说明

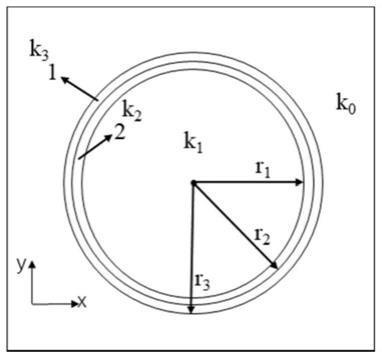

16.图1是本发明的一种减小硅光芯片热串扰的cmos兼容结构;

17.图2是标准工艺下的soi波导;

18.图3是ime加工示意图。

具体实施方式

19.如图1为在xy视图下的本发明的一种减小硅光芯片热串扰的cmos兼容结构:包括设于外层的金属圆柱环层和设于内层的空气圆柱环层;

20.如图2是在xz视图下的标准工艺的soi波导;

21.所述金属圆柱环层的材料可以是铜、铝、钨等cmos工艺线包括的金属材料,理想情况下所述金属圆柱环层和空气圆柱环层的深度由包层(cladding)顶部到box层和硅衬底(si substrate)交界面。但是金属圆柱环层和空气圆柱环层的深度和尺寸大小可以根据实际的工艺水平来调节;

22.基于中性夹杂思想的结构的设计:

23.基本思想:当夹杂之后的等效参数与背景材料的物理参数相等时,背景材料中(夹杂以外区域)的物理场不会受到扰动。

24.基于以上的设计思想,均匀各向同性材料的夹杂层的体积分数为:

[0025][0026]

其中,r《r1的部分是圆柱芯层即内部硅光芯片所在的区域,r2》r》r1的部分是空气圆柱环层,r3》r》r2的部分是金属圆柱环层。且金属环柱层和空气环柱层即夹杂层。则整个圆柱的等效热导率:

[0027][0028]

其中,其中为圆柱芯层材料(硅光滤波器所在区域)的热导率,k0是背景材料的热导率,k2是空气的热导率,k3是金属的热导率,l是夹杂层数。当有两层时,l=2,当时得到针对k0设计的结构:

[0029][0030][0031]

在cmos标准工艺下选择合适的材料,结合工艺最小尺寸合理设计结构。简单来讲,空气的热导率仅有0.0263w/mk,空气圆柱环层起到很好的隔热作用。而金属的热导率比较高,比如cu的热导率约为400w/mk,可以将热引导至下层的硅衬底之中,硅(si)的热导率为148w/mk,比二氧化硅(sio2)的热导率1.38w/mk高一百多倍,可以很好的把热引导走。传统的芯片上隔热会用热导率比较低的二氧化硅(sio2)来隔热,但是这是把双刃剑,二氧化硅(sio2)的低热导率也会把热限制起来。所以本发明提出的结构可以弥补这个缺点。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1