用于光电系统的模块化组件的制作方法

1.本公开的主题涉及一种光子集成光路(pic)和电子集成电路(eic)的晶片级组件。本文所公开的技术在将多信道光纤阵列耦合到这种组件的pic方面提供微米或亚微米精度。

背景技术:

2.当组装复杂光学子组件或具有高度集成光子集成电路(pic)的模块时必须有效使用空间。向/从外部光纤将光耦合到这些pic带来了特定挑战。光纤耦合通常使用主动对准来实现,所述主动对准是昂贵的、耗时的并且可能占据组件中的宝贵空间。

3.实现光纤耦合的当前解决方案涉及(i)使pic与光纤块主动对准,或(ii)使用单独v形槽阵列,所述单独v形槽阵列使用主动对准技术或不太准确的被动技术与pic对准。主动对准技术需要昂贵的设备,而被动对准技术可能导致较大的耦合损耗并且因此导致较低的性能。

4.本公开的主题涉及克服上述一个或多个问题或至少减轻其影响。

技术实现要素:

5.如本文所公开,组件用于集成至少一个光纤块和至少一个光子集成电路(pic)芯片。所述至少一个pic芯片具有第一表面并且具有用于光学信号的至少一个第一波导。所述组件包括衬底和至少一个波导(wg)芯片。所述衬底具有带第一缓冲器的第一侧。所述第一缓冲器与所述至少一个pic芯片的所述第一表面可附连地相邻。所述至少一个波导(wg)芯片具有第一小平面和第二小平面以及第二表面。所述第二表面具有第二缓冲器,所述第二缓冲器可附连到所述衬底的所述第一侧上的所述第一缓冲器。所述至少一个wg芯片具有在其中设置在所述第一小平面与所述第二小平面之间的至少一个第二波导。所述第一小平面处的所述至少一个第二波导被配置来使所述光学信号与所述至少一个光纤块耦合。所述第二小平面处的所述至少一个第二波导被配置来使所述光学信号与所述至少一个pic芯片的所述至少一个第一波导耦合。

6.如本文所公开,组件用于将至少一个光纤块和至少一个电子集成电路(eic)芯片与单独电子电路集成。所述组件包括衬底、至少一个光子集成电路(pic)芯片和至少一个波导(wg)芯片。所述衬底具有带第一缓冲器的第一侧。所述第一缓冲器与所述至少一个eic芯片的所述第一表面可附连地相邻。所述至少一个pic芯片具有用于光学信号的至少一个第一波导并且具有第一表面。所述第一表面具有可附连到所述第一缓冲器的多个第二缓冲器。所述至少一个波导(wg)芯片具有第一小平面和第二小平面以及第二表面。所述第二表面具有可附连到所述第一缓冲器的多个第三缓冲器。所述至少一个wg芯片具有在其中设置在所述第一小平面与所述第二小平面之间的至少一个第二波导。所述第一小平面处的所述至少一个第二波导被配置来使所述光学信号与所述至少一个光纤块耦合。所述第二小平面处的所述至少一个第二波导被配置来使所述光学信号与所述至少一个pic芯片的所述至少

一个第一波导耦合。

7.如本文所公开,设备与多个电子集成电路(eic)芯片一起使用以用于将多个光纤块连接到专用集成电路(asic)芯片。所述设备包括:电路板,所述asic芯片安装在所述电路板上;和如以上所公开安装在所述电路板上的多个组件,其中所述asic芯片是所述单独电子电路。

8.如本文所公开,一种将至少一个光纤块的光学信号与单独电子电路的电子信号集成的方法包括(未必按顺序):将至少一个电子集成电路(eic)芯片安装到衬底的第一侧上的一个或多个第一缓冲器;将至少一个光子集成电路(pic)芯片安装到所述第一缓冲器中的一个或多个;将至少一个波导(wg)芯片安装到所述第一缓冲器中的一个或多个;将所述至少一个wg芯片的第二小平面处的至少一个第一波导与所述至少一个pic芯片的至少一个第二波导对准;将设置在所述衬底的第二侧上并且与所述第一缓冲器中的一个或多个电连通的一个或多个第二缓冲器连接到所述单独电子电路;以及将所述至少一个光纤块的所述光学信号连接到所述至少一个wg芯片的第一小平面处的所述至少一个第一波导。

9.前述概述并不意图概述本公开的每个潜在实施方案或每种方面。

附图说明

10.图1a至图1b例示用于本公开的多芯片组件的衬底的顶视图和剖视图。

11.图2a例示提供直接光纤附接的多芯片组件的平面视图。

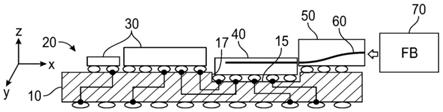

12.图2b例示提供直接光纤附接的多芯片组件的侧视图。

13.图2c示意性地例示用于所公开组件的缓冲器布置。

14.图3a例示本公开的波导芯片的透视图。

15.图3b例示波导芯片的端视图。

16.图3c例示波导芯片的底视图。

17.图4例示具有带穿通硅通孔的光子集成电路芯片的多芯片组件的侧视图。

18.图5a例示具有对准沟槽的多芯片组件的侧视图。

19.图5b例示具有对准支架和肩部的多芯片组件的侧视图。

20.图6例示具有与专用集成电路一起使用的本公开的多芯片组件的共同封装的光学器件的设备。

具体实施方式

21.图1a至图1b例示用于根据本公开的模块化多芯片组件的衬底或晶片10的顶视图和剖视图。衬底10具有第一侧12和第二侧16,所述第一侧12和所述第二侧16分别具有第一组缓冲器14和第二组缓冲器18。在内部,衬底10具有配置在第一缓冲器14和/或第二缓冲器18之间的电连接件11。这些电连接件11在生产期间被预布置并且被配置出于衬底10和最终组装的目的。

22.如这里所示,缓冲器14、18可以是焊料凸块。然而,任一侧12、16可具有缓冲器,所述缓冲器包括焊料凸块、凸块下金属或它们的组合。此外,尽管描述了焊料凸块和凸块下金属,但可使用各种倒装芯片技术,诸如球栅阵列、铜柱、柱形凸块等。因此,衬底10上的缓冲器14、18以及本文别处引用的那些缓冲器(34,44,54:图2b)可涵盖倒装芯片技术中使用的

任何此类特征。

23.总体上,衬底10可由玻璃材料、硅材料、陶瓷材料或诸如用于晶片的其他材料构成。衬底10可通过任何合适的生产工艺形成以包括用于电连接件11的金属。缓冲器14、18可包括凸块或球,所述凸块或球可使用已知技术来沉积。取决于实施方式,缓冲器14、18可由典型材料(诸如共晶材料、无铅材料或高铅材料)构成或缓冲器14、18可以是晶片材料上的cu柱凸块。

24.在生产时,衬底10可用于在上面安装多个芯片并且将那些附加芯片的模块化组件与单独电子电路的部件集成。例如,衬底10可用于2-d或2.5-d集成中的倒装芯片结合。至少一侧12可接收倒装芯片安装在侧12上的电子集成电路(eic)芯片、光子集成电路(pic)芯片和三维波导芯片。衬底10中的多个金属层被采用为电连接件11以在各种eic与pic之间或向/从外部板和/或其他电子电路按特定路线发送电信号(例如,射频信号和直流控制)。

25.如图2a至图2b所示,模块化多芯片组件20的实例以平面视图和侧视图例示。组件20提供与光纤块70的直接光纤附接以将光学信号与电子信号集成。

26.组件20包括倒装芯片安装在衬底10的侧12上的至少一个电子集成电路(eic)芯片30、至少一个光子集成电路(pic)芯片40和至少一个波导(wg)芯片50。这里,示出三个eic芯片30、两个pic芯片40和两个wg芯片50,但根椐实施方式可使用任何其他组合。

27.尽管其他实施方式可提供常规芯片安装,但eic芯片30优选地倒装芯片安装在衬底10的缓冲器(例如,焊料凸块14)上,使得无需销孔。具体地,eic芯片30可具有可附连到衬底的焊料凸块14的凸块下金属(34)。类似地,pic芯片40和wg芯片50可具有可附连到衬底的焊料凸块14的凸块下金属(44,54)。当然,根据缓冲器可使用其他布置。例如并且如图2c示意性地示出,衬底10可具有焊料凸块14、18,所述焊料凸块14、18可连接到eic芯片30、pic芯片40、wg芯片50或其他电子装置上的焊料凸块或凸块下金属。另选地,衬底10上的缓冲器14、18可以是凸块下金属,所述凸块下金属可连接到eic芯片30、pic芯片40、wg芯片50或其他电子装置上的焊料凸块。

28.这些缓冲器14中的预配置缓冲器具有与彼此和/或与衬底10的另一侧16上的缓冲器18的已配置电连接件11。根据具体情况,这些其他缓冲器18可以是焊料凸块、凸块下金属或它们的组合。如稍后所论述,这些底部缓冲器18被配置来连接成与实施方式中的单独电子电路通信。最后,缓冲器14、18、34、44、54在衬底10与部件30、40、50等之间的布置取决于实施方式并且可发生变化。

29.至少一个pic芯片40具有用于传达光学信号的一个或多个内部波导46并且具有可附连到用于电信号的衬底的缓冲器(例如,焊料凸块14)的多个缓冲器(例如,凸块下金属44)。

30.至少一个wg芯片50具有用于传达光学信号的一个或多个内部波导60并且具有可附连到衬底的缓冲器(例如,焊料凸块14)的多个缓冲器(例如,凸块下金属54)。凸块下金属(54)可主要用于wg芯片50与衬底的放置和对准,但它们也可用于电信号。

31.波导(wg)芯片50充当pic芯片40与光纤块70的各种光纤之间的桥接芯片。总体上,wg芯片50由玻璃材料、聚合物材料、硼硅酸盐等构成,其中设置有波导60。wg芯片50的波导60提供水平和/或竖直方向的变化以在相关联光纤块70与pic芯片30之间传达光学信号。

32.如图3a至图3c所示,wg芯片50具有第一小平面52a和第二小平面52b并且具有底表

面56,所述底表面56具有可附连到焊料凸块(14)的缓冲器(例如,凸块下金属54),如先前所指出。wg芯片50具有在其中设置在第一小平面52a与第二小平面52b之间的多个波导60。为了有利于组装和对准,wg芯片50中的波导60可从一个小平面52b处的底部附近朝向另一小平面52a处的中间路由。其他布置是可能的。

33.wg芯片50可具有一个或多个对准特征以有利于与光纤块(70)和/或pic芯片(40)的对准。对准特征可实现pic芯片(40)与光纤块(70)的光纤之间的被动光纤附接。例如,第一小平面52a具有至少两个对准特征55,诸如两个销孔或狭槽55,所述两个销孔或狭槽55被配置来将对准销接纳在光纤阵列块(70)的面上。以此方式,光纤阵列块(70)可与wg芯片50机械地配合,从而使光纤与波导60对接耦合,而无需主动对准。光纤与波导60之间的倏逝耦合在一些布置中也是可能的。可比类型的对准特征可在另一面52b上使用以用于耦合到pic芯片(40)上的狭槽或销。wg芯片50的其他侧可具有对准特征以用于使芯片(50)与其他wg芯片(50)或组件(20)的衬底(10)上的其他元件相邻定位并对准。

34.wg芯片50可但不限于使用3-d激光直写工艺来制造。在所述工艺中,wg芯片50的主体由特定材料诸如硼硅酸盐形成。波导60可通过改变用于波导60的材料的折射率而形成在主体中。所述工艺还可通过改变来形成3d微机械加工特征。此类微机械加工特征可用于部件的机械对准,如本文所公开。

35.如图2a至图2b所示,光纤块70与wg芯片50的小平面52a连接,使得波导60可传达光学信号。wg芯片50的另一小平面52b与pic芯片40相邻设置,其中波导60被配置来与pic芯片40传达光学信号。如将了解的,pic芯片40包括其自身的波导46和光子电路布置(未示出)。pic芯片的波导46可对接耦合到wg芯片的波导60以根据具体情况在任一方向上对它们之间的光学信号进行成像。pic芯片的波导46也可短暂地耦合到wg芯片的波导60。pic芯片的波导46也可辐射地耦合到wg芯片的波导60,诸如通过两个芯片处的光栅耦合器。

36.如图所示,图2a至图2b的组件20使用wg芯片50来在预配置衬底10上实现光纤块70与多个芯片(包括eic芯片30和pic芯片40)的直接光纤连接。考虑到效率以及一种类型的芯片的安装可能如何干扰另一种类型的芯片的安装,芯片30、40、50可以任何合适的次序安装并附连在衬底10上。

37.例如,至少一个pic 40和至少一个wg芯片50以自对准精度(其可以是微米或更佳)而倒装芯片结合。wg芯片50中的光波导60对接耦合到pic芯片40中的波导46。光波导60接着路由到另一小平面52a,其中进行与光纤阵列块70的直接或紧邻接触。如将是典型的,pic芯片40可具有至少一个主动元件,即结合芯片的波导46使用的激光器、电光调制器、光电探测器、光开关等。

38.芯片和它们的布置的多个变型是可能的。在一个实例中,图4例示具有带穿通硅通孔44的pic芯片的模块化多芯片组件20的侧视图。如此布置中所示,pic芯片40上的波导46可朝向pic芯片40的顶表面定位。这些通孔44可用激光引发的选择性蚀刻来形成并且可填充有铜等以提供电连接,而无需用于芯片的光子电路的引线结合。

39.如以上所论述,衬底10的缓冲器(例如,焊料凸块14)和预配置内部连接11允许多个芯片30、40、50的对准并且有利于制造组件20及其集成到单独电子电路中。数微米的放置精度可使用cmos生产工艺来实现。自对准可在共熔回流期间通过焊料凸块14的表面张力来实现。以此方式,多个芯片30、40、50可利用由焊料凸块14的回流提供的自对准能力倒装芯

片安装在衬底10上。尤其在竖直方向(z轴)上的附加自对准可通过在衬底10和/或pic芯片40和wg芯片50上使用机械结构来实现。多个机械结构可被提供来提高各种芯片之间的自对准的精度。这些结构可包括支脚、构造和肩部。

40.在一个实例中,图5a例示具有对准沟槽15的多芯片组件20的侧视图。如图所示的沟槽15被限定在衬底10的第一侧12中的一定深度处,并且pic芯片40可安装在沟槽15中。沟槽15的一个或多个肩部17可提供表面,pic芯片40抵靠所述表面安装以有利于水平(x-y轴)对准。主要地,沟槽15的深度可有利于波导60在wg芯片50的第二小平面54处与pic芯片40的内部波导46的竖直(z轴)对准。

41.在另一实例中,图5b例示具有对准支架19和肩部17的多芯片组件20的侧视图。如图所示的支架19可以是衬底10的一部分并且可限定在一个或多个高度处,并且pic芯片40和/或wg芯片50可在附连到缓冲器(例如,焊料凸块14)时安装在支架19上。除此之外或在另选方案中,支架19可以是芯片40、50的一部分并且可在一个或多个限定高度处从芯片40、50的底部扩张。同样地,衬底10或芯片40、50上的支架19可抵靠垂直表面配合以主要实现竖直对准或可在衬底10或芯片40、50中的凹陷或狭槽中配合。如将了解的,配合在可比凹陷或狭槽中的支架19可提供竖直和水平对准。以任一方式,支架19可有助于pic芯片40和wg芯片50上的相应波导(46,60)之间的竖直(z轴)对准。

42.一个或多个肩部17可从衬底10的第一侧12延伸并且可提供表面,pic芯片40(和/或wg芯片50)抵靠所述表面安装以有利于波导之间的水平(x-y轴)对准。

43.eic芯片30可能无需沟槽、支架和肩部的这些特征,但它们可被同等设置以便于它们放置在衬底10上。此外,衬底10的第二侧14可根据需要包括沟槽、肩部、支架、销、狭槽等的对准特征以有利于对准并集成到其他部件中。

44.如所论述,组件20使多个芯片30、40、50以对准和有序方式在衬底10上安装并集成在一起。多个模块化组件20可一起用于共同封装光学器件以用于与其他电子部件集成。例如,图6例示具有与专用集成电路芯片104(诸如在信号切换和处理中使用的开关)一起使用的本公开的多个模块化组件20的电路100的平面视图。asic芯片104安装在电路板102上,所述电路板102包括印刷电路(未示出)和用于asic芯片104的典型销连接(未示出)。组件20安装在电路板102上,其中缓冲器(例如,焊料凸块)如所配置连接到板102上的印刷电路。在此布置中,多个组件20将多个光学信号与各种ic芯片30和asic芯片102的电子信号连接。

45.正如此简短实例将示出的,所公开的组件20可结合其他组件20和其他电路使用以有利于集成光学信号和电子信号的设备的生产和制造。

46.如本文所公开,组件20提供电子集成电路(eic)30与光子集成电路(pic)40之间的对准并且进一步通过使用光桥芯片(即wg芯片50)提供光纤与pic 40的自对准。所述布置允许光纤直接附接到这些预组装系统。

47.如本文所公开,wg芯片50(或被动光桥芯片)可与其他pic芯片40一起倒装芯片安装在衬底10上。这些芯片40、50均可以大约微米或更佳的自对准精度倒装芯片安装在衬底10上。自对准可在倒装芯片结合期间主要通过凸块和凸块下金属的回流来实现。wg芯片50桥接光纤与pic芯片40之间的光学通信并且允许光纤块70的直接附接。

48.存在若干优点。首先,组件20去除光芯片之间以及光芯片与光纤之间所需的任何主动或被动对准。第二,衬底10可被预配置并且广泛地使用以生产多个组件20以用于一起

集成到附加电路中。

49.优选和其他实施方案的前述描述并不意图限制或约束发明人设想的发明性概念的范围或适用性。受益于本公开将了解,可单独地或结合所公开的主题的任何其他实施方案或方面中的任何其他所描述的特征利用以上根据所公开的主题的任何实施方案或方面所描述的特征。

50.作为公开本文所包含的发明性概念的交换,申请人希望由所附权利要求提供的所有专利权。因此,希望所附权利要求包括所有修改和更改以在最大程度上归入附加权利要求或其等价物的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1