阵列基板及制作方法、显示面板与流程

1.本发明涉及显示器技术领域,特别是涉及一种阵列基板及制作方法、显示面板。

背景技术:

2.随着显示技术的发展,轻薄化的显示面板倍受消费者的喜爱,尤其是轻薄化的显示面板(liquid crystal display,lcd)。

3.现有的一种显示装置包括薄膜晶体管阵列基板(thin film transistor array substrate,tft array substrate)、彩膜基板(color filter substrate,cf substrate)以及填充在薄膜晶体管阵列基板和彩膜基板之间的液晶分子,上述显示装置工作时,在薄膜晶体管阵列基板的像素电极与彩膜基板的公共电极分别施加驱动电压或者在薄膜晶体管阵列基板的公共电极和像素电极分别施加驱动电压,控制两个基板之间的液晶分子的旋转方向,以将显示装置的背光模组提供的背光折射出来,从而显示画面。

4.现有技术中的氧化物薄膜晶体管(tft)具有优异的电学性能、大面积制造均匀性及低制造成本等优势,有望在各类平板显示产品中实现应用。现有大多数阵列基板上的像素电极通常额外采用一层透明金属氧化物制成,再通过接触孔与漏极导电连接,不仅制作工艺复杂,而且还浪费原材料。所以,有的像素电极与源极、漏极以及有源层均采用一层透明金属氧化物半导体(例如铟镓锌锡氧化物(igzto))制成,然后再对像素电极、源极和漏极部分进行导体化处理,虽然可以简化制作工艺,但是由于源极和漏极部分较窄,再加上透明金属氧化物半导体的导电性能较差,大大降低了源极和漏极的导电性能,导致驱动功耗增加,影响数据信号的传输。所以急需一款既能简化制作工艺又不影响源极或漏极的导电性能的阵列基板。

技术实现要素:

5.为了克服现有技术中存在的缺点和不足,本发明的目的在于提供一种阵列基板及制作方法、显示面板,以解决现有技术中的阵列基板无法同时兼顾简化制作工艺和源极/漏极的导电性能的问题。

6.本发明的目的通过下述技术方案实现:

7.本发明提供一种阵列基板的制作方法,包括:

8.提供基底;

9.在所述基底的上方形成第一金属层,对所述第一金属层进行蚀刻,所述第一金属层形成图案化的扫描线和栅极,所述栅极与所述扫描线电性连接;

10.在所述基底的上方形成覆盖所述扫描线和所述栅极的第一绝缘层;

11.在所述第一绝缘层的上方形成金属氧化物半导体层,对所述金属氧化物半导体层进行蚀刻,所述金属氧化物半导体层形成图案化的有源层、源极、漏极以及像素电极,所述源极和所述漏极通过所述有源层导电连接,所述像素电极与所述漏极导电连接;

12.在所述金属氧化物半导体层的上表面涂布光刻胶层,以所述第一金属层掩模板,

从所述基底远离所述光刻胶层一侧对所述光刻胶层进行光刻处理,所述光刻胶层形成图案化的光刻胶图案,所述扫描线、所述栅极以及所述有源层均与所述光刻胶图案相对应;

13.以所述光刻胶图案为遮挡,从所述光刻胶图案远离所述基底的一侧对所述金属氧化物半导体层进行导体化处理,所述金属氧化物半导体层对应所述源极、所述漏极以及所述像素电极的区域被导体化;

14.在所述金属氧化物半导体层的上表面形成第二金属层,对所述第二金属层进行蚀刻并形成图案化的数据线,所述数据线直接与所述源极导电连接;

15.所述第二金属层还形成图案化的第一连接部,所述数据线与所述第一连接部导电连接,所述第一连接部完全覆盖住所述源极并直接与所述源极的上表面相接触;和/或,所述第二金属层还形成图案化的第二连接部,所述第二连接部完全覆盖住所述漏极并直接与所述漏极的上表面相接触。

16.进一步地,所述有源层的上表面设有沟道保护层,所述沟道保护层完全覆盖住所述有源层。

17.进一步地,所述光刻胶层和所述沟道保护层均采用正性光敏材料,所述光刻胶图案与所述有源层对应的区域形成所述沟道保护层。

18.进一步地,所述制作方法还包括:

19.在所述第一绝缘层的上方形成第二绝缘层以及在所述第二绝缘层上方形成透明导电层,对所述透明导电层进行蚀刻并形成图案化的公共电极,所述公共电极与所述像素电极相互绝缘设置。

20.本发明还提供一种阵列基板,所述阵列基板采用上述的制作方法制成,所述阵列基板包括:

21.基底;

22.设于所述基底上方的第一金属层,所述第一金属层包括扫描线和栅极,所述栅极与所述扫描线电性连接;

23.设于所述第一金属层上方的第一绝缘层,所述第一绝缘层覆盖所述扫描线和所述栅极;

24.设于所述第一绝缘层上方的金属氧化物半导体层,所述金属氧化物半导体层包括呈半导体的有源层以及呈导体的源极、漏极和像素电极,所述源极和所述漏极通过所述有源层导电连接,所述像素电极与所述漏极导电连接;

25.设于所述金属氧化物半导体层上表面的第二金属层,所述第二金属层包括数据线,所述数据线直接与所述源极导电连接;

26.所述第二金属层还包括第一连接部,所述数据线与所述第一连接部导电连接,所述第一连接部完全覆盖住所述源极并直接与所述源极的上表面相接触;和/或,所述第二金属层还包括第二连接部,所述第二连接部完全覆盖住所述漏极并直接与所述漏极的上表面相接触。

27.进一步地,所述第一连接部在所述基底上的投影与所述有源层在所述基底上的投影部分重叠;所述第二连接部在所述基底上的投影与所述有源层在所述基底上的投影部分重叠。

28.进一步地,所述有源层的上表面设有沟道保护层,所述沟道保护层完全覆盖住所

述有源层。

29.进一步地,所述沟道保护层采用正性光敏材料。

30.进一步地,所述阵列基板还包括设于所述第一绝缘层上方的第二绝缘层以及设于所述第二绝缘层上方的透明导电层,所述透明导电层包括公共电极,所述公共电极与所述像素电极相互绝缘设置。

31.本发明还提供一种显示面板,包括上述的阵列基板以及与所述阵列基板相对设置的对置基板以及设于所述阵列基板和所述对置基板之间的液晶层。

32.本发明有益效果在于:通过将有源层、源极、漏极以及像素电极一同采用金属氧化物半导体层制成,像素电极直接与漏极导电连接,可以节省蚀刻接触孔以及额外制作像素电极的步骤,简化了制程工艺;并且第一连接部和/或第二连接部与数据线一同采用第二金属层制成,第一连接部完全覆盖住源极并直接与源极的上表面相接触,第一连接部可以降低源极的电阻,第二连接部完全覆盖住漏极并直接与漏极的上表面相接触,第二连接部可以降低漏极的电阻,增加了源极和/或漏极的导电性能,使得驱动功耗降低,避免影响数据信号的传输。

附图说明

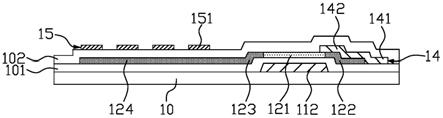

33.图1是本发明实施例一中阵列基板的截面示意图;

34.图2a-2h是本发明实施例一中阵列基板的制作方法的截面示意图;

35.图3a-3f是本发明实施例一中阵列基板的制作方法的平面示意图;

36.图4是本发明实施例二中阵列基板的截面结构示意图;

37.图5是本发明实施例二中阵列基板去掉公共电极的平面示意图;

38.图6是本发明实施例三中阵列基板的截面结构示意图;

39.图7a-7f是本发明实施例三中阵列基板的制作方法的截面示意图;

40.图8是本发明实施例三中阵列基板去掉公共电极的平面示意图;

41.图9是本发明中显示面板的截面结构示意图。

具体实施方式

42.为更进一步阐述本发明为达成预定发明目的所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本发明提出的阵列基板及制作方法、显示面板的具体实施方式、结构、特征及其功效,详细说明如下:

43.[实施例一]

[0044]

图1是本发明实施例一中阵列基板的截面示意图,图2a-2h是本发明实施例一中阵列基板的制作方法的截面示意图,图3a-3f是本发明实施例一中阵列基板的制作方法的平面示意图。

[0045]

如图1所示,本发明实施例一提供的一种阵列基板,包括:

[0046]

基底10,基底10可以由玻璃、石英、硅、丙烯酸或聚碳酸酯等材料制成,基底10也可为柔性基板,用于柔性基板的适当材料包括例如聚醚砜(pes)、聚萘二甲酸乙二醇酯(pen)、聚乙烯(pe)、聚酰亚胺(pi)、聚氯乙烯(pvc)、聚对苯二甲酸乙二醇酯(pet)或其组合。

[0047]

设于基底10上方的第一金属层11(图3a),第一金属层11直接设于基底10的上表

面,第一金属层11包括扫描线111和栅极112,栅极112与扫描线111电性连接。其中,第一金属层11可以采用金属例如铜(cu)、银(ag)、铬(cr)、钼(mo)、铝(al)、钛(ti)、锰(mn)、镍(ni)等,或者采用上述金属的组合例如al/mo、cu/mo等。

[0048]

设于第一金属层11上方的第一绝缘层101,第一绝缘层101直接设于基底10和第一金属层11的上表面并覆盖扫描线111和栅极112。其中,第一绝缘层101的材料为氧化硅(siox)、氮化硅(sinx)或二者的组合。

[0049]

设于第一绝缘层101上方的金属氧化物半导体层12(图2b),金属氧化物半导体层12直接设于第一绝缘层101的上表面,金属氧化物半导体层12包括呈半导体的有源层121以及呈导体的源极122、漏极123和像素电极124,源极122和漏极123通过有源层121导电连接,像素电极124与漏极123导电连接。即金属氧化物半导体层12包括导体部分和半导体部分,导体部分包括源极122、漏极123和像素电极124,半导体部分包括有源层121。具体地,可以通过对金属氧化物半导体层12进行导体化处理的方式,例如采用等离子体进行处理,离子轰击、氢(h2)掺杂、氦(he)掺杂以及氩(ar)掺杂等方式,使金属氧化物半导体层12的部分区域实现导体化,以形成导体化的源极122、漏极123和像素电极124,但有源层121未被导体化且仍保留为半导体。金属氧化物半导体层12优选采用透明金属氧化物半导体材料制成,例如铟锌氧化物(inzno)、铟镓氧化物(ingao)、铟锡氧化物(insno)、锌锡氧化物(znsno)、镓锡氧化物(gasno)、镓锌氧化物(gazno)、铟镓锌氧化物(igzo)或铟镓锌锡氧化物(igzto)等制成。

[0050]

设于金属氧化物半导体层12上表面的第二金属层14,第二金属层14包括数据线141,数据线141直接与源极122导电连接。其中,第二金属层14可以采用金属例如铜(cu)、银(ag)、铬(cr)、钼(mo)、铝(al)、钛(ti)、锰(mn)、镍(ni)等,或者采用上述金属的组合例如al/mo、cu/mo等。

[0051]

本实施例中,第二金属层14还包括第一连接部142,数据线141与第一连接部142导电连接,第一连接部142完全覆盖住源极122并直接与源极122的上表面相接触。由于第一连接部142与数据线141采用同一层金属层制作而成,第一连接部142的电阻较小,使得第一连接部142完全覆盖住源极122后,第一连接部142和源极122整体上的电阻较小,从而增加源极122的导电性。优选地,第一连接部142在基底10上的投影与有源层121在基底10上的投影部分重叠,使得第一连接部142还覆盖一分部有源层121,以增加源极122和漏极123在沟道处的导通性能。当然,在其他实施例中,第二金属层14包括第二连接部143,第二连接部143完全覆盖住漏极123并直接与漏极123的上表面相接触。由于第二连接部143与数据线141采用同一层金属层制作而成,第二连接部143的电阻较小,使得第二连接部143完全覆盖住漏极123后,第二连接部143和漏极123整体上的电阻较小,从而增加漏极123的导电性。当然,第二连接部143在基底10上的投影与有源层121在基底10上的投影部分重叠,使得第二连接部143还覆盖一分部有源层121,以增加源极122和漏极123在沟道处的导通性能。

[0052]

本实施例中,阵列基板还包括设于第一绝缘层101上方的第二绝缘层102以及设于第二绝缘层102上方的透明导电层15,透明导电层15包括公共电极151,公共电极151与像素电极124相互绝缘设置。具体地,第二绝缘层102设于第二金属层14、金属氧化物半导体层12以及第一绝缘层101的上表面,第二绝缘层102覆盖住数据线141、第一连接部142、有源层121、漏极123以及像素电极124。公共电极151设于第二绝缘层102的上表面,公共电极151与

像素电极124通过第二绝缘层102相互绝缘。当然,在其他实施例中,阵列基板上也可不用设置公共电极151,公共电极151设于彩膜基板20(图9)上,以形成tn或va显示模式。

[0053]

其中,基底10朝向第一金属层11的方向为上方向,基底10远离第一金属层11的方向为下方向。

[0054]

如图2a至图3f所示,本实施例还提供一种阵列基板的制作方法,该制作方法用于制作上述阵列基板,该制作方法包括:

[0055]

如图2a和图3a所示,提供基底10,基底10可以由玻璃、石英、硅、丙烯酸或聚碳酸酯等材料制成,基底10也可为柔性基板,用于柔性基板的适当材料包括例如聚醚砜(pes)、聚萘二甲酸乙二醇酯(pen)、聚乙烯(pe)、聚酰亚胺(pi)、聚氯乙烯(pvc)、聚对苯二甲酸乙二醇酯(pet)或其组合。

[0056]

在基底10的上方形成第一金属层11,优选地,第一金属层11设于直接在基底10的上表面。对第一金属层11进行蚀刻,第一金属层11形成图案化的扫描线111和栅极112,栅极112与扫描线111电性连接。其中,第一金属层11可以采用金属例如铜(cu)、银(ag)、铬(cr)、钼(mo)、铝(al)、钛(ti)、锰(mn)、镍(ni)等,或者采用上述金属的组合例如al/mo、cu/mo等。

[0057]

在基底10的上方形成覆盖扫描线111和栅极112的第一绝缘层101,优选地,第一绝缘层101直接设于基底10和第一金属层11的上表面并覆盖扫描线111和栅极112。其中,第一绝缘层101的材料为氧化硅(siox)、氮化硅(sinx)或二者的组合。

[0058]

如图2b和图3b所示,在第一绝缘层101的上方形成金属氧化物半导体层12,优选地,金属氧化物半导体层12直接设于第一绝缘层101的上表面。对金属氧化物半导体层12进行蚀刻,金属氧化物半导体层12形成图案化的有源层121、源极122、漏极123以及像素电极124,源极122和漏极123通过有源层121导电连接,像素电极124与漏极123导电连接。其中,金属氧化物半导体层12优选采用透明金属氧化物半导体材料制成,例如铟锌氧化物(inzno)、铟镓氧化物(ingao)、铟锡氧化物(insno)、锌锡氧化物(znsno)、镓锡氧化物(gasno)、镓锌氧化物(gazno)、铟镓锌氧化物(igzo)或铟镓锌锡氧化物(igzto)等制成。

[0059]

如图2c、图2d和图3c所示,在金属氧化物半导体层12的上表面涂布光刻胶层100,以第一金属层11掩模板,从基底10远离光刻胶层100一侧对光刻胶层100进行光刻处理,光刻胶层100形成图案化的光刻胶图案110,扫描线111、栅极112以及有源层121均与光刻胶图案110相对应。

[0060]

如图2e和图3c所示,以光刻胶图案110为遮挡,从光刻胶图案110远离基底10的一侧对金属氧化物半导体层12进行导体化处理,金属氧化物半导体层12对应源极122、漏极123以及像素电极124的区域被导体化。具体地,采用等离子体对金属氧化物半导体层12进行处理,通过离子轰击、氢(h2)掺杂、氦(he)掺杂以及氩(ar)掺杂等方式对金属氧化物半导体层12进行处理,使得没有被光刻胶图案110覆盖的金属氧化物半导体层12实现导体化,也就是使源极122、漏极123以及像素电极124实现导体化。

[0061]

由于有源层121被光刻胶图案110覆盖住,光刻胶图案110有较好的氢阻挡能力,有利于在对金属氧化物半导体层12进行导体化的处理过程中避免向有源层121中引入氢,导致有源层121被导体化。

[0062]

如图2f和图3d所示,对金属氧化物半导体层12进行导体化处理后,剥离掉光刻胶图案110,使得扫描线111和有源层121露出。

[0063]

如图2g和图3e所示,在金属氧化物半导体层12的上表面形成第二金属层14,优选地,第二金属层14直接设于金属氧化物半导体层12的上表面。对第二金属层14进行蚀刻并形成图案化的数据线141,数据线141直接与源极122导电连接。其中,第二金属层13可以采用金属例如铜(cu)、银(ag)、铬(cr)、钼(mo)、铝(al)、钛(ti)、锰(mn)、镍(ni)等,或者采用上述金属的组合例如al/mo、cu/mo等。

[0064]

本实施例中,对第二金属层14进行蚀刻时还形成图案化的第一连接部142,数据线141与第一连接部142导电连接,第一连接部142完全覆盖住源极122并直接与源极122的上表面相接触。由于第一连接部142与数据线141采用同一层金属层制作而成,第一连接部142的电阻较小,使得第一连接部142完全覆盖住源极122后,第一连接部142和源极122整体上的电阻较小,从而增加源极122的导电性。优选地,第一连接部142在基底10上的投影与有源层121在基底10上的投影部分重叠,使得第一连接部142还覆盖一分部有源层121,以增加源极122和漏极123在沟道处的导通性能。当然,在其他实施例中,对第二金属层14进行蚀刻时还形成图案化的第二连接部143,第二连接部143完全覆盖住漏极123并直接与漏极123的上表面相接触。由于第二连接部143与数据线141采用同一层金属层制作而成,第二连接部143的电阻较小,使得第二连接部143完全覆盖住漏极123后,第二连接部143和漏极123整体上的电阻较小,从而增加漏极123的导电性。当然,第二连接部143在基底10上的投影与有源层121在基底10上的投影部分重叠,使得第二连接部143还覆盖一分部有源层121,以增加源极122和漏极123在沟道处的导通性能。

[0065]

如图2h和图3f所示,在第一绝缘层101的上方形成第二绝缘层102以及在第二绝缘层102上方形成透明导电层15,对透明导电层15进行蚀刻并形成图案化的公共电极151,公共电极151与像素电极124相互绝缘设置。具体地,第二绝缘层102设于第二金属层14、金属氧化物半导体层12以及第一绝缘层101的上表面,第二绝缘层102覆盖住数据线141、第一连接部142、有源层121、漏极123以及像素电极124。公共电极151设于第二绝缘层102的上表面,公共电极151与像素电极124通过第二绝缘层102相互绝缘。当然,在其他实施例中,阵列基板上也可不用设置公共电极151,公共电极151设于彩膜基板20(图9)上,以形成tn或va显示模式。

[0066]

[实施例二]

[0067]

图4是本发明实施例二中阵列基板的截面结构示意图,图5是本发明实施例二中阵列基板去掉公共电极的平面示意图。如图4和图5所示,本发明实施例二提供的阵列基板及制作方法与实施例一(图1至图3f)中的阵列基板及制作方法基本相同,不同之处在于,在本实施例中,第二金属层14包括数据线141、第一连接部142以及第二连接部143,数据线141与第一连接部142导电连接,第一连接部142完全覆盖住源极122并直接与源极122的上表面相接触,第二连接部143完全覆盖住漏极123并直接与漏极123的上表面相接触。由于第一连接部142、第二连接部143与数据线141采用同一层金属层制作而成,第一连接部142和第二连接部143的电阻较小,使得第一连接部142完全覆盖住源极122后,第一连接部142和源极122整体上的电阻较小,第二连接部143完全覆盖住漏极123后,第二连接部143和漏极123整体上的电阻较小,从而增加源极122和漏极123的导电性。优选地,第一连接部142和第二连接部143在基底10上的投影均与有源层121在基底10上的投影部分重叠,使得第一连接部142和第二连接部143均还覆盖一分部有源层121,以增加源极122和漏极123在沟道处的导通性

能。

[0068]

相对于实施例一,本实施的第二金属层14同时形成数据线141、第一连接部142以及第二连接部143,同时增加了源极122和漏极123的导电性。

[0069]

本领域的技术人员应当理解的是,本实施例的其余结构以及工作原理均与实施例一相同,这里不再赘述。

[0070]

[实施例三]

[0071]

图6是本发明实施例三中阵列基板的截面结构示意图,图7a-7f是本发明实施例三中阵列基板的制作方法的截面示意图,图8是本发明实施例三中阵列基板去掉公共电极的平面示意图。如图6和图8所示,本发明实施例二提供的阵列基板及制作方法与实施例二(图4至图5)中的阵列基板及制作方法基本相同,不同之处在于,在本实施例中,有源层121的上表面设有沟道保护层131,沟道保护层131完全覆盖住有源层121,沟道保护层131可以对有源层121起到保护作用,避免外环境光以及后续工艺影响有源层121的性能。

[0072]

优选地,沟道保护层131采用正性光敏材料制成,即沟道保护层131采用与光刻胶相同的材料制成,从而可以进一步简化制成工艺。当然,在其他实施例中,沟道保护层131也可采用普通的绝缘材料制成,例如为氧化硅(siox)、氮化硅(sinx)或二者的组合。

[0073]

本实施例还提供一种阵列基板的制作方法,该制作方法与实施例二中的制作方法基本相同,不同之处在于,在本实施例中,如图7a和7b所示,在金属氧化物半导体层12的上表面涂布光刻胶层100,以第一金属层11掩模板,从基底10远离光刻胶层100一侧对光刻胶层100进行光刻处理,光刻胶层100形成图案化的光刻胶图案110,扫描线111、栅极112以及有源层121均与光刻胶图案110相对应。

[0074]

如图7c所示,以光刻胶图案110为遮挡,从而光刻胶图案110远离基底10的一侧对金属氧化物半导体层12进行导体化处理,金属氧化物半导体层12对应源极122、漏极123以及像素电极124的区域被导体化。具体地,采用等离子体对金属氧化物半导体层12进行处理,通过离子轰击、氢(h2)掺杂、氦(he)掺杂以及氩(ar)掺杂等方式对金属氧化物半导体层12进行处理,使得没有被光刻胶图案110覆盖的金属氧化物半导体层12实现导体化,也就是使源极122、漏极123以及像素电极124实现导体化。

[0075]

由于有源层121被光刻胶图案110覆盖住,光刻胶图案110有较好的氢阻挡能力,有利于在对金属氧化物半导体层12进行导体化的处理过程中避免向有源层121中引入氢,导致有源层121被导体化。

[0076]

如图7d所示,对金属氧化物半导体层12进行导体化处理后,保留光刻胶图案110,使得光刻胶图案110与有源层121对应的区域形成沟道保护层131。

[0077]

如图7e和图8所示,在金属氧化物半导体层12的上表面形成第二金属层14,优选地,第二金属层14直接设于金属氧化物半导体层12的上表面,同时,第二金属层14也覆盖住光刻胶图案110。对第二金属层14进行蚀刻并形成图案化的数据线141、第一连接部142以及第二连接部143,数据线141直接与源极122导电连接,第一连接部142完全覆盖住源极122并直接与源极122的上表面相接触,第二连接部143完全覆盖住漏极123并直接与漏极123的上表面相接触。其中,第二金属层13可以采用金属例如铜(cu)、银(ag)、铬(cr)、钼(mo)、铝(al)、钛(ti)、锰(mn)、镍(ni)等,或者采用上述金属的组合例如al/mo、cu/mo等。

[0078]

如图7f所示,在第一绝缘层101的上方形成第二绝缘层102以及在第二绝缘层102

上方形成透明导电层15,对透明导电层15进行蚀刻并形成图案化的公共电极151,公共电极151与像素电极124相互绝缘设置。具体地,第二绝缘层102设于第二金属层14、金属氧化物半导体层12以及第一绝缘层101的上表面,第二绝缘层102覆盖住数据线141、第一连接部142、有源层121、漏极123以及像素电极124。公共电极151设于第二绝缘层102的上表面,公共电极151与像素电极124通过第二绝缘层102相互绝缘。当然,在其他实施例中,阵列基板也可不用设置公共电极151,公共电极151设于彩膜基板20(图9)上,以形成tn或va显示模式。

[0079]

本实施例中,通过在有源层121的上表面设有沟道保护层131,沟道保护层131和光刻胶层100均采用正性光敏材料,从而使得光刻胶图案110对应有源层121的部分作为沟道保护层131,对有源层121起到保护作用,避免外环境光以及后续工艺影响有源层121的性能,而且还可以简化制作工艺。

[0080]

本领域的技术人员应当理解的是,本实施例的其余结构以及工作原理均与实施例二相同,这里不再赘述。当然,实施例一中也可设置与本实施例中相似的沟道保护层131,除了第二金属层14形成的图案不同以外,其余结构和制作方法均相同。

[0081]

图9是本发明中显示面板的截面结构示意图。如图9所示,本发明还提供一种显示面板,包括上述阵列基板、与阵列基板相对设置的对置基板20以及设于阵列基板和对置基板20之间的液晶层30。对置基板20上设有上偏光片41,阵列基板上设有下偏光片42,上偏光片41的透光轴与下偏光片42的透光轴相互垂直。其中,液晶层30中的液晶分子采用正性液晶分子(介电各向异性为正的液晶分子),在初始状态时,正性液晶分子处于平躺姿态,靠近对置基板20的正性液晶分子的配向方向与靠近阵列基板的正性液晶分子131的配向方向相平行。可以理解地是,阵列基板和对置基板20在朝向液晶层30的一层还设有配向层,从而对液晶层30中的正性液晶分子进行配向。

[0082]

本实施例中,对置基板20为彩膜基板,对置基板20上设有黑矩阵21和色阻层22,黑矩阵21与扫描线111、数据线141、薄膜晶体管以及外围非显示区相对应,黑矩阵21将多个色阻层22间隔开。色阻层22包括红(r)、绿(g)、蓝(b)三色的色阻材料,并对应形成红(r)、绿(g)、蓝(b)三色的子像素。

[0083]

在本文中,所涉及的上、下、左、右、前、后等方位词是以附图中的结构位于图中的位置以及结构相互之间的位置来定义的,只是为了表达技术方案的清楚及方便。应当理解,所述方位词的使用不应限制本技术请求保护的范围。还应当理解,本文中使用的术语“第一”和“第二”等,仅用于名称上的区分,并不用于限制数量和顺序。

[0084]

以上所述,仅是本发明的较佳实施例而已,并非对本发明做任何形式上的限定,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出些许更动或修饰,为等同变化的等效实施例,但凡是未脱离本发明技术方案内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1