一种芯片组件、光器件及组装方法与流程

1.本技术涉及光通信领域,尤其涉及一种芯片组件、光器件及组装方法。

背景技术:

2.随着光通信领域的飞速发展,对光模块速率的要求也不断上升,在5g环境下,其单路的最低速率已经达到50gbps及以上,虽然速率上升,但是光模块集成化、小型化的趋势却越来越明显,因此,也对光模块中的光器件的结构设计提出了更高的要求。但是,当前的光器件在组装过程中出现人为损坏的情况较多,提高了整体的不良率。

技术实现要素:

3.有鉴于此,本技术实施例期望提供一种芯片组件、光器件及组装方法,能有效的改善光器件在组装过程中的不良率。

4.为达到上述目的,本技术实施例的技术方案是这样实现的:

5.一种光器件,包括:电路板;以及芯片组件,所述芯片组件包括底座、盖体以及第一芯片单元;所述底座与所述电路板固定连接,所述第一芯片单元通过所述盖体与所述电路板电性连接;所述盖体扣设在所述底座上以形成容纳空间;所述第一芯片单元布置在所述容纳空间内。

6.进一步地,所述盖体与所述电路板在所述容纳空间外采用金丝键合连接。

7.进一步地,所述底座配置为散热底座。

8.一种芯片组件,用于与上述的电路板配合,所述芯片组件包括:底座,用于与所述电路板固定连接;盖体,用于与所述电路板电性连接;所述盖体扣设在所述底座上以形成容纳空间;以及与所述盖体电性连接的第一芯片单元,所述第一芯片单元布置在所述容纳空间内。

9.进一步地,所述第一芯片单元配置为将电信号转化为光信号。

10.进一步地,所述第一芯片单元布置在所述盖体面向所述容纳空间内的一面上。

11.进一步地,所述盖体包括顶板以及至少两个支撑部,两个所述支撑部设置在所述顶板的两侧;所述支撑部远离所述顶板的一端与所述底座采用胶粘固定,所述第一芯片单元固设在所述顶板面向所述容纳空间的一面上,以使得所述第一芯片单元远离所述支撑部与所述底座的粘接区域。

12.进一步地,所述第一芯片单元包括第一芯片以及第一芯片底板;所述第一芯片设置在所述第一芯片底板的正面;所述第一芯片底板的背面固定在所述盖体面向所述容纳空间内的一面上。

13.进一步地,所述盖体与所述第一芯片底板在所述容纳空间内采用金丝键合连接;所述第一芯片与所述第一芯片底板在所述容纳空间内采用金丝键合连接。

14.进一步地,所述芯片组件包括布置在所述容纳空间内的第二芯片单元,所述第二芯片单元配置为监控所述第一芯片单元的背光。

15.一种组装方法,用于上述的芯片组件的组装,包括:

16.将所述第一芯片单元布置在所述盖体面向所述容纳空间内的一面上;

17.对第一芯片单元与所述盖体进行打线操作;

18.对第一芯片单元与所述盖体进行测高操作;

19.将所述盖体扣设在所述底座上。

20.进一步地,所述将所述第一芯片单元布置在所述盖体面向所述容纳空间内的一面上的步骤之前,还包括:

21.将第一芯片设置在第一芯片底板的正面;

22.对第一芯片与所述第一芯片底板进行打线操作;

23.对第一芯片与所述盖体进行测高操作。

24.本技术实施例的一种芯片组件、光器件及组装方法通过设置芯片组件包括底座、盖体以及第一芯片单元。底座与电路板固定连接,第一芯片单元通过盖体与电路板电性连接。盖体扣设在底座上以形成容纳空间;第一芯片单元布置在容纳空间内使得第一芯片单元的外周有盖体以及底座的保护,在光器件组装过程中,有效的避免第一芯片单元与盖体电性连接的结构部分、以及第一芯片单元本身出现碰伤的情况,从而有效改善了光器件组装过程的不良品率。

附图说明

25.图1为相关技术中光器件的结构示意图,其中省略了光器件的外壳封装,以显示内部电路板与芯片的装配结构;

26.图2为相关技术中电路板与芯片的装配结构示意图;

27.图3为图2的a-a视图;

28.图4为本技术实施例的光器件的结构示意图,其中,省略了光器件的外壳封装,以显示内部电路板与芯片的装配结构;

29.图5为图4的b-b视图;

30.图6为本技术一实施例的芯片组件的结构示意图;

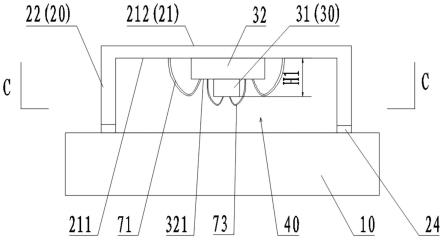

31.图7为图6的c-c视图,其中省略了金丝键合的结构;

32.图8为本技术一实施例的盖体的结构示意图;

33.图9为本技术另一实施例的盖体的结构示意图;

34.图10为另一实施例的光器件的结构示意图;

35.图11为本技术实施例的芯片组件的组装方法;

36.图12为本技术实施例的光器件的组装方法。

具体实施方式

37.需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的技术特征可以相互组合,具体实施方式中的详细描述应理解为本技术的解释说明,不应视为对本技术的不当限制。

38.在本技术实施例的描述中,“上”、“下”、“左”、“右”、“前”、“后”方位或位置关系为基于附图4所示的方位或位置关系,需要理解的是,这些方位术语仅是为了便于描述本技术

和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

39.常规的光器件为tosa(transmitter optical subassembly;光发射器)和rosa(receiver optical subassembly,光接收器),tosa包括能够将输入的电信号转化成光信号发出的激光器芯片;rosa包括能够将输入的光信号装换为电信号输出的光电芯片。在4g通信时代,厂家通常制作单独的tosa以及单独的rosa,用两个光口分别连接光纤传输高速及大容量上下行数据。但是随着5g技术的飞速发展,长距离、大容量的5g场景对上下行的时差提出了很高的要求,如果用单独tosa和rosa分两根光纤传输,上下行光纤长度的区别,光纤本身的不同,会造成传输时间、色散和散射等因素的差别,进而导致长距离5g场景的上下行传输技术出现瓶颈,因此也出现了集tosa和rosa于一体的光器件bosa(bi-directional optical sub-assembly,光发射接收器)。因此,在本技术的各个实施例中,若未说明,则光器件可以是tosa、rosa或者bosa。

40.在相关技术中,如图1至图3所示,光器件的组装过程需要将芯片单元30’先行安装在电路板90’上,再在安装有芯片单元30’的电路板90’上继续耦合连接各种必要的元器件,从而实现光器件的功能。可以理解的是,根据光器件的类型不同,芯片单元30’可以为激光器芯片,也可以是光电芯片。光器件这种组装方式,芯片单元30’裸露在外,易出现人为损坏,例如芯片单元30’碰伤划伤;芯片单元30’与电路板90之间的电路连接可以通过金丝键合实现;在这种组装方式中,金丝键合中连接的金丝71’、72’正常情况为拱形,在组装过程被操作人员或者其他元器件碰撞导致金丝塌陷、金丝断裂等情况,均会导致光器件的不良。

41.本技术实施例提供一种光器件,参考如图4至图9,以及图11和图12所示,光器件包括:电路板90以及芯片组件100。芯片组件100包括底座10、盖体20以及第一芯片单元30。底座10与电路板90固定连接,第一芯片单元30通过盖体20与电路板90电性连接。盖体20扣设在底座10上以形成容纳空间40;第一芯片单元30布置在容纳空间40内以防止第一芯片单元30在光器件的组装过程中出现损伤。

42.本领域技术人员可知,在光器件技术领域,光器件可具备一个独立的封装,电路板90上集成有完成光电信号转换的其他必要元器件。

43.其中,第一芯片单元30与盖体20可以通过金丝键合、铜箔、金属导线等方式实现电性连接,盖体20与电路板90可以通过金丝键合、铜箔、金属导线等方式实现电性连接,从而使得第一芯片单元30能够通过盖体20与电路板90电性连接,实现第一芯片单元30与电路板90之间的电信号传递。

44.盖体20可以通过胶粘、焊接等方式扣设在底座10上以围设形成容纳空间40;容纳空间40可为一个半封闭的空间。

45.第一芯片单元30布置在容纳空间40内。由此使得,第一芯片单元30的外周有盖体20以及底座10的保护,在光器件组装过程中,有效的避免第一芯片单元30本身、以及第一芯片单元30与盖体20电性连接的结构部分(如果两者采用金丝键合,则该结构部分也即是金丝71,如果两者采用铜箔连接,则该结构也即是铜箔)出现碰伤的情况,从而降低了光器件组装过程的不良品率。此外,第一芯片单元30与盖体20、底座10能够作为一个整体,也即是芯片组件100,单独的进行装配以及转运,由于有容纳空间40的保护,芯片组件100在存储转运过程中也不会出现碰伤第一芯片单元30的情况,装配方式更为灵活;无需在光器件的组

装现场对芯片组件100进行组装,避免了现场各种元器件混杂,从而可以避免第一芯片单元30出现损坏的情况;也降低了光器件的组装工艺难度;并且,在芯片组件100组装完成后可以先行对芯片组件100进行测试,防止芯片组件100的不良品流入光器件的组装过程中,最终避免光器件在组装完成后因芯片组件100的不良出现整体的报废。

46.一种可能的实施例,如图5和图6所示,盖体20与第一芯片单元30在容纳空间40内采用金丝键合连接,以实现盖体20与第一芯片单元30的电性连接;盖体20与第一芯片单元30金丝键合的区域位于容纳空间40内,从而可以使得连接盖体20与第一芯片单元30的金丝71获得盖体20以及底座10的保护,避免在光器件的组装过程中被操作人员或者其他元器件碰伤导致金丝塌陷、金丝断裂等情况,从而降低了光器件组装过程的不良品率。

47.一种可能的实施例,如图4和图5所示,盖体20与电路板90在容纳空间40外采用金丝键合连接;通过底座10与电路板90固定连接,实现对芯片组件100的固定,盖体20背离容纳空间40内的一面具有较大的面积可以供金丝键合,从而确保第一芯片单元30能够通过盖体20与电路板90电性连接,实现第一芯片单元30与电路板90之间的电信号传递。

48.相关技术中,参考图1至图3所示,光器件的芯片单元30’设置在底座10’上,底座10’为半导体材料的陶瓷基板,例如氮化铝;底座10’与芯片单元30’采用金丝键合连接以实现两者的电性连接,底座10’与电路板90’金丝键合连接,由此芯片单元30’通过底座10’与电路板90’电性连接,从而完成芯片单元30’与电路板90’之间的电信号传递。考虑到芯片单元30’在进行工作时会散发出大量的热量,光器件通常会包括散热座60’,散热座60’通常为钨铜、铝合金等导热良好的金属制成;散热座60’固定在电路板90’上,底座10’布置在散热座60’上,底座10’与散热座60’之间采用银胶粘接固定,银胶不仅能固定两者,还具有良好的导热性能,芯片单元30’发出的热量经过底座10’传递至散热座60’,由此,在芯片单元30’进行工作的情况下,例如转换光电信号,散热座60’还能够有效的确保芯片单元30’的工作温度正常,最终有效延长光器件的使用寿命。

49.不同于前述实施例的一种结构,如图10所示,光器件包括:电路板90a以及芯片组件100a。芯片组件100a包括底座10a、盖体20a以及芯片单元30a;底座10a与电路板90a固定连接,底座10a为半导体陶瓷基板,芯片单元30a通过底座10a与电路板90a电性连接。盖体20a扣设在底座10a上以形成容纳空间40a;芯片单元30a布置在底座10a面向容纳空间40a的一面上从而使得芯片单元30a布置在容纳空间40a内,可防止芯片单元30a在光器件的组装过程中出现损伤。但考虑到散热,这种设计结构仍然需要在底座10a设计采用钨铜等制成的散热座60a,散热座60a固定在电路板90a上以辅助芯片单元30a进行散热,底座10a依然需要与散热座60a之间采用银胶粘接固定以实现导热;且由于底座10a上需要留出一定的空间给予盖体20a进行扣设以避免影响金丝键合的区域。

50.一种可能的实施例,如图4至图9所示,底座10与电路板90固定连接,第一芯片单元30仅仅通过底座10与电路板90实现固定,第一芯片单元30通过盖体20与电路板90电性连接;由此,底座10配置为散热底座,也即是说,底座10可以是采用钨铜、铝合金等材料制作的底座。在光器件的装配过程中,底座10能够直接嵌入电路板90,替代了散热座60’,通过底座10有效的对第一芯片单元30散热能够有效的确保第一芯片单元30的工作温度正常,延长光器件的使用寿命;且由于第一芯片单元30布置在容纳空间40中,能够减少碰伤,此外,底座10与电路板90固定采用常规的固化胶即可实现固定功能,例如uv光固化胶,以保证两者的

连接强度,并节省了成本昂贵的银胶粘接。

51.一种可能的实施例,如图4至图9所示,芯片组件100包括:用于与电路板90固定连接的底座10,用于与电路板90电性连接的盖体20,以及与盖体20电性连接的第一芯片单元30,盖体20扣设在底座10上以形成容纳空间40。第一芯片单元30配置为将电信号转化为光信号;也即是说,第一芯片单元30为激光器芯片单元,能够将接收到的电信号转化为光信号发出;盖体20上应当具有供光信号射出的通道23,这个通道23可以是开口槽或者通孔,使得布置在容纳空间40内的第一芯片单元30从通道23将光信号射出容纳空间40。

52.一些实施例中,第一芯片单元30也可以配置为将光信号转化为电信号;也即是说,第一芯片单元30为光电芯片单元,能够将接收到的光信号转化为电信号,并通过电路板90传输至其他元器件,以完成相对应的光电传输功能;盖体20上应当具有供光信号射入的通道23,这个通道23可以是开口槽或者通孔,使得布置在容纳空间40内的第一芯片单元30从通道23获取从容纳空间40外射入的光信号。

53.一种可能的实施例,如图4至图9所示,第一芯片单元30布置在盖体20面向容纳空间40内的一面上。例如通过胶粘或者焊接等方式实现第一芯片单元30固定。这样设计一方面使得第一芯片单元30能够布置在容纳空间40内获得保护,避免出现碰伤,另一方面盖体20面向容纳空间40内的一面具有较大的面积,能够方便第一芯片单元30与其通过金丝键合连接。盖体20面向容纳空间40内的一面与背向容纳空间40内的一面可通过铜箔实现连接,盖体20背向容纳空间40内的一面可以通过金丝键合与电路板90连接,由此,布置在容纳空间40内的第一芯片单元30通过盖体20与电路板90实现电性连接。

54.一种可能的实施例,如图4至图8所示,盖体20包括顶板21以及至少两个支撑部22。两个支撑部22设置在顶板21的两侧,整体横截面的形状可以是半口字形也可以半圆弧形,支撑部22沿第一方向相对间隔地设置在顶板21的两侧,由此,可以在两个支撑部22之间形成沿第二方向延伸的通道23,以使得光信号可沿第二方向从容纳空间40射出或者使得光信号沿第二方向射入容纳空间40中。

55.可以理解的是,本技术各个实施例中,参考图8所示,将顶板21的横向宽度作为第一方向,将顶板21的纵向作为第二方向;在其他的一些实施例中,也可以将其他指定的方向作为第一方向与第二方向,只需要确保光信号可沿第二方向从容纳空间40射出或者使得光信号沿第二方向射入容纳空间40中即可。

56.顶板21以及支撑部22通常可采用一体成型连接,两者的连接强度好,能更好的对第一芯片单元30提供保护。顶板21以及支撑部22可为氮化铝等半导体材料制成,方便用于电气连接。此外,顶板21以及支撑部22也可采用分体连接,顶板21采用氮化铝等半导体材料制成陶瓷基板,支撑部22采用钨铜等导热金属进行制作,连接处采用胶粘或者焊接固定即可,以降低加工难度。

57.支撑部22支撑在顶板21与底座10之间,以使得顶板21与底座10相对间隔设置,由顶板21、底座10以及支撑部22围设形成的区域即为容纳空间40。需要注意的是,若第一芯片单元30为其他功能的芯片,无需光信号的的输入或者无需发射光信号,则盖体20上可以不设置通道23,盖体20只需要保护第一芯片单元30即可。

58.支撑部22远离顶板21的一端与底座10采用胶粘固定,该胶粘处24通常采用银胶固定,以形成良好的导热,第一芯片单元30产生的热量经过顶板21传递至支撑部22,再从支撑

部传递至支撑部22;通过底座10有效的对第一芯片单元30散热能够有效的确保第一芯片单元30的工作温度正常,延长光器件的使用寿命。

59.第一芯片单元30通常固设在顶板21面向容纳空间40一面上,也即是将第一芯片单元30布置在顶板21面向底座10的底面211上;以使得第一芯片单元30远离支撑部22与底座10的粘接处24,防止胶水粘接过程中污染第一芯片单元30。顶板21背向底座10的一面为顶面212,顶面212与电路板90可以通过金丝键合实现电连接,实现第一芯片单元30与电路板90之间的电信号传递,顶面212具有较大的面积,因此可以降低金丝键合的工艺难度。

60.一种可能的实施例,如图4至图7所示,第一芯片单元30包括第一芯片31以及第一芯片底板32。第一芯片31设置在第一芯片底板32的正面321;第一芯片底板32的背面(未标出)固定在盖体20面向容纳空间40内的一面上。

61.当第一芯片单元30配置为将电信号转化为光信号;第一芯片31可为激光器芯片,由于芯片通常较小,因此需要先行固定在第一芯片底板32上,以方便后续组装。

62.第一芯片31与第一芯片底板32在容纳空间40内采用金丝键合连接。具体地,第一芯片31设置在第一芯片底板32的正面321,两者可以采用胶粘固定,第一芯片底板32可为氮化铝等半导体材料制成的陶瓷基板;第一芯片31与第一芯片底板32的正面321之间采用金丝键合连接,连接第一芯片31与正面321的金丝73处于容纳空间40内,从而可以在组装完成后获得保护,避免在光器件的组装过程中被操作人员或者其他元器件碰伤导致金丝塌陷、金丝断裂等情况,从而降低了光器件组装过程的不良品率。第一芯片31的发光端(未标出)应对准通道23,以便于将从电路板90传输过来的电信号转化为光信号从通道23发出。

63.盖体20与第一芯片底板32在容纳空间40内采用金丝键合连接,具体地,第一芯片底板32的远离正面321的背面固定在盖体20面向容纳空间40内的一面上,第一芯片底板32的背面布置在顶板21的底面211上,两者可以采用胶粘固定,或者焊接固定,第一芯片底板32的正面321与顶板21的底面211的底面通过金丝键合连接,连接第一芯片底板32与顶板21的金丝71处于容纳空间40内,从而可以在组装完成后获得保护,避免在光器件的组装过程中被操作人员或者其他元器件碰伤导致金丝塌陷、金丝断裂等情况。

64.一种可能的实施例,如图4、图6和图7所示,芯片组件100还包括布置在容纳空间40内的第二芯片单元50。根据第一芯片单元30的功能不同,第二芯片单元50可以为不同功能的芯片。当第一芯片单元30配置为将电信号转化为光信号,则第二芯片单元50可以为背光检测器芯片单元,用于监控第一芯片单元30的背光。第二芯片单元50贴装在顶板21的底面211,第一芯片单元30发出的光信号经由透镜进行光路汇聚,第一芯片单元30漏出的光由第二芯片单元50接受,用以监控第一芯片单元30的工作状态。此外,第二芯片单元50也可以是光路调制器。当第一芯片单元30配置为将光信号转化为电信号,则第二芯片单元50可为跨阻放大器芯片单元等。

65.第二芯片单元50可以包括第二芯片51以及第二芯片底板52。第二芯片51设置在第二芯片底板52的正面(未标出);第二芯片底板52的背面(未标出)固定在盖体20面向容纳空间40内的一面上。第二芯片51与第二芯片底板52在容纳空间40内可采用金丝键合连接,以获得保护防止碰伤。盖体20与第二芯片底板52在容纳空间40内采用金丝键合连接,以获得保护防止碰伤。

66.如图4至图9,以及图11和图12所示,本技术再提供一种组装方法,用于芯片组件

100的组装。

67.组装方法包括:

68.s40、将第一芯片单元30布置在盖体20面向容纳空间40内的一面上。例如通过胶粘或者焊接等方式实现第一芯片单元30固定。

69.s50、对第一芯片单元30与盖体20进行打线操作。本处的打线操作是指的在第一芯片单元30的第一芯片底板32与盖体20的顶板21之间打金线,常用打线机进行,打线操作需要满足拉力测试,打线的长度也有一定的要求,过长过短都会影响实际的性能,例如灵敏度,发射眼图,光模块失效分析就有打线断裂等因素。打线完成可以安排目检,以控制打线质量。连接第一芯片底板32与顶板21的金丝71处于容纳空间40内,从而可以在组装完成后获得保护。

70.s60、对第一芯片单元30与盖体20进行测高操作。本处的测高操作即是指的通过测距仪器测出顶板21的底面211到电路板90的距离h2,以方便计算光器件的中心高度位置。

71.s70、将盖体20扣设在底座10上。盖体20可以通过胶粘、焊接等方式扣设在底座10上以形成芯片组件100。

72.一种可能的实施例,s40步骤之前,还包括:

73.s10、将第一芯片31设置在第一芯片底板32的正面。连接方式可以是胶粘贴片。

74.s20、对第一芯片31与第一芯片底板32进行打线操作。打线操作是指的在第一芯片底板32的正面321与第一芯片31之间打金线,常用打线机进行,打线操作需要满足拉力测试,打线的长度也有一定的要求,连接第一芯片31与正面321的金丝73处于容纳空间40内,从而可以在组装完成后获得保护。

75.s30、对第一芯片31与盖体20进行测高操作。本处的测高操作即是指的通过测距仪器测出第一芯片31到顶板21的底面211的距离h1,以方便计算光器件的中心高度位置。

76.如图4至图9,以及图11和图12所示,本技术再提供一种光器件的组装方法,包括:

77.上述芯片组件的组装方法的步骤,以及;

78.s80、将芯片组件100安装在电路板90上。芯片组件100的底座10与电路板90固定连接,并在盖体20的顶面212与电路板90可以通过金丝键合实现电连接。

79.s90、安装其他组件耦合封装,以完成光器件的组装。

80.本技术提供的各个实施例/实施方式在不产生矛盾的情况下可以相互组合。

81.以上所述仅为本技术的较佳实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1