一种用于PONOLT系统的硅基光电子的收发集成芯片的制作方法

一种用于pon olt系统的硅基光电子的收发集成芯片

技术领域

1.本发明涉及光通信技术领域,尤其涉及一种用于pon(passive optical network,无源光网络)olt(optical line terminal,光线路终端)系统的硅基光电子的收发集成芯片。

背景技术:

2.现有技术中公开一种用于50g以上无源光网络中的局端设备,其包括:插接在系统板上的金手指、50g以上的连续下行发射通道、25g以上的突发上行接收通道和单纤双向bosa(bi-directional optical sub-assembly,双向光组件)。发射通道包括dsp(digital signal processor,数字信号处理器/数字信号处理芯片)、pam4(pulsed amplitude modulation four-level,四阶脉冲幅度调制)驱动单元、核心封装光组件box;dsp接收系统板的两路25g的nrz(non return to zero,非归零) tx(transmitting,发射)信号,并合成一路50g的pam4调制信号;pam4驱动单元接收pam4调制信号以驱动核心封装光组件中的外调制器生成发射的50g pam4的光信号;接收通道包括:同轴封装to(transistor outline,晶体管外形)、la(linear amplifier,线性放大器)和cdr(clock data recovery,时钟数据恢复),同轴封装to接收光信号,并转换为电信号经由la和cdr进行限流整形后通过金手指输入给系统板,由此,上述局端设备能够实现将接入网的下行速率从10g提升到50g,上行速度提升到25g。

3.然而上述的局端设备仅能实现一种速率的提升,无法适应多速率通道的光收发器,特别地,上述的光通道发送和接收是通过同轴封装to和核心封装光组件如bosa光组件实现,其占用空间、成本高,无法实现局端设备的小型化及多速率的需求。

4.鉴于此,本发明提供一种基于硅基光电子集成芯片的多速率的局端模块,有效降低占用体积,且能够适应多速率的场景。

技术实现要素:

5.(一)要解决的技术问题鉴于现有技术的上述缺点、不足,本发明提供一种用于pon olt系统的硅基光电子的收发集成芯片、光引擎、局端模块及于pon olt系统板卡。

6.(二)技术方案为了达到上述目的,本发明采用的主要技术方案包括:第一方面,本发明实施例提供一种用于pon olt系统的硅基光电子的收发集成芯片,所述收发集成芯片位于olt的光引擎中,且实现收发一体的集成芯片,所述收发集成芯片基于olt前端单路、双路或四路的驱动电信号对光信号进行调制,调制后的下行光信号经过光引擎的增益处理后经由光引擎的光接口发射;以及,所述收发集成芯片对光引擎的光接口接收的上行光信号进行光电转换以发送所述olt的位于光引擎外部区域的突发模式接收放大芯片组进行处理。

7.可选地,所述驱动电信号为一路驱动电信号,则调制后的下行光信号为一路下行光信号;所述驱动电信号为两路独立的驱动电信号,则收发集成芯片基于每一路驱动电信号对光信号进行调制,调制后的下行光信号为两路下行光信号;所述驱动电信号为四路独立的驱动电信号,则收发集成芯片基于每一路驱动电信号对光信号进行调制,调制后的下行光信号为四路下行光信号;所述光接口接收的上行光信号为一路上行光信号,则所述收发集成芯片对一路上行光信号进行光电转换并输出一路转换后的电信号;所述光接口接收的上行光信号为两路上行光信号,则所述收发集成芯片对两路上行光信号分别进行光电转换并输出转换后的两路独立的电信号;所述光接口接收的上行光信号为四路上行光信号,则所述收发集成芯片对四路上行光信号分别进行光电转换并输出转换后的四路独立的电信号。

8.可选地,驱动电信号为一路驱动电信号时,所述收发集成芯片包括:硅光耦合器、硅光调制器、硅光合分波器、硅光pin(positive intrinsic negative,正极-绝缘-负极)接收器;所述硅光耦合器接收所述光引擎中激光组件发出的作为下行光源的激光信号,所述下行光源经由光路传输进入到硅光调制器进行调制,所述硅光调制器所述驱动电信号对下行光源进行调制,得到调制后的光信号;调制后的光信号经光路传输至硅光合分波器以输出至所述光引擎,以使光引擎进行增益处理并经所述光接口进行下行传输;以及,经所述光接口接收的上行光信号在光引擎中增益放大后经硅光合分波器进入所述硅光pin接收器进行光电转换以输出。

9.可选地,驱动电信号为两路驱动电信号时,所述收发集成芯片包括:一个硅光耦合器、一个硅基分光器、两个硅光调制器、两个硅光合分波器、两个硅光pin接收器;此收发集成芯片的每个硅光合分波器需支持单下行单上行共两个不同波长光信号的合分波;所述硅光耦合器接收所述光引擎中激光组件发出的作为下行光源的激光信号,所述下行光源经由硅基分光器进行分光处理,形成两路下行光源;每一路下行光源经光路传输进入到各自对应的硅光调制器进行调制,每一个硅光调制器基于一路驱动电信号对该路的下行光源进行调制,得到调制后的一路光信号;调制后的两路光信号分别经光路传输至各自的硅光合分波器以分别输出至所述光引擎,以使光引擎的两个增益组件对两路输出分别进行增益处理并经所述光接口进行两路光信号的下行传输;以及,经所述光接口接收的两路上行光信号在光引擎的两个增益组件中分别进行增益放大后进入各自的硅光合分波器处理后经光路传输至各自的硅光pin接收器进行光电转换,每一个硅光pin接收器输出一路转换后的电信号。

10.可选地,驱动电信号为两路驱动电信号时,所述收发集成芯片包括:两个硅光耦合器、两个硅光调制器、一个硅光合分波器、两个硅光pin接收器;

每一个硅光耦合器接收所述光引擎中对应激光组件发出的作为下行光源的激光信号,两路下行光源分别对应的激光信号波长不同,所述下行光源经由光路传输进入到各自对应的一个硅光调制器进行调制,每一个硅光调制器基于一路驱动电信号对该路的下行光源进行调制,得到调制后的一路光信号;该一路逛信号包括两种波长的下行光源;调制后的两路光信号经光路传输至一个硅光合分波器以输出两路下行光信号至所述光引擎,以使光引擎的一个增益组件对两路输出进行增益处理并经所述光接口进行两路光信号的下行传输;以及,经所述光接口接收的两路上行光信号在光引擎的一个增益组件中进行增益放大后经一路硅光合分波器处理后成为两路上行光信号,每一路上行光信号经光路传输至各自的硅光pin接收器进行光电转换,每一个硅光pin接收器输出一路转换后的电信号。

11.可选地,驱动电信号为四路驱动电信号时,所述收发集成芯片包括:两个硅光耦合器、两个硅基分光器、四个硅光调制器、两个硅光合分波器、四个硅光pin接收器;所述两个硅光耦合器分别接收所述光引擎中两个激光组件发出的作为下行光源的激光信号,且两个激光信号波长不同,所述下行光源经由硅基分光器进行分光处理,形成四路下行光源,其中两两波长一致;每一路下行光源经光路传输进入到各自对应的硅光调制器进行调制,每一个硅光调制器基于一路驱动电信号对该路的下行光源进行调制,得到调制后的一路光信号;调制后的四路光信号分别经光路传输至硅光合分波器,且两路不同波长光信号为一组,一共两组分别通过两个硅光合分波器输出至所述光引擎,以使光引擎的两个增益组件对两组四路光信号输出分别进行增益处理并经所述光接口进行四路光信号的下行传输;以及,经所述光接口接收的四路上行光信号在光引擎的两个增益组件中分别进行增益放大后进入各自的硅光合分波器处理后经光路传输至各自的硅光pin接收器进行光电转换,每一个硅光pin接收器输出一路转换后的电信号。可选地,驱动电信号为四路驱动电信号时,所述收发集成芯片包括:四个硅光耦合器、四个硅光调制器、一个硅光合分波器、四个硅光pin接收器;每一个硅光耦合器接收所述光引擎中对应激光组件发出的作为下行光源的激光信号,且四路激光信号波长不同,所述下行光源经由光路传输进入到各自对应的一个硅光调制器进行调制,每一个硅光调制器基于一路驱动电信号对该路的下行光源进行调制,得到调制后的一路光信号;调制后的四路光信号经光路传输至一个硅光合分波器在空间上合并进入一个片上波导以输出四路下行光信号至所述光引擎,以使光引擎的一个增益组件对四路输出进行增益处理并经所述光接口进行四路光信号的下行传输;以及,经所述光接口接收的四路上行光信号在光引擎的一个增益组件中进行增益放大后耦合进入硅基光电子集成芯片上一个片上波导,并经一路硅光合分波器处理后,依不同波长进入四个片上波导成为四路空间分离的上行光信号,每一路上行光信号经光路传输至各自的硅光pin接收器进行光电转换,每一个硅光pin接收器输出一路转换后的电信号。

12.可选地,所述收发集成芯片还包括:对应光路传输的硅光波导、硅光监测器;

所述硅光波导、硅光监测器用于对光路传输的光信号进行传输和监测。

13.第二方面,本发明还提供一种用于pon olt系统的光引擎,所述光引擎位于采用sfp-dd(small form-factor pluggable-double density,双密度小型可插拔)或sfp-dd112(small form-factor pluggable-double density 112g,单路112g的双密度小型可插拔)封装的olt模块中,并基于olt前端单路、双路或四路的驱动电信号对光信号进行调制和增益处理,以通过光引擎的光接口发射;以及,所述光引擎的光接口接收的上行光信号进行光电转换以发送所述olt的位于光引擎外部区域的突发模式接收放大芯片组进行处理;所述光引擎中设置有第一方面任一所述的硅基光电子的收发集成芯片。

14.可选地,所述光引擎的光接口用于接收上行光信号或发送下行光信号,所述光接口包括:单通道单纤双向的simplex sc(simplex,单纤双向;sc,standard connector标准连接器)接口和/或双通道单纤双向的双simplex lc(lucent connector,朗讯连接器)接口;且所述光接口为采用sfp-dd/sfp-dd112模块封装的接口。

15.可选地,所述光引擎包括:o波段激光器及驱动组件、o波段增益芯片及驱动组件、光接口、金手指阵列;所述o波段激光器及驱动组件作为激光组件产生作为下行光源的激光信号;o波段增益芯片及驱动组件用于对硅基光电子的收发集成芯片输出的光信号进行增益处理,或者对光接口接收的上行光信号进行增益处理;金手指阵列用于传输光引擎与olt中其他组件的电信号/驱动电信号;其中,所述驱动电信号为一路驱动电信号时,所述o波段激光器及驱动组件为一个、o波段增益芯片及驱动组件为一个;所述驱动电信号为两路驱动电信号时,所述o波段激光器及驱动组件为一个、o波段增益芯片及驱动组件为两个;所述驱动电信号为两路驱动电信号时,所述o波段激光器及驱动组件为两个、o波段增益芯片及驱动组件为两个;所述驱动电信号为两路驱动电信号时,所述o波段激光器及驱动组件为两个、o波段增益芯片及驱动组件为一个;所述驱动电信号为四路驱动电信号时,所述o波段激光器及驱动组件为两个、o波段增益芯片及驱动组件为两个;所述驱动电信号为四路驱动电信号时,所述o波段激光器及驱动组件为四个、o波段增益芯片及驱动组件为一个。

16.第三方面,本发明实施例还提供一种基于硅基光电子集成芯片的多速率的局端模块,所述局端模块为采用sfp-dd/sfp-dd112封装的模块,所述局端模块包括:电气接口、具有单/双/四路多速率的速率变换组件、光引擎和突发模式接收放大芯片组;所述电气接口用于实现局端模块与系统板卡之间的电信号传输;所述速率变换组件用于将系统板卡通过所述电气接口传输的具有第一参数的下行电信号进行时钟数据恢复、速率和/或码型的变换处理,得到用于具有第二参数的电信号,该电信号用以施加在光引擎中硅基光电子集成芯片对应的光信号上实现光信号的调

制,并将调制后的下行光信号通过所述光引擎的光接口传输网络端,以及,借助于光引擎的光接口接收的上行光信号经由光引擎中硅基光电子集成芯片的接收转换成电信号;该电信号经突发模式接收放大芯片组和所述电气接口传输至所述系统板卡;所述光引擎中硅基光电子集成芯片为对光信号实现收发一体的收发集成芯片。

17.可选地,所述光引擎中硅基光电子集成芯片为上述第一方面任一所述的用于pon olt系统的硅基光电子的收发集成芯片。

18.可选地,所述光引擎为上述第二方面任一所述的用于pon olt系统的光引擎。

19.可选地,所述电气接口包括:sfp-dd/sfp-dd112封装的印刷电路板的金手指阵列;所述突发模式接收放大芯片组包括:突发模式接收跨阻放大器和突发模式接收线性放大器;所述具有第二参数的电信号为一路电信号时,所述突发模式接收放大芯片组输入输出突发模式电信号为一路,且该路突发模式接收放大芯片组的电信号速率等于或低于具有第二参数的电信号的速率,所述用于具有第二参数的电信号为两路电信号时,所述突发模式接收放大芯片组输入输出突发模式电信号为两路,且两路突发模式接收放大芯片组电信号的速率不高于具有第二参数的电信号的速率;所述用于具有第二参数的电信号为四路电信号时,所述突发模式接收放大芯片组输入输出突发模式电信号为四路,且四路突发模式接收放大芯片组电信号的速率不高于具有第二参数的电信号的速率。

20.可选地,所述电气接口用以实现25/50/100/200g pon olt系统和/或25/50/100/200g epon olt(ethernet passive optical network olt,以太网标准无源光网络olt)系统与局端模块之间的连接,且电气接口包括下述的接口的一种或多种:单路高速电接口、双路高速电接口和四路高速电接口。

21.可选地,速率变换组件包括:数字处理芯片dsp和用于光信号调制的调制驱动组件;所述dsp用于按照光传输设备的参数对所述电气接口传输的单路或双路电信号进行时钟数据恢复、速率和/或码型的映射转换,以得到与光传输设备的参数一致的一路下行电信号,并通过调制驱动组件,得到一路驱动电信号;和/或,速率变换组件包括:双路retimer(重定时器)组件和用于光信号调制的调制驱动组件;所述双路retimer组件用于按照光传输设备的参数对所述电气接口传输的双路电信号进行时钟数据恢复、速率和/或码型的映射转换,以得到与光传输设备的参数一致的两路下行电信号,并通过调制驱动组件,得到两路驱动电信号;和/或,速率变换组件包括:四路retimer组件和用于光信号调制的调制驱动组件;所述四路retimer组件用于按照光传输设备的参数对所述电气接口传输的四路电信号进行时钟数据恢复、速率和/或码型的映射转换,以得到与光传输设备的参数一致的四路下行电信号,并通过调制驱动组件,得到四路驱动电信号。在实际应用中,四路速率可一致,如均可采用4x25gbps、4x50gbps、4x100gbps的速率;或者,在其他实施例中,也可采用两

两一致,如2x25gbps+2x50gbps的组合等,本实施例不对其限定,根据实际需要选择。

22.可选地,dsp包括:retimer组件、gearbox(变速箱)组件、码型转换模块;单路1x25gbps 或1x50gbps nrz或1x100gbps pam4码型输入时,dsp变速箱gearbox组件不工作,单路retimer组件将输入单路电信号进行时钟数据恢复,输出单路1x25gbps nrz或1x50gbps nrz或1x100gbps pam4码型作为下行电信号;双路2x25gbps nrz码型输入时,经过retimer组件、变速箱gearbox组件将双路输入电信号2x25gbps nrz映射转换为单路50gbps nrz码型,以作为输出的一路下行电信号;双路2x25gbps nrz码型输入时,经过retimer组件、变速箱gearbox组件和码型转换模块将双路输入信号2x25gbps nrz映射转换为单路50gbps pam4码型,以作为输出的一路下行电信号;双路2x50gbps nrz码型输入时,经过retimer组件、变速箱gearbox组件将双路输入信号2x50gbps nrz映射转换为单路100gbps nrz码型,以作为输出的一路下行电信号;双路2x50gbps nrz码型输入时,经过retimer组件、变速箱gearbox组件和码型转换模块将双路输入信号2x50gbps nrz映射转换为单路 100gbps pam4码型,以作为输出的一路下行电信号;双路2x 100gbps pam4码型输入时,经过retimer组件、变速箱gearbox组件将双路输入信号2x 100gbps pam4映射转换为单路1x200gbps pam4码型,以作为输出的一路下行电信号。

23.可选地,双路retimer组件包括:retimer芯片;双路2x25gbps nrz码型输入时,retimer芯片用于将电气接口接收的双路的电信号各自进行时钟数据恢复,映射转换为双路的25gbps nrz码型,以作为输出的双路下行电信号;双路2x50gbps nrz码型输入时,retimer用于将电气接口接收的双路的电信号各自进行时钟数据恢复,映射转换为双路的2x50gbps nrz码型,以作为输出的双路下行电信号;双路2x100gbps pam4码型输入时,retimer用于将电气接口接收的双路的电信号各自进行时钟数据恢复,映射转换为双路的2x 100gbps pam4码型,以作为输出的双路下行电信号。

24.可选地,四路retimer组件包括:retimer芯片;四路4x25gbps nrz码型输入时,retimer芯片用于将电气接口接收的四路的电信号各自进行时钟数据恢复,映射转换为四路的25gbps nrz码型,以作为输出的四路下行电信号;四路4x50gbps nrz码型输入时,retimer芯片用于将电气接口接收的四路的电信号各自进行时钟数据恢复,映射转换为四路的4x50gbps nrz码型,以作为输出的四路下行电信号;采用2x25gbps与2x50gbps四路组合输入时,retimer芯片用于将电气接口接收的四路的电信号各自进行时钟数据恢复,映射转换为四路的2x25gbps与2x50gbps nrz码型,以作为输出的四路下行电信号。

25.可选地,调制驱动组件为硅光调制驱动组件,集成在dsp中,或,与retimer芯片集

成在一个组件上。

26.第四方面,本发明实施例还提供一种无源光网络pon olt系统,其特征在于,包括:上述第三方面任一所述的基于硅基光电子集成芯片的多速率的局端模块;所述系统通过所述局端模块与pon网络侧交互。

27.(三)有益效果1)本发明的局端模块olt中的光接口与现有sfp-dd/sfp-dd112 msa协议定义的四种光接口类型(duplex lc(duplex lucent connector,双纤双向朗讯接口)、mpo-12(multi fiber push on 12,12通道多纤芯连接器)、mdc(mini duplex connector,微型双纤双向连接器)、sn(sn connector:sn 连接器))不同,本发明实施例中是采用sfp-dd/sfp-dd112封装协议对olt中simplex sc光接口封装,使得simplex sc光接口支持pon中光信号的单通道单纤双向(bidi)传输;本发明实施例中还可采用相互独立的双通道simplex lc光接口,使得pon olt系统板卡的端口密度进一步加倍,实现更高密度的单纤双向传输特性。

28.2)本发明实施例中,将当前高速小型化sfp-dd/sfp-dd112封装协议应用在于系统板卡交互的电气接口上,以支持下一代pon olt系统的端口高密度、系统高性能需求。本发明实施例中的pon olt系统助力运营商实现局端模块将接入网下行速率从目前xg(s)pon的10gbps提升到25gbps、50gbps、100gbps的更高带宽;上行速率从10gbps提升到25g或50gbps。

29.3)本发明实施例的局端模块应用在pon olt系统中可实现更高的板卡吞吐量。具体地,xg(s)pon olt系统可支持16个10gbps pon olt sfp+光收发器(即局端模块/局端设备)。采用本发明实施例的单路电信号sfp-dd/sfp-dd112封装的电气接口的局端模块,pon olt系统中插入的sfp+光收发器数量不变,而pon olt系统中系统板卡总吞吐量(throughput)提升至xg(s)pon板卡的2.5~20倍。

30.尤其是在双路电信号模式下,一张sfp-dd/sfp-dd112板卡等效32个sfp-dd/sfp-dd11225g/50g/100gpon的光收发器,系统板卡总吞吐量进一步加倍达到xg(s)pon板卡最大吞吐量的5~20x。

31.在四路电信号模式下,一张sfp-dd/sfp-dd112板卡可插入16个sfp-dd/sfp-dd112100g/200g twdm pon光收发器或等效32个sfp-dd/sfp-dd112 50g/25g combo pon光收发器。

32.4)本发明实施例的局端模块可以实现灵活配置下行光信号的速率,兼容多更客户需求,以及兼容不同标准。

33.本发明实施例的pon olt系统支持运营商根据自身客户业务需要、fttx(fiber to the anything,光纤到任意地点)成本诉求、pon mac asic(application specific integrated circuit,专用集成电路)速率和serdes(serializer/deserializer:串行器解串器)速率,灵活配置下行光信号速率及相关服务。例如,可以支持十多种输入输出信号速率组合;本发明实施例的olt/光收发器/局端模块采用的是兼容国内运营商与海外运营商的下一代pon不同速率需求及规划、国内设备商与国外设备商的不同速率需求、多个国际标准组织推进的下一代pon技术标准实现的结构。

34.5)本发明实施例的局端模块具备面向未来应用的开放和可扩展性。具体地,基于以太网速率的sfp-dd/sfp-dd112 msa(multi source agreement 多源协议)增加了对单路

100g pam4输入输出的支持。在未来pon mac(media access control,媒体接入控制层) serdes 升级至100gbps速率时,本发明实施例的局端模块可平滑扩展至支持tdm(time division multiplexing,时分复用)或twdm(time and wavelengthdivision multiplexing,时分与波分复用) 200g(e)pon、100g/50g或50g/25g combo pon(组合无源光网络)。本发明实施例支持的多达13种以上高速率pon类型。

35.6)本发明实施例中的局端模块首次将基于硅基光电子集成芯片的光引擎应用于pon网络光连接。本发明实施例的局端模块中光引擎以集成硅基光电子集成收发芯片(sip)替代传统的光电子混合集成bosa封装,可有效规避采用数十颗分立高速光电芯片进行混合集成封装导致的工艺复杂度、提高产品良率、降低成本、降低光收发器总功耗、提升产品可靠性;并具有高性能、高集成度、高可靠性、适合小型化封装等特点,适用于未来30年更高性能更高端口密度pon olt系统。

36.7)本发明实施例中局端模块所应用的硅基光电子集成芯片,其采用收发一体集成芯片方式实现,其中接收端采用低成本高性能gesi pin接收器,相比于传统pon采用apd(avalanche photo diode,雪崩光电二极管)接收器,pin接收机成本低、良率高、与发射端硅光工艺硅基mz调制器工艺全兼容,可利用现有成熟的硅光工艺生产线一次流片即实现收发一体化集成芯片;无需升级现有硅光产业的加工制造设备和精度即能完成关键硅光集成芯片的生产制造。

37.8)局端模块中,与sip集成的o波段增益芯片对局端模块(即光收发器)的发射侧大功率光信号和接收侧小功率光信号同时进行放大;针对gesi pin自身接收灵敏度不如apd接收灵敏度高且pon上行信号经长距传输可能已衰减至低于pin接收器灵敏度的缺陷,本发明的局端模块采用集成o波段增益芯片(gain chip)放大接收信号以满足锗硅 pin接收器自身灵敏度要求。即,采用pin+gain chip集成方式替代传统的apd,并应用于下一代pon光网络,是兼顾满足技术标准、优化光收发器光引擎成本、兼容现有成熟硅光工艺等多因素综合考虑的结果。

38.综上,本发明实施例中的无源光网络pon采用的olt局端设备支持小型化的sfp-dd/sfp-dd112封装,有效支持下一代olt系统设备的端口高密度、高性能需求。相应地,在pon olt系统中可允许保持现有一张pon板卡16个可插拔光收发器端口的构型,板卡端口密度不变,而板卡吞吐量提升至当今10gpon板卡的2.5~20x。进一步地,本发明实施例中sfp-dd/sfp-dd112电气接口的双排金手指分布可向下兼容sfp28/sfp56/sfp112的单排金手指,还可灵活重定义其金手指阵列使之兼容两组combo pon,从而实现了多速率通道的兼容。

附图说明

39.图1至图3分别为本发明实施例中硅基光电子的收发集成芯片的示意图;图4至图6分别为本发明实施例中的光引擎的示意图;图7为现有技术中sfp-dd/sfp-dd112 msa定义的光接口类型的示意图;图8为本发明实施例中使用的单通道simplex sc光接口和双通道simplex lc接口的示意图;图9至图11为本发明实施例中局端模块的结构示意图;图12至图14为局端模块所应用的pon olt系统的架构示意图;

50g-epon相似挑战外,在满足24.8832gbps、49.7664gbpsnrz速率要求的pcs(physical coding sublayer:物理编码子层)、pma、pmd层电芯片供应方面目前几乎是零,需重新开发。

44.在gpon和xg(s)pon时代,sfp(small form-factor pluggable,小型化可插拔)及sfp+是光收发器采用的典型封装方式,该封装方式允许一张olt板卡容纳16个光收发器。此外,当前高密度高性能olt系统机框可插入17张甚至更多这样的板卡。行业尚未针对下一代更高性能、更高密度olt系统采用何种封装的光收发器达成共识。而过去10年光通信网络技术及应用发展最快的板块是超大规模数据中心(hyper scale data center)。源于支持数据中心内高密度高性能低功耗低成本光互连,新一代基于sfp的sfp-dd/sfp-dd112 msa协议定义了四种光纤接口类型(duplex lc(如图7中(a)所示)、mpo-12(如图7中(b)所示)、mdc(如图7中(d)所示)、sn(如图7中(c)所示)。遵循该多源协议的sfp-dd/sfp-dd112光收发器可灵活支持电口单(1x)或双(2x)路25g nrz、56g pam4(28gbaud)、112g pam4(56gbaud)等serdes速率和光口1x25gbps至2x100gbps以太网速率。

45.本发明涉及光通信网络采用的是下一代无源光网络技术,本发明实施例的光收发器(optical line terminal,olt)即局端模块中采用sfp-dd/sfp-dd112封装、硅基光电子收发集成芯片silicon photonics(sip)和数字信号处理芯片dsp(或retimer)、光接口采用单通道simplex sc接口(如图8中的(a)所示)或双通道simplex lc接口(如图8中的(b)所示),实现下行25g/50g/100g/200gbpsnrz 或 pam4信号,上行突发模式25g/50g/100gbps nrz 或 pam4信号、支持下一代高性能高密度25g(s)pon multi source agreement(msa:多源协议)、itu-t 9804.3 50gpon、ieee 802.3ca(2020)50g-epon等标准协议,并面向未来100g/200gpon应用进行扩展。本发明的sfp-dd/sfp-dd112电气接口可采用单路高速电信号收发,可采用双路高速电信号收发,也可借用combo pon对sfp+单排金手指重定义以支持双路高速电信号方式,重新定义sfp-dd/sfp-dd112双排金手指以支持总共四路高速电信号收发,且该四路高速信号可采用同一速率,适用100g/200g twdm(time and wavelength division multiplexing,时分与波分复用) pon;也可两路不同速率为一组共两组,实现双通道combo pon。如一路50g与一路25g为一组,本发明可在sfp-dd/sfp-dd112光收发器上实现双通道50g/25g combo pon。

46.本发明实施例中的下行是指发射tx,上行是指接收rx,用于传输光信号的接口均为光接口。本实施例的局端模块即为olt、olt收发器等,本发明实施例的描述中单路指一路光信号或电信号,双路指两路光信号或电信号,四路指四路光信号或电信号;本发明单通道指光引擎光接口为一个光纤接口,此接口可以同时收发最少两路不同波长的光信号;双通道指光引擎光接口为两个光纤接口,每接口可以同时收发最少两路不同波长的光信号。

47.实施例一本发明实施例提供一种用于pon olt系统的硅基光电子的收发集成芯片,所述收发集成芯片位于olt的光引擎中,且实现收发一体的集成芯片,所述收发集成芯片基于olt前端单路、双路或四路的驱动电信号对光信号进行调制,调制后的下行光信号经过光引擎的增益处理后经由光引擎的光接口发射;以及,所述收发集成芯片对光引擎的光接口接收的上行光信号进行光电转换以发送所述olt的位于光引擎外部区域的突发模式接收放大芯片组进行处理。

48.本实施例中的硅基光电子的收发集成芯片可为采用一次流片工艺制成的包括有

硅光耦合器、硅光调制器、硅光合分波器、硅光pin接收器的收发集成一体的芯片,其在实际的光路传输中还对应有硅光波导、硅光监测器等组件,具体可参照图1至图3、图15、图16所示。

49.在具体应用中,收发集成芯片接收的驱动电信号为一路驱动电信号,则调制后的下行光信号为一路下行光信号;收发集成芯片接收的驱动电信号为两路独立的驱动电信号,则收发集成芯片基于每一路驱动电信号对光信号进行调制,调制后的下行光信号为两路下行光信号;所述光接口接收的上行光信号为一路上行光信号,则所述收发集成芯片对一路上行光信号进行光电转换并输出一路转换后的电信号;所述光接口接收的上行光信号为两路上行光信号,则所述收发集成芯片对两路上行光信号分别进行光电转换并输出转换后的两路独立的电信号。

50.所述驱动电信号为四路独立的驱动电信号,则收发集成芯片基于每一路驱动电信号对光信号进行调制,调制后的下行光信号为四路下行光信号;相应地,所述光接口接收的上行光信号为四路上行光信号,则所述收发集成芯片对四路上行光信号分别进行光电转换并输出转换后的四路独立的电信号。

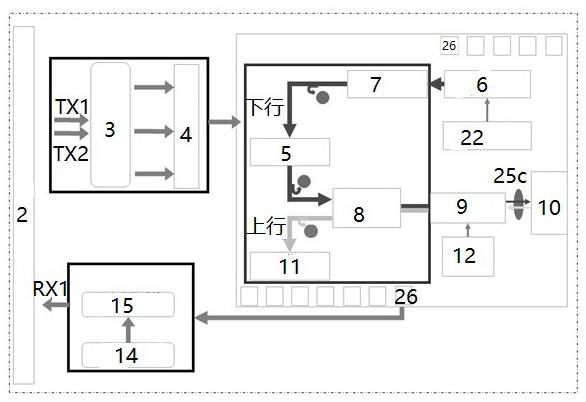

51.如图1所示,本实施例的硅基光电子的收发集成芯片a1可包括:硅光耦合器7、硅光调制器5、硅光合分波器8、硅光pin接收器11;针对下行信号的传输,所述硅光耦合器7接收所述光引擎a2中激光组件发出的作为下行光源的激光信号,所述下行光源经由光路传输进入到硅光调制器5进行调制,所述硅光调制器5所述驱动电信号对下行光源进行调制,得到调制后的光信号;调制后的光信号经光路传输至硅光合分波器8以输出至所述光引擎a2,以使光引擎进行增益处理并经所述光接口进行下行传输;针对上行信号的传输,经所述光接口接收的上行光信号在光引擎a2中增益放大后经硅光合分波器8进入所述硅光pin接收器11进行光电转换以输出。

52.在图1所示的硅基光电子的收发集成芯片可实现一路驱动电信号的调制处理,也是本实施例中核心创新的基本组成单元。另外,图1中光传输过程中也设置有硅光监测器即硅光芯片片上光监测器如20a、20b、20c,该监测器和现有光传输的监测器功能一致,本技术中是集成在收发集成芯片上实现光传输。另外,硅光波导即片上波导21a、21b、21c和21d也是和现有光波导功能一致,本实施例中集成在收发集成芯片上实现光传输。

53.在另一种可能的实现方式,如图2所示,本实施例的硅基光电子的收发集成芯片a1可包括:一个硅光耦合器7、一个硅基分光器24、两个硅光调制器5、两个硅光合分波器8、两个硅光pin接收器11;针对下行的两路驱动电信号,硅光耦合器7接收所述光引擎a2中激光组件发出的作为下行光源的激光信号,所述下行光源经由硅基分光器24进行分光处理,形成两路下行光源;每一路下行光源经光路传输进入到各自对应的硅光调制器5进行调制,每一个硅光调制器5基于一路驱动电信号对该路的下行光源进行调制,得到调制后的一路光信号;此时两路下行光源的波长是一致的,图2中示出的是一个激光组件产生作为下行光源的激光信号,经由硅基1:2分光器分为两路光信号。

54.调制后的两路光信号分别经光路传输至各自的硅光合分波器8以分别输出至所述光引擎a2,以使光引擎a2的两个增益组件对两路输出分别进行增益处理并经所述光接口进行两路光信号的下行传输。

55.针对上行的光信号,经所述光接口接收的两路上行光信号在光引擎的两个增益组件中分别进行增益放大后进入各自的硅光合分波器处理后经光路传输至各自的硅光pin接收器进行光电转换,每一个硅光pin接收器输出一路转换后的电信号。

56.图2中的硅基光电子的收发集成芯片可应用速率方面采用时分复用方式的itu-t 50gpon、未来的100gpon,以及采用itu-t pon速率的25g(s)pon msa协议的各设备中,并通过硅光分光器实现在图1基础上的两个独立光学通道,助力光引擎实现双通道的单纤双向传输。

57.在第三种可能的实现方式,如图3所示,硅基光电子的收发集成芯片包括:两个硅光耦合器7、两个硅光调制器5、一个硅光合分波器8、两个硅光pin接收器11;针对下行的两路驱动电信号,每一个硅光耦合器7接收所述光引擎a2中对应激光组件发出的作为下行光源的激光信号,此时,各路对应的激光信号波长不一样。图3中存在两个激光组件,每一激光组件发出一个波长的激光信号,两路激光组件可发出两个波长的激光信号如λ

ds0

和λ

ds1

。

58.每一路的下行光源经由光路传输进入到各自对应的一个硅光调制器5进行调制,每一个硅光调制器5基于一路驱动电信号对该路的下行光源进行调制,得到调制后的一路光信号;调制后的两路光信号经光路传输至一个硅光合分波器8以输出两路下行光信号至所述光引擎a2,以使光引擎的一个增益组件对两路输出进行增益处理并经所述光接口进行两路光信号的下行传输。

59.针上行的两路驱动电信号,经所述光接口接收的两路上行光信号(该光信号可以是波长不同的光信号,如上行λ

us0

和上行λ

us1

)在光引擎的一个增益组件中进行增益放大后经一路硅光合分波器处理后成为两路上行光信号,每一路上行光信号经光路传输至各自的硅光pin接收器进行光电转换,每一个硅光pin接收器输出一路转换后的电信号。

60.具体地,基于图3所示的结构,ieee 50g-epon 2x25gbps信号速率和nrz编码,并采用o波段双下行波长和双上行波长方式实现 2x25gbps总共50gbps的收发传输,涉及共四个波长的信号:1342+2nm、1358+2nm、1270+10nm、1300+10nm。这四个波长可通过一个增益芯片放大,无需在空间上分成两路通过两个增益芯片分别放大,光引擎设计更简洁。特别地,上行光信号的波长和下行光信号的波长不同,故,在图3中采用不同深度的线条示出。

61.基于上述的图1至图3的收发集成芯片的结构,任意光路传输中还设置有用于光路传输的硅光波导(如各图中示出的21a、21b、21c、21d等片上波导)、硅光监测器(如各图中示出的20a、20b、20c、20d等硅光芯片上的光监测)。本实施例的硅光波导、硅光监测器用于对光路传输的光信号进行传输和监测。硅光片上光监测:监测片上各器件节点光信号,硅光片上波导:用于在硅基光电子集成芯片上实现高速光信号传输。

62.本实施例局端模块所应用的硅基光电子集成芯片,其采用收发一体集成芯片方式实现,其中接收端采用低成本高性能锗硅 pin接收器,相比于传统pon采用apd接收器,pin接收机成本低、良率高、与发射端硅光工艺硅基mz调制器工艺全兼容,可利用现有成熟的硅

光工艺生产线一次流片即实现收发一体化集成芯片;无需升级现有硅光产业的加工制造设备和精度即能完成关键硅光集成芯片的生产制造。

63.在第四种可能的实现方式中,本实施例还提供一种针对四路驱动电信号的收发集成芯片,如图15所示的大矩形框内的结构,硅基光电子的收发集成芯片架构用于双通道100g/200g epon olt 光收发器或双通道 50g/25g combo pon,其具有两个下行波长、两个上行波长、双通道simplex lc 接口、两个增益芯片、两个激光器。具体地,该收发集成芯片包括:两个硅光耦合器、两个硅基分光器、四个硅光调制器、两个硅光合分波器、四个硅光pin接收器;两个硅光耦合器分别接收所述光引擎中两个激光组件发出的作为下行光源的激光信号(两激光信号波长不一样,即图15中λ

ds0

和λ

ds1

波长不同,存在两组λ

ds0

和两组λ

ds1

),所述下行光源经由硅光分光器进行分光处理,形成四路下行光源,其中两两波长一致;特别说明的是,调制信号也是四组,tx1至tx4。此收发集成芯片的每个硅光合分波器需支持两下行两上行共四个不同波长光信号的合分波。

64.每一路下行光源经光路传输进入到各自对应的硅光调制器进行调制,每一个硅光调制器基于一路驱动电信号对该路的下行光源进行调制,得到调制后的一路光信号;调制后的四路光信号分别经光路传输至硅光合分波器,且两路不同波长光信号为一组,一共两组分别通过两个硅光合分波器输出至所述光引擎,以使光引擎的两个增益组件对两组四路光信号输出分别进行增益处理并经所述双通道simplex lc光接口进行四路光信号的下行传输;以及,经所述双通道simplex lc光接口接收的四路上行光信号分为两组,每组由两路上行波长为λ

us0

和λ

us1

的光信号组成。在光引擎的两个增益组件中分别进行增益放大后进入各自的硅光合分波器处理后经光路传输至各自的硅光pin接收器进行光电转换,每一个硅光pin接收器输出一路转换后的电信号(如rx1至rx4(receiving 接收))。

65.也就是说,驱动电信号为四路独立的驱动电信号,则收发集成芯片基于每一路驱动电信号对光信号进行调制,调制后的下行光信号为四路下行光信号;相应地,在光接口接收的上行光信号为四路上行光信号,则收发集成芯片对四路上行光信号分别进行光电转换并输出转换后的四路独立的电信号。

66.在第五种可能的实现方式中,本实施例还提供一种针对四路驱动电信号的收发集成芯片,如图16所示的大矩形框的结构,硅基光电子的收发集成芯片架构用于 100g/200g twdm-pon olt 光收发器,其可具有四个下行波长、四个上行波长、一个simplex sc 接口、一个增益芯片、四个激光器。具体地,该收发集成芯片包括:四个硅光耦合器、四个硅光调制器、一个硅光合分波器、四个硅光pin接收器;每一个硅光耦合器接收所述光引擎中对应激光组件发出的作为下行光源的激光信号,所述下行光源经由光路传输进入到各自对应的一个硅光调制器进行调制,每一个硅光调制器基于一路驱动电信号对该路的下行光源进行调制,得到调制后的一路光信号;调制后的四路光信号经光路传输至一个硅光合分波器合并进入一个片上波导以输出四路下行光信号至所述光引擎,以使光引擎的一个增益组件对四路输出进行增益处理并经所述光接口进行四路光信号的下行传输。需要说明的是,因为光引擎中使用四个激光

器,其产生四个下行光波长,λ

ds0

、λ

ds1

、λ

ds2

、λ

ds3

。此收发集成芯片的硅光合分波器需支持四下行四上行共八个不同波长光信号的合分波。

67.当然,经所述光接口接收的四路上行光信号在光引擎的一个增益组件中进行增益放大后经一路硅光合分波器处理后依不同波长进入四个不同片上波导成为空间上分离的四路上行光信号(如图16中的λ

us0

、λ

us1

、λ

us2

、λ

us3

),每一路上行光信号经光路传输至各自的硅光pin接收器进行光电转换,每一个硅光pin接收器输出一路转换后的电信号。

68.本实施例的局端模块中光引擎以集成硅基光电子集成收发芯片(sip)替代传统的光电子混合集成bosa封装,可有效规避采用数十乃至上百颗分立高速光电芯片进行混合集成封装导致的工艺复杂度、提高产品良率、降低成本、降低光收发器总功耗、提升产品可靠性;并具有高性能、高集成度、高可靠性、适合小型化封装等特点,适用于未来30年更高性能更高端口密度pon olt系统。

69.由此,使得使用上述收发集成芯片的局端模块对应的板卡,可在四路电信号模式下,基于sfp-dd/sfp-dd112封装的一张板卡可插入16个sfp-dd/sfp-dd112100g或200g twdm pon光收发器或等效32个sfp-dd/sfp-dd112 100g/50g 或50g/25g combo pon光收发器,提高吞吐量,实现灵活配置下行光信号的速率,兼容多更客户需求,以及兼容不同标准。

70.实施例二本发明实施例提供一种用于pon olt系统的光引擎,其特征在于,所述光引擎位于采用sfp-dd/sfp-dd112协议的olt模块即光收发器中,并基于olt前端单路、双路或四路的驱动电信号对光信号进行调制和增益处理,以通过光引擎的光接口发射;以及,所述光引擎的光接口接收的上行光信号进行光电转换以发送所述olt的位于光引擎外部区域的突发模式接收放大芯片组进行处理;本实施例中的光引擎中设置有实施例一种任意描述的硅基光电子的收发集成芯片(如图1至图3、图15和图16所示)。

71.该收发集成芯片基于olt前端单路或双路的驱动电信号对光信号进行调制,调制后的下行光信号经过光引擎的增益处理后经由光引擎的光接口发射;以及,所述收发集成芯片对光引擎的光接口接收的上行光信号进行光电转换以发送所述olt的位于光引擎外部区域的突发模式接收放大芯片组进行处理。

72.在本实施例中,光引擎以集成硅基光电子集成收发芯片(sip)替代传统的光电子混合集成bosa封装,可有效规避采用多颗分立高速光电芯片进行混合集成封装导致的工艺复杂度、提高产品良率、降低成本、降低光收发器总功耗、提升产品可靠性;具有高性能、高集成度、高可靠性、适合小型化封装等特点,适用于未来30年更高性能更高端口密度pon olt系统。

73.在实际应用中,本实施例光引擎a2中的光接口可用于接收上行光信号或发送下行光信号,例如,光接口可包括:单通道单纤双向的simplex sc接口和/或双通道单纤双向传输的双simplex lc接口;如图8所示。

74.且所述光接口为采用sfp-dd/sfp-dd112模块封装的接口。

75.可理解的是,当前光接口与现有sfp-dd/sfp-dd112 msa协议定义的四种光接口类型(duplex lc、mpo-12、mdc、sn,如图7所示)不同,本实施例中是采用sfp-dd/sfp-dd112封装协议对olt中simplex sc光接口封装,使得simplex sc光接口支持pon中光信号的单通道单纤双向(bi-direction,简称bidi)传输,同时本实施例中还可采用sfp-dd/sfp-dd112封

装协议对双通道simplex lc光接口封装,使得双通道simplex lc光接口支持多端口高密度pon olt系统单纤双向传输特性。

76.图4至图6中所示的光接口为单通道simplex sc或双通道simplex lc(bi-direction)光接口。双通道simplex lc pon光收发器的优点是支持更高密度更高性能的olt系统:在维持pon mac serdes速率前提下,可使pon板卡总吞吐量相比单通道bidi pon板卡总吞吐量加倍。原一张pon板卡支持16端口sfp系列pon olt光收发器,现在相当于可容纳32个高速pon收发链路。当pon mac serdes速率未来升级到100gbps(pam4)时,此方案可平滑支持双端口2x100gpon。

77.具体地,参见图4至图6所示,本实施例中光引擎a2主要包括:o波段激光器及驱动组件(如o波段大功率半导体激光器6、大功率半导体激光器驱动器22)、o波段增益芯片及驱动组件(o波段增益芯片9、soa驱动器12)、光接口(如simplexsc光接口10)、金手指阵列26;在光引擎a2的信号发送和接收过程中,o波段激光器及驱动组件作为激光组件产生作为下行光源的激光信号;o波段增益芯片及驱动组件用于对硅基光电子的收发集成芯片输出的光信号进行增益处理,或者对光接口接收的上行光信号进行增益处理;金手指阵列用于传输光引擎与olt中其他组件的电信号/驱动电信号。

78.如图4所示,olt前端的驱动电信号为一路驱动电信号时,所述o波段激光器及驱动组件为一个、o波段增益芯片及驱动组件为一个;此单路激光器入射单路输出的方式,可用于25g(s)pon、itu-t 50gpon,或未来更高速率的单路100gpon。

79.如图5所示,olt前端的驱动电信号为两路驱动电信号时,所述o波段激光器及驱动组件为一个、o波段增益芯片及驱动组件为两个;此单路激光器入射双路输出的方式是将一路光源信号在硅光芯片上以1:2方式分为两路独立光信号,用于密度加倍的25g(s)pon、itu-t 50gpon,或未来更高速率的单路100g pon。

80.图5中光引擎可用一个大功率半导体激光器在sip芯片上通过硅基分光器24,即硅基1:2分光器/1:2分光器将信号分成两路,并在片上分别实现信号高速调制、合分波、发射、接收。为更好的示出光传输过程,在图5中示出微透镜25a和25b,其实现增益处理的光信号传输至光接口。图5和图6中对上行和下行光信号传输的过程分别采用弯曲箭头示出各自的片上光导即在光信号传输中均对应有各自的片上波导,以及各自光监测器20a至20b,如实心的圆圈示出的结构。

81.如图6所示,olt前端的驱动电信号为两路驱动电信号时,所述o波段激光器及驱动组件为两个(如图6中的一个大功率半导体激光器驱动器、用于发出λ

ds0

激光波长的第一个o波段大功率激光器和用于发出λ

ds1

激光波长的第二个o波段大功率激光器)、o波段增益芯片及驱动组件为一个,及一个微透镜25。图6中光引擎的光接口也是接收两个波长光信号,经过硅光合分波器之后分为上行光信号λ

us0

和上行光信号λ

us1

进入各自的硅光pin接收器。

82.特别说明的是,图6所示的光引擎接收的调制信号也是两个,如图6中所示的tx1和tx2。

83.此时,光引擎所属的olt光收发器可用于基于2x25g的ieee 50g-epon系统。当两路驱动电信号速率不一样时,如一路50gbps,另一路25gbps,可实现50gpon/25g combo pon。进一步地,这两个不同速率电信号可通过sfp-dd/sfp-dd112光收发器金手指阵列的单排实现:每排各设置一对25gbps和50gbps信号;也可通过双排分别实现:第一排金手指阵列安排

两路25gbps信号、第二排金手指阵列安排两路50gbps。更进一步,基于这样的2x25gbps与2x50gbps电信号组合,结合图15和图16的硅光集成芯片,可以在一个sfp-dd/sfp-dd112光收发器实现两组50g/25g的 combo pon。

84.图6所示的结构对光电芯片封装的集成度提出了更高的要求,相比图4所示的单通道光引擎需多集成一套高速光电芯片,在sfp有限空间下的集成度更高。而图15和图16所示结构的集成度比图6所示集成度更提高了至少一倍。本实施例中,利用硅基光电子集成sip技术可在一块小面积硅芯片上集成多种多粒(数十至上百颗)硅(锗)器件、光耦合器、高速调制器、合分波器、光互连波导、高速pin接收器、1:2光功率分光器、片上光功率动态监测器等,适合面向高性能、高密度、低功耗下一代pon应用的sfp-dd/sfp-dd112小型化封装。

85.本实施例在仅使用dsp的retimer功能或仅使用独立retimer芯片时,光收发器可支持基于以太网速率的ieee 802.3 ca 50g-epon。该标准基于双波长25g 以实现50g。此情况两路分别采用不同波长,下行波长分别为1342nm+2nm和1358nm+2nm,光引擎集成不同波长激光器,双激射波长通过硅光耦合器进入sip芯片。此实施例中不使用1:2分光器,且接收端波长分别为为1270nm+10nm和1300+10nm。具体实现过程中不同波长的收发带来设计、工艺、封装复杂性,可以有效地通过硅基光电子集成芯片方式解决。当双路电信号速率不一致时,本实施例可用于支持combo pon:如当两路电信号速率分别为50gbps和25gbps时,此光收发器可支持未来50g/25g combo pon。当serdes速率升级到28gbaud(56g pam4)或56gbaud(112g pam4)速率时,本实施例的光收发器可平滑支持未来单端口双波长100g-epon或200g-epon。

86.在其他的拓展实施例中,olt前端的驱动电信号为两路驱动电信号时,所述o波段激光器及驱动组件为两个、o波段增益芯片及驱动组件为两个;即双入射双输出的结构。

87.当然,在驱动电信号为四路驱动电信号时,所述o波段激光器及驱动组件为两个、o波段增益芯片及驱动组件为两个,如图15所示。

88.所述驱动电信号为四路驱动电信号时,所述o波段激光器及驱动组件为四个、o波段增益芯片及驱动组件为一个。如图16所示。

89.上述各结构可根据实际的需要进行调整。

90.结合图4至图6所示出的结构可知,硅光调制器5,高速调制来自硅光耦合器进入硅光芯片的cw激光信号,并将高速调制光信号经硅光片上波导发送至硅光合分波器8。

91.o波段大功率半导体激光器6:输出满足协议波长要求的发射端激光信号;硅光耦合器7:用于将o波段大功率半导体激光器发生的激光信号耦合至收发集成芯片a1;硅光合分波器8:硅光集成片上双波滤波器(合分波器):来自硅光调制器5和电气接口2的发射信号经此耦合进入o波段增益芯片9;o波段增益芯片9:发射(下行λ

ds

)和接收(上行λ

us

)不同波长的o-波段光信号经此增益芯片同时被放大。其中下行λ

ds

通过自由空间及微透镜耦合至sfp-dd光收发器的simplexlc光接口10,上行λ

us

通过自由空间及透镜耦合至o波段增益芯片9;simplex lc光接口10:下行λ

ds

经此接口耦合进入传输光纤;上行λ

us

经此接口进入收发器并通过自由空间及透镜(如微透镜25c)耦合至硅光合分波器8。

92.硅光pin接收器11:下行λ

ds

经片上波导进入此pin接收器;

soa(gain chip)驱动器12:设置o波段增益芯片9的工作点;微型tec控制器(图中未标出):用于实现微型温度控制,将sip温度控制在一定范围,防止高温下o波段大功率半导体激光器性能下降、硅光合分波器性能随温度漂移。

93.大功率半导体激光器驱动器22:用于设置o波段大功率半导体激光器的最优工作点。

94.上述支持pon应用的硅光耦合器、硅光合分波器、硅光调制器、硅光pin接收器、片上监测器、片上波导是通过一次流片在硅基材料上实现多种功能器件的硅基光电子单片集成,大大提升了高速光电子芯片的集成度,提高了可靠性和生产良率;而o波段cw大功率半导体激光器、o波段增益芯片是通过异质集成方式与sip(silicon photonics,硅基光电子集成芯片)实现光耦合。

95.当下行电信号为25gbps时,与上行突发模式25gbps构组成对称单通道25g(s)pon工作模式,可支持海外设备商(如nokia)牵头的25g(s)pon 多源协议,并适用于大型海外运营商(at&t等)的下一代高速pon网络;通过2:1 gearbox(速率变换组件)使能采用25g pon mac的海外设备商和运营商在无需升级mac及serdes速率的情况下,平滑实现pmd层支持50g(s)pon。当下行50gbps时,与上行25gbps(或50gbps)构成50g(s)pon工作模式,支持itu-t 50 gpon标准和国内三大运营商选取的下一代高速pon技术路径。

96.实施例三本发明实施例提供一种基于硅基光电子集成芯片的多速率的局端模块,该局端模块为采用sfp-dd/sfp-dd112封装的模块,所述局端模块包括:电气接口、具有单/双/四路多速率的速率变换组件、光引擎和突发模式接收放大芯片组;所述电气接口用于实现局端模块与系统板卡之间的电信号传输;所述速率变换组件用于将系统板卡通过所述电气接口传输的具有第一参数的下行电信号进行时钟数据恢复、速率和/或码型的变换处理,得到用于具有第二参数的电信号,该电信号用以施加在光引擎中硅基光电子集成芯片对应的光信号上实现光信号的调制,并将调制后的下行光信号通过所述光引擎的光接口传输网络端,以及,借助于光引擎的光接口接收的上行光信号经由光引擎中硅基光电子集成芯片的接收转换成电信号;该电信号经突发模式接收放大芯片组和所述电气接口传输至所述系统板卡;所述光引擎中硅基光电子集成芯片为对光信号实现收发一体的收发集成芯片。

97.在具体应用中,局端模块的光引擎中硅基光电子集成芯片为上述实施例一种任意所述的用于pon olt系统的硅基光电子的收发集成芯片。当然,上述的光引擎还可为上述实施例二中任意所述的用于pon olt系统的光引擎。其对应描述参见上述实施例一和实施例二的描述,该处不再重复。

98.此外,本实施例的sfp-dd实现双通道simplex lc光接口(双通道bidi)高速pon对光芯片集成度提出的更高的挑战,相比于单通道情景,支持pon应用的光电芯片需要两套甚至四套,采用混合集成分立器件的传统光引擎封装方式难以将所有器件都放入sfp-dd光收发器内。而利用硅基光电子集成芯片可在一块小芯片上即实现这些功能器件及其互相的连接。如用的硅光耦合器、硅光合分波器、硅光调制器、硅光pin接收器、片上监测器、片上波导均需两套,并增加了硅光分路器,这些可通过一次流片在硅基材料上实现单片集成芯片

sip。

99.另外,本实施例局端模块中电气接口可包括:sfp-dd/sfp-dd112封装的印刷电路板的金手指阵列,即sfp-dd/sfp-dd112封装的电气接口2。本实施例的电气接口用以实现25/50/100/200g pon olt系统和/或50/100/200g epon olt系统与局端模块之间的连接,且电气接口包括下述的一种或多种:单路电接口、双路电接口和四路电接口。如图12中所示的系统板卡中的pon mac asic 1经由sfp-dd/sfp-dd112封装的电气接口2进入到局端模块,并经由数字处理芯片3和硅光调制驱动器4处理,再输出至光引擎a2进而通过光接口输出;相应地,光接口接收的上行光信号经过光引擎转换为上行电信号,经由突发模式跨阻放大器bm-tia 14和突发模式线性放大器bm-la 15之后,借助于电气接口2输出至系统板卡中的突发模式 cdr serdes16,再进一步进入到pon mac asic 1。

100.参见图9和图10所示,本实施例中速率变换组件包括:数字处理芯片dsp 3和用于光信号调制的调制驱动组件;所述dsp 3用于按照光传输设备的参数对所述电气接口传输的单路或双路电信号(如tx1和tx2)进行时钟数据恢复、速率和/或码型的映射转换,以得到与光传输设备的参数一致的一路下行电信号,并通过调制驱动组件,得到一路驱动电信号;具体地,dsp包括:retimer组件、变速箱gearbox组件、码型转换模块;单路1x25gbps 或1x50gbps nrz或1x100gbps pam4码型输入时,dsp变速箱gearbox组件不工作,单路retimer组件将输入单路电信号进行时钟数据恢复,输出单路1x25gbps nrz或1x50gbps nrz或1x100gbps pam4码型作为下行电信号;双路2x25gbps nrz码型输入时,经过retimer组件、变速箱gearbox组件将双路输入电信号2x25gbps nrz映射转换为单路50gbps nrz码型,以作为输出的一路下行电信号;双路2x25gbps nrz码型输入时,经过retimer组件、变速箱gearbox组件和码型转换模块将双路输入信号2x25gbps nrz映射转换为单路50gbps pam4码型,以作为输出的一路下行电信号;双路2x50gbps nrz码型输入时,经过retimer组件、变速箱gearbox组件将双路输入信号2x50gbps nrz映射转换为单路100gbps nrz码型,以作为输出的一路下行电信号;双路2x50gbps nrz码型输入时,经过retimer组件、变速箱gearbox组件和码型转换模块将双路输入信号2x50gbps nrz映射转换为单路 100gbps pam4码型,以作为输出的一路下行电信号;双路2x100gbps pam4码型输入时,经过retimer组件、变速箱gearbox组件将双路输入信号2x100gbps pam4映射转换为单路1x200gbps pam4码型,以作为输出的一路下行电信号。

101.参见图10所示,本实施例中速率变换组件包括:双路retimer组件和用于光信号调制的调制驱动组件;所述双路retimer组件用于按照光传输设备的参数对所述电气接口传输的双路电信号进行时钟数据恢复、速率和/或码型的映射转换,以得到与光传输设备的参数一致的两路下行电信号,并通过调制驱动组件,得到两路驱动电信号。

102.上述双路retimer组件可包括:retimer芯片;双路2x25gbps nrz码型输入时,retimer芯片用于将电气接口接收的双路的电信

号各自进行时钟数据恢复,映射转换为双路的25gbps nrz码型,以作为输出的双路下行电信号;双路2x50gbps nrz码型输入时,retimer用于将电气接口接收的双路的电信号各自进行时钟数据恢复,映射转换为双路的2x50gbps nrz码型,以作为输出的双路下行电信号;双路2x100gbps pam4码型输入时,retimer用于将电气接口接收的双路的电信号各自进行时钟数据恢复,映射转换为双路的2x 100gbps pam4码型,以作为输出的双路下行电信号。

103.需要说明的是,仅使用retimer功能时,其可支持双通道路单纤双向光接口方式,支持双通道25g(s)pon或50g(s)pon 。双通道pon收发器的优点是支持更高密度更高性能的olt系统,在不改变pon mac serdes速率前提下,相比于单通道场景实现了pon连接总带宽的加倍。原一张pon板卡支持16端口sfp+pon olt光收发器,等效于现在32个高速pon端口。

104.在其他实施例中,速率变换组件包括:四路retimer组件和用于光信号调制的调制驱动组件。此时,四路retimer组件用于按照光传输设备的参数对所述电气接口传输的四路电信号进行时钟数据恢复、速率和/或码型的映射转换,以得到与光传输设备的参数一致的四路下行电信号,并通过调制驱动组件,得到四路驱动电信号。四路速率可一致,如采用4x25gbps、4x50gbps、4x100gbps,也可采用两两一致,如2x25gbps+2x50gbps的组合。

105.具体地,四路retimer组件包括:retimer芯片;四路4x25gbps nrz码型输入时,retimer芯片用于将电气接口接收的四路的电信号各自进行时钟数据恢复,映射转换为四路的25gbps nrz码型,以作为输出的四路下行电信号;四路4x50gbps nrz码型输入时,retimer用于将电气接口接收的四路的电信号各自进行时钟数据恢复,映射转换为四路的4x50gbps nrz码型,以作为输出的四路下行电信号;采用2x25gbps与2x50gbps四路组合输入时,retimer用于将电气接口接收的四路的电信号各自进行时钟数据恢复,映射转换为四路的2x25gbps与2x50gbps nrz码型,以作为输出的四路下行电信号。

106.在实际应用中,调制驱动组件为硅光调制驱动组件,集成在dsp中,或,与retimer芯片集成在一个组件上。

107.另外,本实施例的局端模块中突发模式接收放大芯片组可包括:突发模式接收跨阻放大器14和突发模式接收线性放大器15,参见图9至图11所示。

108.可理解的是,具有第二参数的电信号为一路电信号时,所述突发模式接收放大芯片组输入输出突发模式电信号为一路,如图9所示,且该路突发模式接收放大芯片组的电信号速率等于或低于具有第二参数的电信号的速率,所述用于具有第二参数的电信号为两路电信号时,所述突发模式接收放大芯片组输入输出突发模式电信号为两路,如图10和图11所示,且两路突发模式接收放大芯片组电信号的速率不高于具有第二参数的电信号的速率。

109.当用于具有第二参数的电信号为四路电信号时,所述突发模式接收放大芯片组输入输出突发模式电信号为四路,且四路突发模式接收放大芯片组电信号的速率不高于具有

第二参数的电信号的速率。

110.具体地,当dsp输出下行电信号为单路1x25gbps nrz时,经过所述突发模式接收放大芯片组的上行电信号为单路1x25gbps nrz ;当dsp输出下行电信号为单路1x50gbps nrz时,经过所述突发模式接收放大芯片组的上行电信号为单路1x25gbps nrz 或1x50gbps nrz;当dsp输出下行电信号为单路1x100gbps nrz 时,经过所述突发模式接收放大芯片组的上行电信号为单路1x50gbps nrz 或1x100gbps nrz;当dsp输出下行电信号为单路1x50gbps pam4时,经过所述突发模式接收放大芯片组的上行电信号为单路1x50gbps pam4;当dsp输出下行电信号为单路1x100gbps pam4时,经过所述突发模式接收放大芯片组的上行电信号为单路1x100gbps pam4;当dsp输出下行电信号为单路1x200gbps pam4时,经过所述突发模式接收放大芯片组的上行电信号为单路1x200gbps pam4。

111.当retimer芯片输出下行电信号为双路2x25gbps nrz时,经过所述突发模式接收放大芯片组的上行电信号为双路2x25gbps nrz ;当retimer芯片输出下行电信号为双路2x50gbps nrz时,经过所述突发模式接收放大芯片组上行电信号为双路2x50gbps nrz;当retimer芯片输出下行电信号为双路2x100gbps pam4时,经过所述突发模式接收放大芯片组的上行电信号为双路2x100gbps pam4。

112.当retimer芯片输出下行电信号为四路4x25gbps nrz时,经过所述突发模式接收放大芯片组的上行电信号为四路4x25gbps nrz ;当retimer芯片输出下行电信号为四路4x50gbps nrz时,经过所述突发模式接收放大芯片组上行电信号为四路4x50gbps nrz;当retimer芯片输出下行电信号为四路2x25gbps nrz与2x50gbps nrz组合时,经过所述突发模式接收放大芯片组上行电信号为四路2x25gbps nrz与2x50gbps nrz组合;在其他实施例中,局端模块还需要包括:微处理器17、eeprom 18、电源管理组件23等,该些组件的处理方式可与现有的局端模块中各组件的处理方式一致,本实施例不进行详细说明。另外,图12中还示出了为局端模块提供电源的光收发器电源19,在实际应用中可根据需要配置。

113.本实施例的局端设备采用小型化的sfp-dd/sfp-dd112模块,有效实现下一代olt系统设备的端口高密度、高性能需求。

114.结合图12至图14可知,图12和图13适用的serdes速率目前是24.8832gbps nrz和49.7664gbps nrz,未来serdes速率可达99.5328 gbps pam4。具体地,图12至图14的左侧属于系统板卡中的olt pon mac,其位于系统板卡,以asic(application specific integrated circuit,专用集成电路)或fpga(field programmable gate array ,现场可编程门阵列)方式实现physical coding sublayer(pcs)功能,包括前向纠错(fec)、信号编解码等。mac单路高速信号采用itu-t pon标准速率24.8832gbps(简称25gbps)或49.7664gbps(50gbps),编码方式采用nrz,该结构和现有的结构功能一致,该处不再赘述。mac单路高速信号也可在未来提升至99.5328gbps,编码方式为pam4。mac单路高速信号亦可

采用以太网速率25.78125gbps(亦简称25gbps)。

115.需要说明的是,在图13中,pma现在输出是2*24.8832gbps nrz和2*49.7664gbps nrz ,未来可输出2*99.5328 gbps pam4。

116.在图14中,serdes速率目前是25.78125gbps nrz,未来serdes速率可达28gbaud/56 gbps pam4和56gbaud/112 gbps pam4。基于本实施例的结构当前pma输出2*25.78125gbps nrz,未来可适用2*28gbaud/56 gbps pam4和2*56gbaud/112 gbps pam4。

117.电气接口:系统板卡的高速信号、控制信号、电源供应等经此进出光收发器;电气接口可同时提供双路高速电信号输入(tx1&2)及输出(rx1&2),也可根据系统板卡要求,只提供一路输入输出(tx1+rx1)。

118.硅光调制器驱动器/硅光调制驱动组件:经由映射转换后的高速信号叠加至此驱动器上,由该驱动器高速调制硅光调制器。图12中示出的硅光调制驱动器目前的输出是1*24.8832gbps nrz、1*49.7664gbps nrz、1*49.7664 gbps pam4;未来硅光调制驱动器的输出可以是1*99.5328gbps nrz、1*99.5328 gbps pam4、1*99.0656 gbps pam4。

119.突发模式跨阻放大器14:将pin接收器11接收到的25g或50g突发模式信号放大;突发模式线性放大器15:对突发tia输出的25g/50g差分电信号进行放大,并减少前导码的丢失;bm cdr serdes(突发模式时钟数据恢复serdes):位于系统板卡上。接收信号rx1经突发模式线性放大器15和电气接口2后进入此bm cdr serdes 16;在本地精确时钟信号24.8832gbps 或49.7664gbps的参考之下,对突发限幅放大器的信号进行鉴频鉴相处理,消除上行信号的抖动和码间干扰,增强驱动能力之后再传回给系统中的pon mac asic 1。

120.微处理器17:用于处理光收发器各元器件的控制信号、感知信号、协调各元器件的工作;eeprom(electrically erasable programmable read-only memory带电可擦除可编程只读存储器) 18:用于存储光收发器内部各光器件的性能和控制信息,光收发器正常工作时,由微型tec控制器通过i2c调用eeprom 18中相应技术参数;光收发器电源19:通过电气接口2提供光收发器各组件正常运行所需电源;例如可以提供一种3.3v的电源输入。

121.电源管理组件23:用于把光收发器的3.3v总电源降压或升压到各个单元电路需要的电平,并按照规定的时序给对应的单元电路供电。

122.本实施例中,采用sff-dd msa协议定义的电气接口结合itu-t pon速率定义,也提供了同一封装,光口速率升级至单路100gpon的直接路径,且编码方式可灵活采用nrz(100gbaud)也可pam4(56gbaud)。

123.此外,sfp-dd112 msa增加了支持单路100g pam4输入信号,因此上述的光收发器还可于sfp-dd112封装上未来实现扩展至单路200gpon(经2x1gearbox后的输出信号)。

124.实施例四本发明实施例还提供一种无源光网络pon olt系统,其包括:上述实施例四中任意所述的基于硅基光电子集成芯片的多速率通道的局端模块;所述系统通过所述局端模块与pon网络侧交互。系统的基本硬件单元包含电源、机框和板卡。本实施例中,所述pon olt系统局端板卡可插入sfp-dd/sfp-dd112光收发器的数量为16个。

125.结合图1至图16可知,pon mac asic 1发出编码后的高速信号经sfp-dd/sfp-dd112封装的电气接口2进入光收发器内的数字处理芯片(dsp)3。信号速率遵守itu-t pon标准速率要求:为24.8832gbps(简称25gbps)或49.7664gbps(50gbps),编码方式均为nrz。sfp-dd/sfp-dd112可支持双路高速电信号输入(tx1&tx2)及输出(rx1&rx2),也可只采用一路输入输出(tx1+rx1)。

126.数字处理芯片(dsp)3输出的单路高速信号施加在硅光调制驱动器4上,硅光调制驱动器4高速调制,大功率半导体激光器驱动器22设置o波段大功率半导体激光器6最优工作点,经设置最优工作点的o波段大功率半导体激光器6输出大功率激光信号作为pon下行光源。根据itu-t 50gpon、ieee 25g/50g-epon及25g(s)pon要求全工作温度范围内激射波长维持在1342nm+2nm和1358nm+2nm。

127.1342nm+2nm和1358nm+2nm通过硅光耦合器7进入收发集成芯片a1,经片上波导进入硅光调制器4被高速调制,再经片上波导,通过硅光合分波器8后离开收发集成芯片a1,耦合进入o波段增益芯片9;o波段增益芯片9由soa驱动器12设置最优芯片工作点,发射(下行λ

ds

)和接收(上行λ

us

)不同波长的o波段光信号经此增益芯片同时被放大。

128.被o波段增益芯片9放大的λ

ds

发射大功率信号经微透镜(25c、25a或25b)耦合至sfp-dd/sfp-dd112光收发器的simplex sc光接口10,并进入传输光纤发网远端;接收方向的信号说明如下:上行λ

us

从传输光纤经simplexsc光接口10进入光收发器的光引擎。

129.上行λ

us

经微透镜(25c、25a或25b)进入o波段增益芯片9被放大后通过硅光合分波器8,上行λ

us

经硅光合分波器8和进入硅光pin接收器11;硅光pin接收器11将单路高速上行突发模式λ

us

光信号转化成单路突发模式高速电信号;硅光pin接收器11输出的突发模式高速电信号顺序经突发模式跨阻放大器14、突发模式线性放大器15、sfp-dd/sfp-dd112封装的电气接口2后离开光收发器进入系统板卡,以及信号经过高速的系统板卡的bm cdr serdes 16后进入pon mac asic 1,完成olt侧的信号收发闭环。

130.应当注意的是,在权利要求中,不应将位于括号之间的任何附图标记理解成对权利要求的限制。词语“包含”不排除存在未列在权利要求中的部件或步骤。位于部件之前的词语“一”或“一个”不排除存在多个这样的部件。本发明可以借助于包括有若干不同部件的硬件以及借助于适当编程的计算机来实现。在列举了若干装置的权利要求中,这些装置中的若干个可以是通过同一个硬件来具体体现。词语第一、第二、第三等的使用,仅是为了表述方便,而不表示任何顺序。可将这些词语理解为部件名称的一部分。

131.此外,需要说明的是,在本说明书的描述中,术语“一个实施例”、“一些实施例”、“实施例”、“示例”、“具体示例”或“一些示例”等的描述,是指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

132.尽管已描述了本发明的优选实施例,但本领域的技术人员在得知了基本创造性概念后,则可对这些实施例作出另外的变更和修改。所以,权利要求应该解释为包括优选实施

例以及落入本发明范围的所有变更和修改。

133.显然,本领域的技术人员可以对本发明进行各种修改和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也应该包含这些修改和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1