一种叠对标记的掩膜版版图的制作方法

本发明涉及半导体制造,特别涉及一种叠对标记的掩膜版版图。

背景技术:

1、在现有的半导体制作过程中,在晶圆制作半导体器件之前,需要对晶圆进行布局设计,将晶圆划分为若干单元区(die)和位于单元区之间的切割道(scribe lane),其中,单元区用于后续形成半导体器件,切割道用于在半导体器件制作完成时,作为封装阶段单元区分割时的分割线。在设计用于划分晶圆表面的单元区和切割道的光刻版图时,通常将光刻对准标记(alignment mark)和叠对标记(overlay mark)等光刻工艺中所需要用到的光刻图形形成在切割道。

2、随着半导体器件的集成度不断提高,器件的特征尺寸不断缩小,各层光刻图案之间的叠对准确性对于晶圆整体良率的影响越来越重要。

技术实现思路

1、本发明的目的在于提供一种叠对标记的掩膜版版图,以解决各层光刻图案之间的叠对准确性不高的问题。

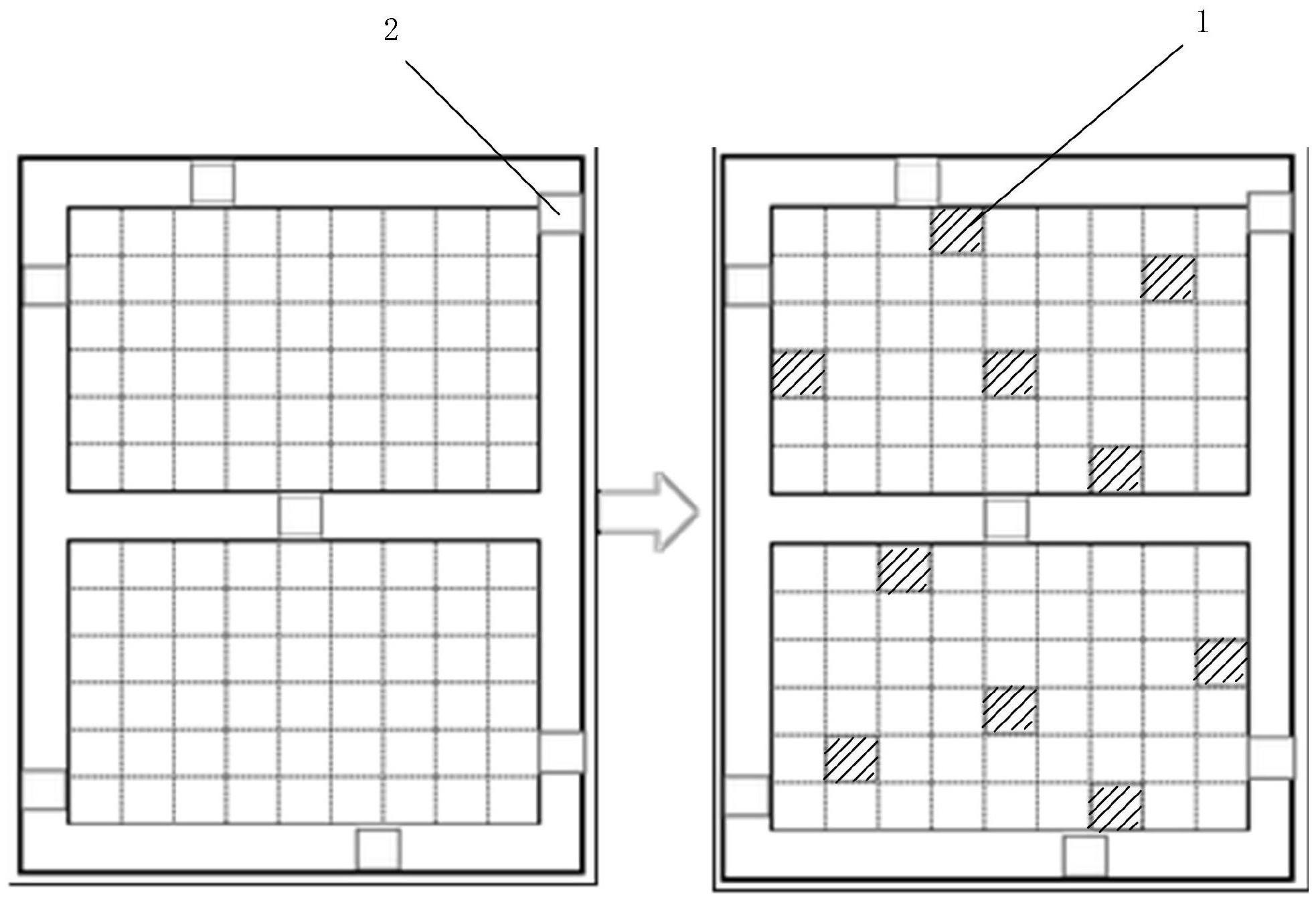

2、为解决上述技术问题,本发明提供一种叠对标记的掩膜版版图,包括主图形区以及围绕所述主图形区的切割道图形区,其中,所述主图形区包括用于在芯片的器件区内对应形成第一叠对标记的第一标记图案,所述切割道图形区包括用于在芯片的切割道区内对应形成第二叠对标记的第二标记图案。

3、优选的,在所述叠对标记的掩膜版版图中,所述第一标记图案包括标识图形区域和围绕所述标识图形区域的虚设图形区域,所述虚设图形区域的边沿上的任一位置与所述标识图形区域之间的距离均相等。

4、优选的,在所述叠对标记的掩膜版版图中,所述标识图形区域包括:面积相同的四个子图形区域,四个所述子图形区域两两呈对角分布,其中两个呈对角分布的所述子图形区域分别包括沿第一方向布置且相互平行的多个第一条形图案,另外两个呈对角分布的所述子图形区域分别包括沿第二方向布置且相互平行的多个第二条形图案,所述第一方向和所述第二方向相垂直。

5、优选的,在所述叠对标记的掩膜版版图中,所述标识图形区域为正方形区域。

6、优选的,在所述叠对标记的掩膜版版图中,所述掩膜版版图包括多个所述第一标记图案,多个所述第一标记图案间隔形成于所述主图形区。

7、优选的,在所述叠对标记的掩膜版版图中,至少在所述主图形区的中心形成一所述第一标记图案。

8、优选的,在所述叠对标记的掩膜版版图中,通过所述第一标记图案形成的所述第一叠对标记的关键尺寸,与通过所述第二标记图案形成的所述第二叠对标记的关键尺寸相同。

9、优选的,在所述叠对标记的掩膜版版图中,所述第一标记图案的尺寸为所述第二标记图案的尺寸的x倍,所述x倍依据版图转化规则进行设计。

10、优选的,在所述叠对标记的掩膜版版图中,在所述切割道图形区与相邻两个所述主图形区距离相等的位置形成所述第二标记图案。

11、优选的,在所述叠对标记的掩膜版版图中,利用所述掩膜版版图形成所述第一叠对标记的所述器件区的膜层和形成所述第二叠对标记的所述切割道区的膜层的结构相同,以同时通过所述第一叠对标记和所述第二叠对标记对所述芯片的叠对变化进行量测。

12、综上所述,本发明提供一种叠对标记的掩膜版版图,包括主图形区以及围绕所述主图形区的切割道图形区,其中,所述主图形区包括用于在芯片器件区内对应形成第一叠对标记的第一标记图案,所述切割道图形区包括用于在芯片切割道区内对应形成第二叠对标记的第二标记图案。利用所述叠对标记的掩膜版版图在所述器件区形成所述第一叠对标记,以及在所述切割道区形成所述第二叠对标记。通过在所述器件区形成第一叠对标记,以及在所述切割道区形成第二叠对标记,可以准确模拟所述器件区内的叠对变化,因此可以提高量测各层光刻图案之间的叠对准确性。

技术特征:

1.一种叠对标记的掩膜版版图,其特征在于,包括:

2.如权利要求1所述的叠对标记的掩膜版版图,其特征在于,所述第一标记图案包括:

3.如权利要求2所述的叠对标记的掩膜版版图,其特征在于,所述标识图形区域包括:面积相同的四个子图形区域,四个所述子图形区域两两呈对角分布,其中两个呈对角分布的所述子图形区域分别包括沿第一方向布置且相互平行的多个第一条形图案,另外两个呈对角分布的所述子图形区域分别包括沿第二方向布置且相互平行的多个第二条形图案,所述第一方向和所述第二方向相垂直。

4.如权利要求2所述的叠对标记的掩膜版版图,其特征在于,所述标识图形区域为正方形区域。

5.如权利要求1所述的叠对标记的掩膜版版图,其特征在于,所述叠对标记的掩膜版版图包括多个所述第一标记图案,多个所述第一标记图案间隔形成于所述主图形区。

6.如权利要求1所述的叠对标记的掩膜版版图,其特征在于,至少在所述主图形区的中心形成一所述第一标记图案。

7.如权利要求1所述的叠对标记的掩膜版版图,其特征在于,通过所述第一标记图案形成的所述第一叠对标记的关键尺寸,与通过所述第二标记图案形成的所述第二叠对标记的关键尺寸相同。

8.如权利要求7所述的叠对标记的掩膜版版图,其特征在于,所述第一标记图案的尺寸为所述第二标记图案的尺寸的x倍,所述x倍依据版图转化规则进行设计。

9.如权利要求1所述的叠对标记的掩膜版版图,其特征在于,在所述切割道图形区与相邻两个所述主图形区距离相等的位置形成所述第二标记图案。

10.如权利要求1所述的叠对标记的掩膜版版图,其特征在于,利用所述叠对标记的掩膜版版图形成所述第一叠对标记的所述器件区的膜层和形成所述第二叠对标记的所述切割道区的膜层的结构相同,以同时通过所述第一叠对标记和所述第二叠对标记对所述芯片的叠对变化进行量测。

技术总结

本发明提供一种叠对标记的掩膜版版图,包括主图形区以及围绕所述主图形区的切割道图形区,其中,所述主图形区包括用于在芯片的器件区内对应形成第一叠对标记的第一标记图案,所述切割道图形区包括用于在芯片的切割道区内对应形成第二叠对标记的第二标记图案。利用所述叠对标记的掩膜版版图在所述器件区形成所述第一叠对标记,以及在所述切割道区形成所述第二叠对标记,可以准确模拟所述器件区内的叠对变化,尤其是实现所述器件区的中心位置的各层光刻图案的叠对变化进行准确测量。

技术研发人员:付嵛,吴鹏

受保护的技术使用者:上海华力微电子有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!