一种芯片设计版图优化方法及装置与流程

【】本发明涉及光刻领域,特别涉及一种芯片设计版图优化方法及装置。

背景技术

0、

背景技术:

1、随着集成电路关键尺寸的不断缩小,业界对能够提高光刻系统成像性能的分辨率增强技术(ret)提出了更高的要求。在众多ret中,光学邻近效应修正(opc)通过物理模型和数学计算来计算光学邻近效应,然后基于计算结果对原始设计图形做定量的变形,从而给出可以在硅片上具有良好成像效果的修正后的掩模版。

2、而修正后的掩模版为了满足一定的可制造性要求,还需要引入额外的计算和检查,称为掩模规则检查(mask rule check,mrc)。mrc规则有边到边、拐角到边、拐角到拐角的规则等。现有技术中通常将图形进行打断获得边,再对每一条边进行mrc违规检查,最后基于算法获得移动量并对每一条边进行移动。修正过程即对设计版图的优化过程,然而在对设计版图内的图形进行修正优化时,图形形变可能使得原有图形中的规则消失,也可能出现原有图形中没有的规则。即优化后的某些图形反而违反了mrc规则,尤其在角对角的规则中,涉及四个可移动边,其修正量或可修正余裕计算最为复杂。根据现有技术应对角对角规则计算图形的边的修正量或可修正余裕时,难以避免突变违规出现,且在计算是极大限制了opc算法的性能。

技术实现思路

0、

技术实现要素:

1、为了解决现有技术应对图形之间出现角对角规则进行修正效果差的问题,本发明提供一种芯片设计版图优化方法及装置。

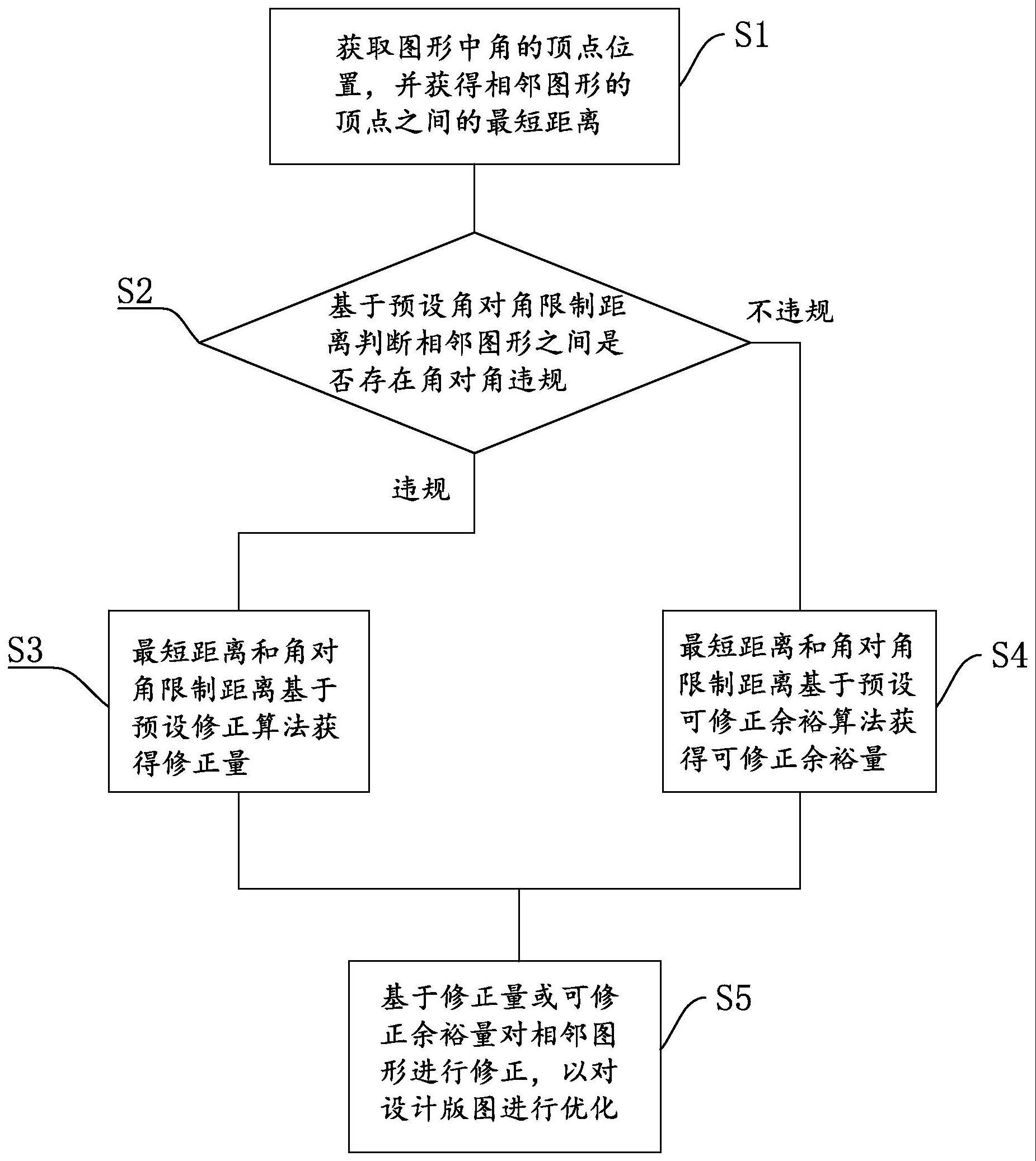

2、本发明为解决上述技术问题,提供如下的技术方案:一种芯片设计版图优化方法,用于对设计版图内存在角对角规则的相邻图形进行优化修正,包括以下步骤:

3、获取图形中角的顶点位置,并获得相邻图形的顶点之间的最短距离;

4、基于预设角对角限制距离判断相邻图形之间是否存在角对角违规;

5、若违规,则最短距离和预设角对角限制距离基于预设修正算法获得修正量;

6、若不违规,则最短距离和预设角对角限制距离基于预设可修正余裕算法获得可修正余裕量;

7、基于修正量或可修正余裕量对相邻图形进行修正,以对设计版图进行优化。

8、优选地,获取图形中角的顶点位置具体包括如下步骤:

9、获取设计版图中图形的轮廓信息,基于预设角对角形状对图形的轮廓进行匹配以获得可能存在角对角违规的相邻图形;

10、获取相邻图形的两个邻近角的顶点位置。

11、优选地,基于预设角对角限制距离判断相邻图形之间是否存在角对角违规具体包括:

12、于设计版图上建立水平-垂直坐标轴;

13、获取两个邻近角的顶点之间的水平最短距离和垂直最短距离;

14、基于水平最短距离和垂直最短距离计算获得两个邻近角的顶点之间的最短距离;

15、若最短距离小于角对角限制距离则该相邻图形的两个邻近角存在角对角违规;

16、若最短距离大于角对角限制距离则该相邻图形的两个邻近角不存在角对角违规。

17、优选地,所述预设修正算法为:

18、公式一:

19、

20、公式二:{kicvi=cv|1≤i≤4};

21、其中,dist_x表示相邻图形的顶点之间的水平最短距离,dist_y表示相邻图形的顶点之间的垂直最短距离,cvi(i=,2,3,4)表示顶点所对应的第i条边进行移动的距离,c2c_spec表示角对角限制距离;公式二中cv表示的是单位修正长度的量,ki表示常数,即1/kicv表示第i条边的修正量。公式二表示对公式一中对第i条边的修正方式进行约束,以使顶点所对应的第i条边按照1/ki倍的单位修正长度进行修正。

22、优选地,将预设修正算法中公式二进行更新,更新后的公式二为:{cvi=cv|1≤i≤4};

23、更新后的公式二表示对公式一中对第i条边的修正方式进行约束,以使顶点所对应的所有边按照相同的修正量进行修正,cv表示顶点所对应的所有边的修正量。

24、优选地,可修正余裕算法包括:

25、公式三:

26、8cv2-4(dist_x+dist_y)cv+(dist_x2+dist_y2-c2c_spec2)=0;

27、公式四:

28、δ=(dist_x+dist_y)2-2(dist_x2+dist_y2-c2c_spec2);

29、

30、其中,公式三中的cv为更新后的公式二对公式一中对第i条边的修正方式进行约束,以使顶点所对应的所有边按照相同的修正量进行修正,dist_x表示相邻图形的顶点之间的水平最短距离,dist_y表示相邻图形的顶点之间的垂直最短距离;公式四为判断公式三中的cv是否存在解,若δ≥0则表明cv存在两个解,且cv输出的值为两个解中的较小值,且将其做为可修正余裕量,若δ≥0则表明cv无解,cv输出的值为水平最短距离和垂直最短距离中较大值的0.5倍,并将其作为可修正余裕量。

31、优选地,基于修正量对相邻图形进行修正具体包括:

32、获取相邻图形的两个邻近角所对应的边的位置信息;

33、修正量包括移动方向和修正距离,设定朝图形内部的移动方向为修正量的移动方向;

34、邻近角所对应的边基于修正量的移动方向进行移动修正距离以使相邻图形消除角对角违规。

35、优选地,基于可修正余裕量对相邻图形进行修正具体包括:

36、获取相邻图形的两个邻近角所对应的边的位置信息;

37、可修正余裕量包括移动方向和可修正余裕距离设定朝图形外部的移动方向为可修正余裕量的移动方向;

38、两个邻近角所对应的边基于可修正余裕量的移动方向进行移动以使相邻图形消除角对角违规。

39、优选地,基于可修正余裕量的移动方向进行移动可修正余裕量距离之后进一步包括:

40、基于预设边对边限制距离判断修正后两个邻近角所对应的边之间是否存在边对边违规;

41、若违规,则减少可修正余裕量以消除边对边违规。

42、本发明为解决上述技术问题,提供又一技术方案如下:一种装置,应用于上述的芯片设计版图优化方法,所述装置包括:

43、识别模块:用于获取图形中角的顶点位置,并获得相邻图形的顶点之间的最短距离;

44、判断模块:用于判断相邻图形之间是否存在角对角违规

45、计算模块:用于基于预设修正算法获得修正量或基于预设可修正余裕算法获得可修正余裕量;

46、处理模块:用于基于修正量或可修正余裕量对相邻图形进行修正。

47、与现有技术相比,本发明所提供的一种芯片设计版图优化方法及装置,具有如下的有益效果:

48、1.本发明实施例提供的一种芯片设计版图优化方法,用于对设计版图内存在角对角规则的相邻图形进行优化修正,包括以下步骤:

49、获取图形中角的顶点位置,并获得相邻图形的顶点之间的最短距离;

50、基于预设角对角限制距离判断相邻图形之间是否存在角对角违规;

51、若违规,则最短距离和角对角限制距离基于预设修正算法获得修正量;

52、若不违规,则最短距离和角对角限制距离基于预设可修正余裕算法获得可修正余裕量;

53、基于修正量或可修正余裕量对相邻图形进行修正,以对设计版图进行优化。本实施例解决了现有技术无法以通常手段解方程得到关键的修正量和可修正余裕信息,额外提供了预设的修正算法和可修正余裕算法,以使opc算法对设计图形进行修正的行为更加可控,进而提升了考虑mrc规则的opc算法的表现和运行效率。

54、2.本发明实施例获取图形中角的顶点位置具体包括如下步骤:获取设计版图中图形的轮廓信息,基于预设角对角形状对图形的轮廓进行匹配以获得可能存在角对角违规的相邻图形;获取相邻图形的两个邻近角的顶点位置。基于上述方法获得图形中角的顶点位置避免占用过多的算法资源,极大提升了整体运送过程中的效率。

55、3.本发明实施例基于预设角对角限制距离判断相邻图形之间是否存在角对角违规具体包括:于设计版图上建立水平-垂直坐标轴;获取两个邻近角的顶点之间的水平最短距离和垂直最短距离;基于水平最短距离和垂直最短距离计算获得两个邻近角的顶点之间的最短距离;若最短距离小于角对角限制距离则该相邻图形的两个邻近角存在角对角违规;若最短距离大于角对角限制距离则该相邻图形的两个邻近角不存在角对角违规。操作简单,效率高。

56、4.本发明实施例所述预设修正算法为:

57、公式一:

58、

59、公式二:{kicvi=cv|1≤i≤4};

60、其中,dist_x表示相邻图形的顶点之间的水平最短距离,dist_y表示相邻图形的顶点之间的垂直最短距离,cvi(i=,2,3,4)表示顶点所对应的第i条边进行移动的距离,c2c_spec表示角对角限制距离;公式二中cv表示的是单位修正长度的量,ki表示常数,即1/kicv表示第i条边的修正量。公式二表示对公式一中对第i条边的修正方式进行约束,以使顶点所对应的第i条边按照1/ki倍的单位修正长度进行修正。当存在角对角违规时,由于限制了每一条边和单位修正长度的比例关系,因此四元二次方程问题变化解为一元二次方程,进而可以获得修正量的解。基于修正量对相邻图形的边进行移动修正,即可消除角对角违规。

61、5.本发明实施例将预设修正算法中公式二进行更新,更新后的公式二为:{cvi=cv|1≤i≤4};更新后的公式二表示对公式一中对第i条边的修正方式进行约束,以使顶点所对应的所有边按照相同的修正量进行修正,cv表示顶点所对应的所有边的修正量。相邻图形的边进行移动的修正量将相同。使得计算过程更为简单,有助于提升计算效率。

62、6.本发明实施例可修正余裕算法包括:

63、公式三:

64、8cv2-4(dist_x+dist_y)cv+(dist_x2+dist_y2-c2c_spec2)=0;

65、公式四:

66、δ=(dist_x+dist_y)2-2(dist_x2+dist_y2-c2c_spec2);

67、

68、其中,公式三中的cv为公式二对公式一中对第i条边的修正方式进行约束,以使顶点所对应的所有边按照相同的修正量进行修正,dist_x表示相邻图形的顶点之间的水平最短距离,dist_y表示相邻图形的顶点之间的垂直最短距离;公式四为判断公式三中的移动量是否存在解,若δ≥0则表明cv存在两个解,且cv输出的值为两个解中的较小值,且将其做为可修正余裕量,若δ≥0则表明cv无解,cv输出的值为水平最短距离和垂直最短距离中较大值的0.5倍,并将其作为可修正余裕量。由于限制了每一条边修正的关系,即在进行修正时限制所有边移动的距离相同,因此四元二次方程问题变化解为一元二次方程,进而可以简便获得cv的解,进而轻松获得可修正余裕量。

69、7.本发明实施例基于可修正余裕量的移动方向进行移动可修正余裕量距离之后进一步包括:基于预设边对边限制距离判断修正后两个邻近角所对应的边之间是否存在边对边违规;若违规,则减少可修正余裕量以消除边对边违规。通过改进mrc中关于c2c形状的计算结果,避免了大多数c2c形状突变为e2e形状并产生mrc违规的不利情况发生,使opc算法能够在更安全的边界内运行,减少了突变违规带来的反复调试参数与重新运行opc算法的时间损耗,从而提升了考虑mrc规则的opc算法的表现和运行效率。

70、10.本发明实施例还提供一种装置,具有与上述一种芯片设计版图优化方法相同的有益效果,在此不做赘述。

- 还没有人留言评论。精彩留言会获得点赞!