一种大规模光开关阵列驱动控制芯片及其设计方法与流程

本发明涉及数据中心光开关阵列,具体涉及一种大规模光开关阵列驱动控制芯片及其设计方法。

背景技术:

1、随着互联网的高速发展,大数据、云计算、物联网、量子通信、人工智能等技术不断渗透、交叉、融合,数据的传输量急速增长。数据中心海量数据的传输往往存在传输路径的选择及路由切换。传统电子交换技术存在数据容量小、切换延时长、功耗高、体积大等不足,而基于光开关阵列的光交换、光路由选择具有高速、宽带、透明、低功耗以及潜在的低成本等诸多优点。

2、光开关阵列是数据中心光交换的核心,其功能是实现光信号在不同光路上的快速交换,当光开关达到一定规模后,需要单独控制的开关单元数目非常庞大,除了光开关芯片本身的设计原理和结构外,控制和驱动电路也影响开关的速度、功耗等特性,影响光开关综合性能的发挥。现有的光开关阵列驱动控制电路存在驱动路数有限、不可拓展、走线长延时大、集成度低、体积大等技术难题。

技术实现思路

1、为解决现有驱动控制电路的不足,本发明的目的在于提供一种大规模光开关阵列驱动控制芯片及其设计方法。

2、为实现上述目的,本发明采用了以下技术方案:

3、在本发明的第一方面,公开了一种大规模光开关阵列驱动控制芯片。

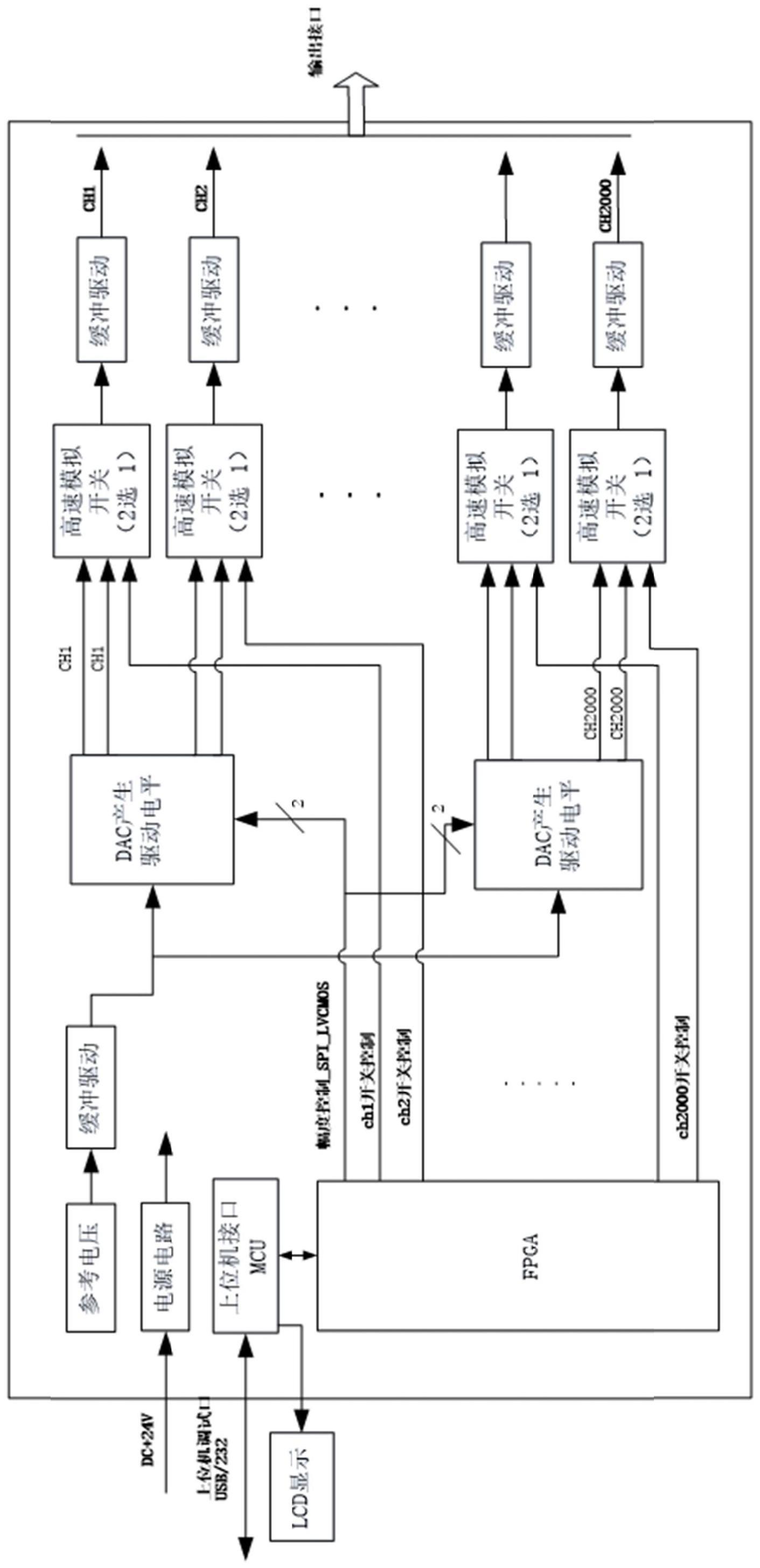

4、具体地说,该芯片包括fpga单元、dac单元、高速模拟开关电路和缓冲驱动单元;

5、所述fpga的输出端分别与所述dac单元的输入端、所述高速模拟开关电路的输入端相连;

6、所述dac单元的输出端与所述高速模拟开关电路的输入端相连;

7、所述高速模拟开关电路的输出端与所述缓冲驱动单元的输入端相连;

8、所述缓冲驱动单元的输出端与光开关阵列相连。

9、进一步的,所述光开关阵列包括多个光开光单元;

10、所述高速模拟开关电路包括多个高速模拟开关;

11、所述缓冲驱动单元包括多个缓冲驱动电路;

12、所述光开关单元、所述高速模拟开关和所述缓冲驱动电路的数量相等;

13、所述高速模拟开关与所述缓冲驱动电路一一对应连接;

14、所述缓冲驱动电路与所述光开光单元一一对应连接。

15、进一步的,所述fpga单元,用于根据上位机的控制指令输出幅度控制信号给dac单元;

16、所述fpga单元,还用于控制高速模拟开关电路在高低电平之间切换,以产生脉冲控制信号;

17、所述dac单元,用于将接收到的信号转换为对应的高电平、低电平幅度信号;

18、所述缓冲驱动单元,用于隔离和提高参考电压输出带负载能力。

19、进一步的,该芯片还包括电源电路;

20、所述电源电路用于为fpga单元、dac单元和高速模拟开关电路提供所需的工作电压。

21、进一步的,该芯片还包括上位机;

22、所述上位机与所述fpga单元的上位机接口相连;

23、所述上位机接口,用于通过通讯接口发送需要输出的目标通道及输出控制信号的幅度。

24、进一步的,该芯片还包括lcd显示单元;

25、所述lcd显示单元用于实时显示当前正在输出的通道以及输出信号的幅值信息。

26、在本发明的第二方面,公开了一种大规模光开关阵列驱动控制芯片的设计方法。

27、具体地说,该方法包括:

28、s1、设计fpga单元,用于接收上位机的控制指令,输出幅度控制信号;

29、s2、设计dac单元,并对dac单元所需的参考电压进行设置;所述dac单元,用于接收fpga单元输出的幅度控制信号,并将接收到的信号转换为对应的高电平、低电平幅度信号;

30、s3、设计高速模拟开关电路,用于在fpga单元的控制下,在高低电平之间不断切换,产生脉冲控制信号;

31、s4、设计缓冲驱动单元,在输出端配置缓冲驱动单元且设置在高速模拟开关电路之后,用于隔离和提高参考电压输出带负载能力;

32、s5、设计电源电路,用于为fpga单元、dac单元、高速模拟开关电路提供所需的工作电压;

33、s6、设计lcd显示单元,用于实时显示通道输出以及输出信号的幅值信息。

34、和现有技术相比,本发明的优点为:

35、本发明以2000路光开关阵列为控制对象,提出了一种新型的大规模光开关阵列驱动控制电路,用于解决光开关速度快而驱动控制电路速度慢的现实问题。本发明对于海量数据大容量、低延时传输和快速光交换的实现都具有重要的参考意义。本发明采用dac与高速模拟开关组合的技术方案,创造性地实现了高速脉冲信号的产生,且驱动脉冲信号的上升沿、下降沿仅由高速模拟开关决定。

技术特征:

1.一种大规模光开关阵列驱动控制芯片,其特征在于,该芯片包括fpga单元、dac单元、高速模拟开关电路和缓冲驱动单元;

2.根据权利要求1所述的大规模光开关阵列驱动控制芯片,其特征在于,

3.根据权利要求1所述的大规模光开关阵列驱动控制芯片,其特征在于,

4.根据权利要求1所述的大规模光开关阵列驱动控制芯片,其特征在于,

5.根据权利要求1所述的大规模光开关阵列驱动控制芯片,其特征在于,

6.根据权利要求1所述的大规模光开关阵列驱动控制芯片,其特征在于,

7.一种大规模光开关阵列驱动控制芯片的设计方法,其特征在于,该方法包括:

8.根据权利要求7所述的设计方法,其特征在于,该方法还包括:

技术总结

本发明涉及一种大规模光开关阵列驱动控制芯片及其设计方法。该芯片包括FPGA单元、DAC单元、高速模拟开关电路和缓冲驱动单元;所述FPGA的输出端分别与所述DAC单元的输入端、所述高速模拟开关电路的输入端相连;所述DAC单元的输出端与所述高速模拟开关电路的输入端相连;所述高速模拟开关电路的输出端与所述缓冲驱动单元的输入端相连;所述缓冲驱动单元的输出端与光开关阵列相连。本发明以2000路光开关阵列为控制对象,提出了一种新型的大规模光开关阵列驱动控制芯片及其设计方法,用于解决光开关速度快而驱动控制电路速度慢的现实问题。本发明对于海量数据大容量、低延时传输和快速光交换的实现都具有重要的参考意义。

技术研发人员:杨鹏毅,姚宗影,吴洋,庄永河,刘金鹏,李鸿高,周晶,李子祥

受保护的技术使用者:中国电子科技集团公司第四十三研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!