一种硅光子学系统中的新式的电光调变器的制作方法

本发明涉及半导体,尤其是涉及一种硅光子学系统中的新式的电光调变器。

背景技术:

1、硅光子,即siph,是藉由半导体制程所设计与制造,包含了整合集成电路(eic)部份与集成光路(pic)部份。是新世代微波通讯及巨型资料中心及ai高速运算的必要要件。在硅光子的器件中,其中的电光调变器是由在硅波导中通过驱动电压来改变光学折射率和吸收系数来调制相位和振幅。

2、而等离子体色散效应多用于高速硅调变器,等离子体色散诱导的折射率变化效应如公式①:

3、∆n=-(e2λ2/8π2c2ε0n)[∆ne/m*ce+∆nh/m*ch]①

4、其中,e是电子电荷,ε0是真空中的介电常数,c是真空中的光速,λ为波长,n为未扰动折射率,m*ce和m*ch为电子和空穴的电导率有效质量,∆ne和∆nh为电子和空穴的浓度变化,然而现有技术中的电光调变器存在以下缺陷:折射率的变化太小以至于光波的相位调变幅度不够明显,因此提出一种新式的设计以改善上述问题。

技术实现思路

1、本发明为克服上述情况不足,旨在提供一种运用在siph其中的电光调变器的新式设计,以解决上述背景技术中提出的问题。

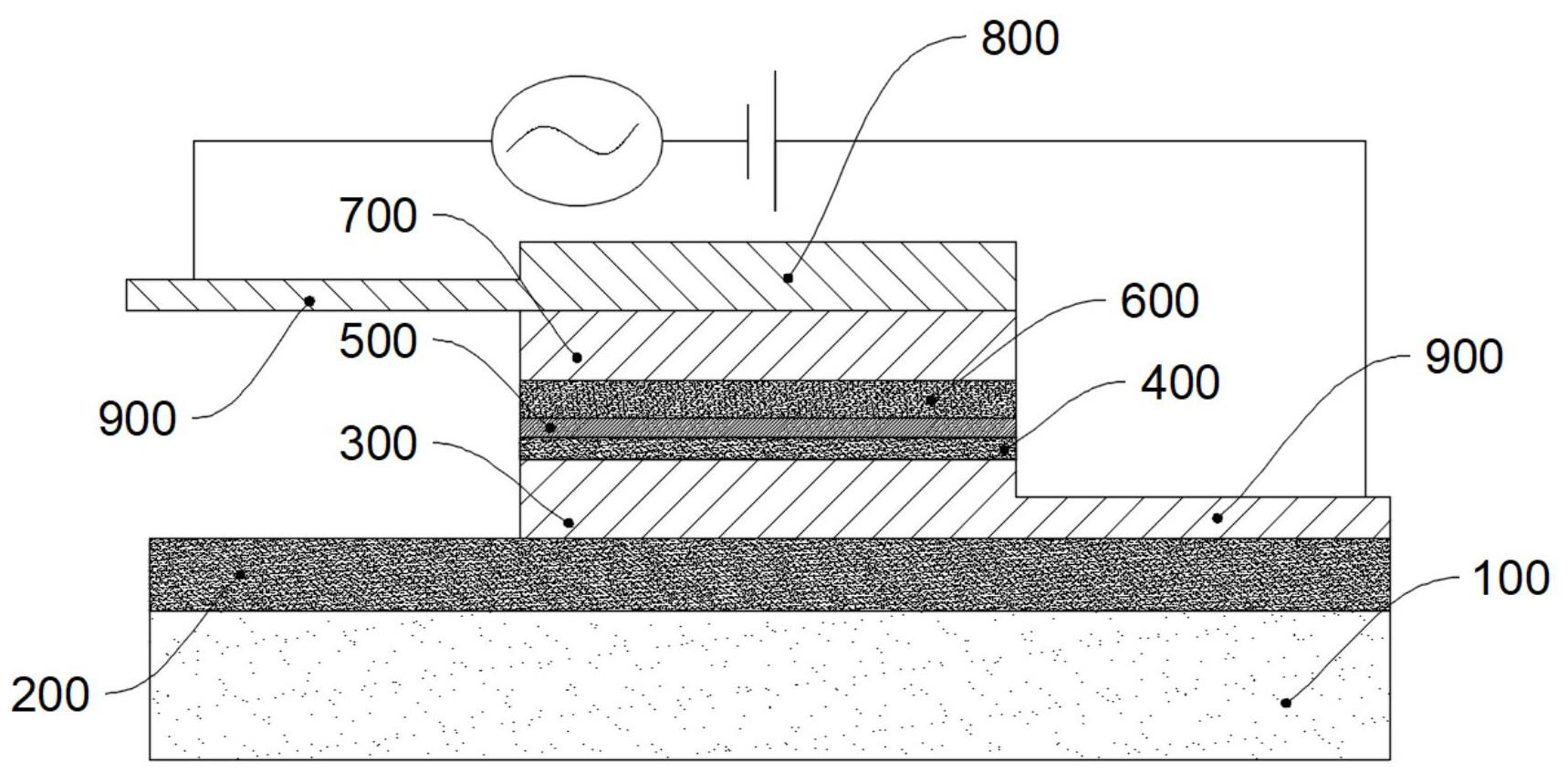

2、由于等离子体色散效应与有效质量成反比,因此提出了一种减少电子和电洞的有效质量的应变工程,即设计一种硅光子学系统中的新式的电光调变器,包括集成光路,集成光路上具有硅片;

3、在集成光路上以半导体制程技术,在硅片上设置二氧化硅层;

4、在集成光路上以半导体制程技术,在硅氧化层上以磊晶制程设置p型硅层;

5、在集成光路上以半导体制程技术,在p型硅层上以磊晶制程设置掺杂p型载子的硅化锗层;

6、在集成光路上以半导体制程技术,在硅化锗层上设置中介绝缘层;

7、在集成光路上以半导体制程技术,在中介绝缘层上设置应变氮化硅层;

8、在集成光路上以半导体制程技术,在应变氮化硅层上以磊晶制程设置n型硅层;

9、在集成光路上以半导体制程技术,在n型硅层上设置多晶硅层;

10、其中,p型硅层和n型硅层作为光波导使用,在集成光路上,施加有偏置电压于p型硅层和n型硅层,以改变p型硅层和n型硅层的折射率。

11、优选地,中介绝缘层为三明治结构,其采用氧化硅、氧化铝、氧化锆或氧化铪材料制成。

12、优选地,p型硅层和多晶硅层均延伸有接电部,偏置电压与接电部电连接。

13、优选地,二氧化硅层的厚度为120nm-200nm。

14、优选地,p型硅层的厚度为100nm-200nm。

15、优选地,硅化锗层的厚度为10nm-25nm。

16、优选地,中介绝缘层的厚度为2nm-10nm。

17、优选地,应变氮化硅层的厚度为8nm-20nm。

18、优选地,n型硅层的厚度为100nm-200nm。

19、优选地,多晶硅层的厚度为100nm-200nm。

20、与现有技术相比,本发明的有益效果是:

21、本发明提出了一种新的电光调变器的结构设计,在p型硅层上以磊晶制程设置p型载子掺杂的硅化锗层,硅化锗层是外延结构,其ge含量有其饱和值,太高差向异构长不出来,利用ge比si原子大,产生晶格拉伸,应力会比纯的p型硅原子大,因此其会有应变力作用在p型的硅层,减少电洞的有效质量;同样的,在应变氮化硅层上以磊晶制程设置n型硅层;应变氮化硅层会有应变力作用在n型硅层,减少电子的有效质量;此将更多地增强n型硅层的折射率;因此,应变氮化硅层及应变p型载子掺杂的硅化锗层,将更多地增强折射率的变化以增强光波的相位调变。

22、本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

技术特征:

1.一种硅光子学系统中的新式的电光调变器,其特征在于,包括集成光路,集成光路上具有硅片;

2.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,中介绝缘层为三明治结构,其采用氧化硅、氧化铝、氧化锆或氧化铪材料制成。

3.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,p型硅层和多晶硅层均延伸有接电部,偏置电压与接电部电连接。

4.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,二氧化硅层的厚度为120nm-200nm。

5.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,p型硅层的厚度为100nm-200nm。

6.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,硅化锗层的厚度为10nm-25nm。

7.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,中介绝缘层的厚度为2nm-10nm。

8.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,应变氮化硅层的厚度为8nm-20nm。

9.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,n型硅层的厚度为100nm-200nm。

10.根据权利要求1所述的一种硅光子学系统中的新式的电光调变器,其特征在于,多晶硅层的厚度为100nm-200nm。

技术总结

本发明涉及半导体技术领域,尤其是涉及一种硅光子学系统中的新式的电光调变器,包括集成光路,集成光路上具有硅片;在集成光路上以半导体制程技术,在硅片上设置二氧化硅层;在集成光路上以半导体制程技术,在硅氧化层上以磊晶制程设置P型硅层;在集成光路上以半导体制程技术,在P型硅层上以磊晶制程设置掺杂P型载子的硅化锗层;在集成光路上以半导体制程技术,在硅化锗层上设置中介绝缘层;在集成光路上以半导体制程技术,在中介绝缘层上设置应变氮化硅层;在集成光路上以半导体制程技术,在应变氮化硅层上以磊晶制程设置N型硅层;应变氮化硅层及应变P型载子掺杂的硅化锗层,将更多地增强折射率的变化以增强光波的相位调变。

技术研发人员:许晋铭,杨建荣

受保护的技术使用者:许晋铭

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!