半导体装置及其制造方法与流程

半导体装置及其制造方法

1.相关申请案的引用

2.本技术案基于2021年06月21日申请的在先日本专利申请第2021-102722号的优先权的利益,且谋求所述利益,所述内容全体以引用的方式包含于此。

技术领域

3.本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术:

4.在半导体装置的半导体层包含氢的情况下,大多期望降低半导体层内的氢原子浓度。

技术实现要素:

5.一实施方式提供一种能降低半导体层内的氢原子浓度的半导体装置及其制造方法。

6.根据一实施方式,半导体装置具备:积层膜,包含于第1方向交替积层的多个电极层及多个绝缘层;及柱状部,包含在所述积层膜内于所述第1方向延伸的电荷存储层及第1半导体层。所述装置还具备设置于所述积层膜及所述柱状部上的第2半导体层,所述第2半导体层内的至少一部分区域包含1.0

×

10

21

cm-3

以上的原子浓度的磷与1.0

×

10

19

cm-3

以下的原子浓度的氢。

7.根据所述构成,能提供一种能降低半导体层内的氢原子浓度的半导体装置及其制造方法。

附图说明

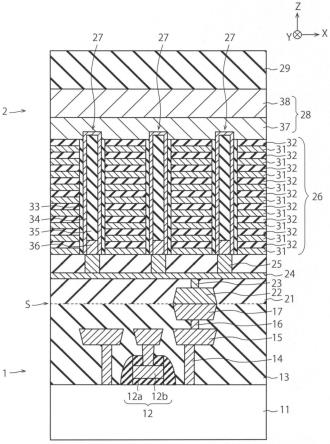

8.图1为表示第1实施方式的半导体装置的构造的剖视图。

9.图2为表示第1实施方式的半导体装置的构造的放大剖视图。

10.图3为表示第1实施方式的半导体装置的整体构造的剖视图。

11.图4(a)、(b)为表示第1实施方式的半导体装置的制造方法的剖视图(1/5)。

12.图5(a)、(b)为表示第1实施方式的半导体装置的制造方法的剖视图(2/5)。

13.图6(a)、(b)为表示第1实施方式的半导体装置的制造方法的剖视图(3/5)。

14.图7(a)、(b)为表示第1实施方式的半导体装置的制造方法的剖视图(4/5)。

15.图8(a)、(b)为表示第1实施方式的半导体装置的制造方法的剖视图(5/5)。

16.图9(a)、(b)为表示第1实施方式的变化例的半导体装置的制造方法的剖视图。

17.图10(a)~(c)为用以对第1实施方式的比较例的半导体层37的性质进行说明的示意图。

18.图11(a)~(c)为用以对第1实施方式的半导体层37的性质进行说明的示意图。

19.图12(a)、(b)为用以对第1实施方式的比较例的半导体层37的性质进行说明的图

表。

20.图13(a)、(b)为用以对第1实施方式的半导体层37的性质进行说明的图表。

21.图14(a)、(b)为表示第2实施方式的半导体装置的制造方法的剖视图(1/2)。

22.图15(a)、(b)为表示第2实施方式的半导体装置的制造方法的剖视图(2/2)。

23.图16(a)、(b)为用以对第2实施方式的半导体层37的性质进行说明的剖视图。

24.图17为表示第3实施方式的半导体装置的制造方法的俯视图。

25.图18为表示第3实施方式的半导体装置的整体构造的剖视图。

具体实施方式

26.以下,参考附图说明本发明的实施方式。在图1~图18中,对相同的构成标注相同的符号,并省略重复的说明。

27.(第1实施方式)图1为表示第1实施方式的半导体装置的构造的剖视图。图1的半导体装置例如为3维快闪存储器。

28.图1的半导体装置具备包含cmos(complementary metal oxide semiconductor:互补金属氧化物半导体)电路的电路区域1、与包含存储器单元阵列的阵列区域2。存储器单元阵列具备存储数据的多个存储器单元,cmos电路具备控制存储器单元阵列的动作的外围电路。图1的半导体装置例如如后所述,通过将包含电路区域1的电路晶圆、与包含阵列区域2的阵列晶圆贴合而制造。符号s表示电路区域1与阵列区域2的贴合面。

29.图1表示互相垂直的x方向、y方向、及z方向。在所述说明书中,将+z方向处理为上方向,将-z方向处理为下方向。例如,cmos区域1由于图示在阵列区域2的-z方向,所以位于阵列区域2的下方。另外,-z方向可与重力方向一致,也可与重力方向不一致。z方向为第1方向的例。

30.在图1中,电路区域1具备衬底11、晶体管12、层间绝缘膜13、多个接触插塞14、包含多根配线的配线层15、通孔插塞16、及金属垫17。图1表示配线层15内的多根配线中的3根、与设置于所述配线下的3个接触插塞14。衬底11为第1衬底的例。金属垫17为第1垫的例。

31.在图1中,阵列区域2具备层间绝缘膜21、金属垫22、通孔插塞23、包含多根配线的配线层24、多个接触插塞25、积层膜26、多个柱状部27、源极层28、及绝缘膜29。图1表示配线层24内的多根配线中的1根、与设置于所述配线上的3个接触插塞25及3个柱状部27。金属垫22为第2垫的例。

32.此外,积层膜26包含多个电极层31与多个绝缘层32。各柱状部27包含存储器绝缘膜33、通道半导体层34、核心绝缘膜35、及核心半导体层36。源极层28包含着半导体层37与金属层38。通道半导体层34为第1半导体层的例。半导体层37为第2半导体层的例。

33.以下,参考图1,说明本实施方式的半导体装置的构造。

34.衬底11例如为si(硅)衬底等半导体衬底。晶体管12设置于衬底11上,包含着栅极绝缘膜12a及栅极电极12b。晶体管12例如构成所述cmos电路。层间绝缘膜13以覆盖晶体管12的方式形成于衬底11上。层间绝缘膜13例如为sio2膜(氧化硅膜)、或包含sio2膜与其它绝缘膜的积层膜。

35.接触插塞14、配线层15、通孔插塞16、及金属垫17形成于层间绝缘膜13内。具体而言,接触插塞14配置在衬底11上、或晶体管12的栅极电极12b上。图1中,衬底11上的接触插

塞14设置于晶体管12的源极区域及漏极区域(未图示)上。配线层15配置在接触插塞14上。通孔插塞16配置在配线层15上。金属垫17在衬底11的上方,配置在通孔插塞16上。金属垫17例如为cu(铜)层。

36.层间绝缘膜21形成于层间绝缘膜13上。层间绝缘膜21例如为sio2膜、或包含sio2膜与其它绝缘膜的积层膜。

37.金属垫22、通孔插塞23、配线层24、及接触插塞25形成于层间绝缘膜21内。具体而言,金属垫22在衬底11的上方,配置在金属垫17上。金属垫22例如为cu层。通孔插塞23配置在金属垫22上。配线层24配置在通孔插塞23上。图1表示配线层24内的多根配线中的1根,所述配线例如作为位线发挥功能。接触插塞25配置在配线层24上。

38.积层膜26设置于层间绝缘膜21上,包含于z方向交替积层的多个电极层31及多个绝缘层32。电极层31例如为包含w(钨)层的金属层,作为字线发挥功能。绝缘层32例如为sio2膜。在本实施方式中,所述多个电极层31彼此具有相同厚度,所述多个绝缘层32彼此也具有相同厚度。但,所述绝缘层32中的最上层的绝缘层32的厚度可比其它绝缘层32的厚度厚。

39.各柱状部27设置于积层膜26内,包含着存储器绝缘膜33、通道半导体层34、核心绝缘膜35、及核心半导体层36。存储器绝缘膜33形成于积层膜26的侧面,具有于z方向延伸的管状的形状。通道半导体层34形成于存储器绝缘膜33的侧面,具有于z方向延伸的管状的形状。核心绝缘膜35与核心半导体层36形成于通道半导体层34的侧面,具有于z方向延伸的棒状的形状。具体而言,核心半导体层36配置在接触插塞25上,核心绝缘膜35配置在核心半导体层36上。

40.存储器绝缘膜33如后所述,例如依序包含着阻挡绝缘膜、电荷存储层、及隧道绝缘膜。阻挡绝缘膜例如为sio2膜。电荷存储层例如为sin膜(氮化硅膜)。隧道绝缘膜例如为sio2膜或sion膜(氮氧化硅膜)。通道半导体层34例如为多晶硅层等多晶半导体层。核心绝缘膜35例如为sio2膜。核心半导体层36例如为多晶硅层等多晶半导体层。所述存储器单元阵列内的各存储器单元由通道半导体层34、电荷存储层、电极层31等构成。

41.各柱状部27内的通道半导体层34设置于比金属垫22高的位置,但经由核心半导体层36、接触插塞25、配线层24、及通孔插塞23电性连接于金属垫22。因此,阵列区域2内的存储器单元阵列经由金属垫22或金属垫17,与电路区域1内的外围电路电性连接。由此,能通过外围电路控制存储器单元阵列的动作。

42.源极层28包含依序形成于积层膜26及柱状部27上的半导体层37及金属层38,作为源极线发挥功能。在本实施方式中,各柱状部27的通道半导体层34从存储器绝缘膜33露出,半导体层37直接形成于通道半导体层34上。此外,金属层38直接形成于半导体层37上。因此,源极层28电性连接于各柱状部27的通道半导体层34。半导体层37例如为多晶硅层等多晶半导体层。金属层38例如包含w层、cu层、或al(铝)层。

43.绝缘膜29形成于源极层28上。绝缘膜29例如为sio2膜。

44.此处,对本实施方式的半导体装置包含的杂质原子进行说明。

45.本实施方式的半导体层37作为杂质原子,包含p(磷)原子与h(氢)原子。在本实施方式中,半导体层37内的p原子浓度为1.0

×

10

21

cm-3

以上,半导体层37内的h原子浓度为1.0

×

10

19

cm-3

以下。对于本实施方式的半导体层37包含此种杂质原子的理由予以后述。

46.另外,p原子浓度为1.0

×

10

21

cm-3

以上,h原子浓度为1.0

×

10

19

cm-3

以下的条件可在半导体层37内的全域内成立,也可仅在半导体层37内的一部分区域成立。后者的情况下,半导体层37可包括包含多晶硅层等多晶半导体层的多晶区域、与包含非晶硅层等非晶半导体层的非晶区域,所述条件可仅在半导体层37内的多晶区域成立。另一方面,非晶区域内的h原子浓度可比1.0

×

10

19

cm-3

高。关于此种浓度分布的进一步的细节予以后述。

47.另外,1.0

×

10

21

cm-3

的p原子浓度表示每1cm3的p原子的个数为1.0

×

10

21

atoms。同样地,1.0

×

10

19

cm-3

的h原子浓度表示每1cm3的h原子的个数为1.0

×

10

19

atoms。

48.图2为表示第1实施方式的半导体装置的构造的放大剖视图。

49.图2表示积层膜26内所包含的3个电极层31及3个绝缘层32、与设置于积层膜26内的1个柱状部27。所述柱状部27内的存储器绝缘膜33如上所述,包含依序形成于积层膜26的侧面的阻挡绝缘膜33a、电荷存储层33b、及隧道绝缘膜33c。阻挡绝缘膜33a例如为sio2膜。电荷存储层33b例如为sin膜。隧道绝缘膜33c例如为sio2膜或sion膜。

50.另一方面,各电极层31包含势垒金属层31a与电极材层31b。势垒金属层31a例如为tin膜(氮化钛膜)。电极材层31b例如为w膜。本实施方式的各电极层31如图2所示,介隔阻挡绝缘膜39,形成于上部的绝缘层32的下表面、下部的绝缘层32的上表面、及阻挡绝缘膜33a的侧面。阻挡绝缘膜39例如为al2o3膜(氧化铝膜),与阻挡绝缘膜33a一起作为各存储器单元的阻挡绝缘膜发挥功能。如此,本实施方式的积层膜26除电极层31及绝缘层32外,还包含阻挡绝缘膜39。阻挡绝缘膜39、势垒金属层31a、及电极材层31b依序形成于上部的绝缘层32的下表面、下部的绝缘层32的上表面、及阻挡绝缘膜33a的侧面。

51.图3为表示第1实施方式的半导体装置的整体构造的剖视图。

52.电路区域1如图3所示,具备衬底11、多个晶体管12、层间绝缘膜13、多个接触插塞14、包含多根配线的配线层15、多个通孔插塞16、及多个金属垫17。电路区域1内的所述构成要素的细节如参考图1所说明。

53.电路区域1如图3所示,还具备包含多根配线的配线层15’、与包含多根配线的配线层15”。图3中,于配线层15上设置着配线层15’,于配线层15’上设置着配线层15”,于配线层15”上设置着通孔插塞16。电路区域1在图3中具备3个配线层15、15’、15”,但电路区域1内的配线层的数量也可为3个以外。

54.阵列区域2如图3所示,具备层间绝缘膜21、多个金属垫22、多个通孔插塞23、包含多根配线的配线层24、接触插塞25、积层膜26、多个柱状部27、源极层28、及绝缘膜29。图3表示所述多个接触插塞25中的1个接触插塞25。积层膜26包含多个电极层31及多个绝缘层32。各柱状部27包含未图示的存储器绝缘膜33、通道半导体层34、核心绝缘膜35、及核心半导体层36(参考图1)。源极层28包含半导体层37及金属层38。阵列区域2内的所述构成要素的细节如参考图1所说明。

55.阵列区域2如图3所示,还具备包含多根配线的配线层24’。图3中,于通孔插塞23上设置着配线层24’,于配线层24’上设置着配线层24。阵列区域2在图3中具备2个配线层24、24’,但阵列区域2内的配线层的数量也可为2个以外。

56.阵列区域2还具备在层间绝缘膜21内设置于绝缘膜29下的存储器单元阵列41。存储器单元阵列41包含积层膜26、柱状部27、及源极层28等。积层膜26内的各电极层31作为字线wl发挥功能,源极层28作为源极线sl发挥功能。

57.存储器单元阵列41包含阶梯构造部42。各字线wl经由接触插塞43与字线配线层44电性连接。另一方面,各柱状部27经由接触插塞25与位线bl电性连接,且与源极线sl电性连接。本实施方式的字线配线层44与位线bl包含于配线层24内。

58.阵列区域2还具备设置于配线层24上的多个通孔插塞45、设置于所述通孔插塞45及绝缘膜29上的金属垫46、及设置于金属垫46及绝缘膜29上的钝化膜47。

59.金属垫46例如为cu层或al层,作为本实施方式的半导体装置的外部连接垫(接合垫)发挥功能。钝化膜47例如为sio2膜等绝缘膜,具有使金属垫46的上表面露出的开口部p。金属垫46能经由所述开口部p,通过接合线、焊料球、金属凸块等电性连接于安装衬底或其它装置。

60.图4~图8为表示第1实施方式的半导体装置的制造方法的剖视图。

61.图4(a)表示用以制造阵列区域2的阵列晶圆w2。制造阵列区域2时,首先于衬底51上形成绝缘膜52,于绝缘膜52上交替形成多个牺牲层31’与多个绝缘层32(图4(a))。结果,于绝缘膜52上形成积层膜26’。积层膜26’包含于z方向上交替积层的多个牺牲层31’与多个绝缘层32。衬底51例如为si衬底等半导体衬底。衬底51为第2衬底的例。绝缘膜52例如为sin膜。牺牲层31’例如为sin膜。

62.接着,形成贯通积层膜26’及绝缘膜52的多个存储器孔h1,并于各存储器孔h1内依序形成存储器绝缘膜33、通道半导体层34、及核心绝缘膜35(图4(a))。结果,于所述存储器孔h1内,形成于z方向延伸的多个柱状部27。存储器绝缘膜33通过于各存储器孔h1内依序形成阻挡绝缘膜33a、电荷存储层33b、及隧道绝缘膜33c而形成(参考图2)。

63.接着,于积层膜26’及柱状部27上形成绝缘膜53(图4(a))。绝缘膜53例如为sio2膜。

64.接着,形成贯通绝缘膜53及积层膜26’的缝隙(未图示),通过使用缝隙的湿蚀刻去除牺牲层31’(图4(b))。结果,于积层膜26’内的绝缘层32间形成多个空洞h2。

65.接着,从缝隙于所述空洞h2内形成多个电极层31(图5(a))。结果,包含于z方向上交替积层的多个电极层31与多个绝缘层32的积层膜26形成于绝缘膜52与绝缘膜53之间。此外,于衬底51的上方,形成所述多个柱状部27贯通积层膜26的构造。另外,在各空洞h2内形成电极层31时,于各空洞h2内依序形成阻挡绝缘膜39、势垒金属层31a、及电极材层31b(参考图2)。

66.接着,去除绝缘膜53,去除各柱状部27内的核心绝缘膜35的一部分,并于去除核心绝缘膜35的一部分的区域埋入核心半导体层36(图5(b))。结果,各柱状部27被加工成包含存储器绝缘膜33、通道半导体层34、核心绝缘膜35、及核心半导体层36的构造。

67.接着,于积层膜26及柱状部27上形成层间绝缘膜21、金属垫22、通孔插塞23、配线层24、及多个接触插塞25(图5(b))。此时,所述接触插塞25形成于各自对应的柱状部27的核心半导体层36上,配线层24、通孔插塞23、及金属垫22依序形成于所述接触插塞25上。

68.图6(a)表示用以制造电路区域1的电路晶圆w1。图6(a)所示的电路晶圆w1通过在衬底11上形成晶体管12、层间绝缘膜13、多个接触插塞14、配线层15、通孔插塞16、及金属垫17而制造(参考图1)。此时,晶体管12形成于衬底1上,所述接触插塞14形成于衬底1上或晶体管12上。此外,配线层15、通孔插塞16、及金属垫17依序形成于所述接触插塞14上。衬底11为第1衬底的例。

69.接着,使阵列晶圆w2的朝向反转,通过机械性压力将电路晶圆w1与阵列晶圆w2贴合(图6(a))。结果,将层间绝缘膜13与层间绝缘膜21接着。接着,对电路晶圆w1与阵列晶圆w2进行退火(图6(a))。结果,将金属垫17与金属垫22接合。如此,衬底51上的金属垫22贴合于衬底11上的金属垫17,衬底51上的层间绝缘膜21贴合于衬底11上的层间绝缘膜13,衬底51积层于衬底11的上方。

70.接着,去除衬底51(图6(b))。结果,绝缘膜52或各柱状部27露出于衬底11的上方。衬底51例如通过cmp(chemical mechanical polishing:化学机械抛光)去除。在图6(b)的工序中,除了通过cmp去除衬底51外,还可通过cmp将衬底11薄膜化。

71.接着,通过蚀刻去除绝缘膜52、或各柱状部27的存储器绝缘膜33的一部分(图7(a))。存储器绝缘膜33的被去除的部分例如为从积层膜26露出的部分。结果,各柱状部27的通道半导体层34的一部分在比积层膜26高的位置上,从存储器绝缘膜33露出。

72.接着,于积层膜26及柱状部27上,形成源极层28的半导体层37(图7(b))。结果,由于半导体层37形成于各柱状部27的通道半导体层34上,所以半导体层37电性连接于各柱状部27的通道半导体层34。

73.在图7(b)的工序中,半导体层37作为非晶半导体层形成。所述非晶半导体层例如为a-si(非晶硅)层。在本实施方式中,例如,使用包含si(硅)元素与h(氢)元素的源极气体形成作为a-si层的半导体层37。因此,图7(b)的工序中形成的半导体层37包含h原子作为杂质原子。期望使所述h原子从半导体层37脱离。

74.因此,本实施方式的半导体层37在图7(b)的工序中,作为除h原子外还包含p原子的非晶半导体层(例如a-si层)形成。由此,如后所述,能促进h原子从半导体层37脱离。在本实施方式中,例如,使用包含si元素与h元素的源极气体、及包含p元素与h元素的源极气体形成此种半导体层37。所述源极气体的例为sih4气体与ph3气体。在图7(b)的工序中,半导体层37例如以400℃以下形成。由此,能抑制形成半导体层37时的热对金属垫17、22造成不良影响。

75.在图7(b)的工序结束的阶段,半导体层37内的h原子浓度例如比1.0

×

10

19

cm-3

高。所述阶段的h原子浓度的具体例比1.0

×

10

19

cm-3

高,且为1.0

×

10

20

cm-3

以下。所述情况下,期望使h原子从半导体层37脱离,以降低半导体层37内的h原子浓度。

76.另外,在图7(b)的工序结束的阶段,半导体层37内的p原子浓度例如比1.0

×

10

21

cm-3

低。所述阶段的p原子浓度的具体例比1.0

×

10

21

cm-3

低,且为1.0

×

10

19

cm-3

以上。所述情况下,为了充分促进h原子从半导体层37脱离,期望提高半导体层37内的p原子浓度。因此,本实施方式中,在后述工序中,对半导体层37内进一步注入p原子。

77.在图7(b)的工序中,例如,能通过调整sih4气体与ph3气体的流量比,控制半导体层37内的p原子浓度及h原子浓度。在本实施方式中,例如,将ph3气体的流量相对于sih4气体的流量的比调整为0.03以上且0.35以下(0.03≦ph3/sih4≦0.35)。由此,能实现所述具体例的p原子浓度及h原子浓度。sih4气体的流量例如为360sccm。ph3气体的流量例如为9~126sccm。

78.接着,使用p(磷)离子,进行对半导体层37的离子注入(图8(a))。结果,对半导体层37内进一步注入p原子作为杂质原子。所述离子注入例如以半导体层37内的p原子浓度成为1.0

×

10

21

cm-3

以上的方式进行。由此,在后述工序中,能充分促进h原子从半导体层37脱离。

另外,在图8(a)的工序中,例如,能通过调整离子注入的持续时间、功率、焦距、流量等,控制半导体层37内的p原子浓度。

79.接着,对半导体层37进行退火(图8(b))。所述退火例如为激光退火。结果,使半导体层37结晶化,从非晶半导体层变化为多晶半导体层。结晶化后的半导体层37例如为多晶硅层。于所述退火时,半导体层37内的至少一部分h原子从半导体层37脱离,半导体层37内的h原子的浓度降低。所述退火例如以半导体层37内的h原子浓度成为1.0

×

10

19

cm-3

以下的方式进行。根据本实施方式,由高浓度的p原子充分促进h原子从半导体层37脱离,由此能将h原子浓度设为此种低浓度。

80.如此,在本实施方式中,为了使作为杂质原子的h原子从半导体层37脱离,于半导体层37内导入作为其它杂质原子的p原子。p原子在图7(b)的工序中形成半导体层37时、与图8(a)的工序中对半导体层37内注入p离子时,被导入到半导体层37内。在本实施方式中,所述p原子最终残存于半导体层37内,也就是制造后的(完成品的)半导体装置的半导体层37内。在制造后的半导体装置中,半导体层37内的p原子浓度例如为1.0

×

10

21

cm-3

以上,半导体层37内的h原子浓度例如为1.0

×

10

19

cm-3

以下。关于本实施方式的半导体层37的进一步的细节,予以后述。

81.接着,于半导体层37上形成源极层28的金属层38,于金属层38上形成绝缘膜29(图8(b))。

82.之后,将电路晶圆w1及阵列晶圆w2切断为多个芯片。所述芯片以各芯片包含电路区域1与阵列区域2的方式被切断。如此,制造图1的半导体装置。

83.图9为表示第1实施方式的变化例的半导体装置的制造方法的剖视图。

84.图9(a)及图9(b)的工序分别与图8(a)及图8(b)的工序对应。所述图7(b)所示的半导体层37也可因柱状部27的突出部,而形成为具有凹凸的上表面。图9(a)表示如此形成的半导体层37。在所述情况下,对所述半导体层37进行离子注入(图9(a)),还对所述半导体层37进行退火(图9(b))。之后,于半导体层37上形成金属层38,于金属层38上形成绝缘膜29,并通过cmp将绝缘膜29的上表面平坦化。另外,也可省略所述cmp。

85.以下,参考图10~图13,比较第1实施方式的半导体层37、与所述比较例的半导体层37。

86.图10为用以对第1实施方式的比较例的半导体层37的性质进行说明的示意图。

87.图10(a)表示本比较例的半导体层37所包含的si原子、p原子、及h原子。在本比较例中,通过图7(b)的工序形成半导体层37,但不对半导体层37进行图8(a)所示的p离子注入。因此,本比较例的半导体层37在图8(b)中的退火前,包含浓度比1.0

×

10

21

cm-3

低的p原子、与浓度比1.0

×

10

19

cm-3

高的h原子。在图10(a)中,si原子形成晶格,p原子或h原子进入所述晶格与si原子键合。

88.图10(b)表示图8(b)中的退火过程中的本比较例的半导体层37。通过所述退火,切断si原子、p原子、及h原子之间的键合。结果,半导体层37内的一部分h原子在退火过程中或退火后从半导体层37脱离,并从半导体层37作为h2分子释放出。由此,半导体层37内的h原子浓度降低。

89.图10(c)表示图8(b)中的退火后的本比较例的半导体层37。本比较例的半导体层37通过退火而冷却,从非晶半导体层变化为多晶半导体层。未从半导体层37脱离的h原子与

半导体层37内的si原子再键合、或在半导体层37内成为h2分子。担心后者的h原子(h2分子)于半导体层37内形成空隙。由于此种空隙会导致半导体层37断线或高电阻化,所以非优选。

90.此处,对本比较例的半导体层37内的p原子进行说明。

91.如图10(a)所示,p原子与h原子同样与si原子键合。因此,于形成半导体层37时,如果半导体层37内的p原子浓度变高,那么半导体层37内的h原子浓度容易变低。原因在于如果p原子与si原子键合,那么能与h原子键合的si原子的数量减少,导致h原子难以与si原子键合。本比较例的半导体层37虽包含p原子,但具有不满1.0

×

10

21

cm-3

的低p原子浓度。因此,本比较例的半导体层37于退火前具有超过1.0

×

10

19

cm-3

的高h原子浓度。结果,本比较例的半导体层37内的h原子浓度于退火后也变高。

92.本比较例的半导体层37内的p原子浓度于通过图7(b)的工序形成半导体层37时,能通过增大ph3气体的流量而变高。然而,ph3气体中的p原子以ph离子的形态进入半导体层37内。因此,如果以这种方法使半导体层37内的p原子浓度变高,那么半导体层37内的h原子浓度也变高。因此,在本比较例中,将半导体层37内的p原子浓度设定得比1.0

×

10

21

cm-3

低。

93.图11为用以对第1实施方式的半导体层37的性质进行说明的示意图。

94.图11(a)表示本实施方式的半导体层37所包含的si原子、p原子、及h原子。在本实施方式中,通过图7(b)的工序形成半导体层37,还对半导体层37进行图8(a)所示的p离子注入。因此,本实施方式的半导体层37在图8(b)中的退火前,包含1.0

×

10

21

cm-3

以上浓度的p原子、与浓度比1.0

×

10

19

cm-3

高的h原子。图11(a)区分表示通过图7(b)的工序导入的p原子、与通过图8(a)的工序导入的p原子。在图11(a)中,前者的p原子或h原子与si原子键合进入晶格,后者的p原子不与si原子键合而进入晶格。

95.图11(b)表示图8(b)的退火过程中的本实施方式的半导体层37。通过所述退火,切断si原子、p原子、及h原子之间的键合。结果,半导体层37内的一部分h原子在退火过程中或退火后从半导体层37脱离,从半导体层37作为h2分子释放出。由此,半导体层37内的h原子浓度降低。

96.图11(c)表示图8(b)中的退火后的本实施方式的半导体层37。本实施方式的半导体层37通过退火而冷却,从非晶半导体层变化为多晶半导体层。未从半导体层37脱离的h原子与半导体层37内的si原子再键合、或在半导体层37内成为h2分子。担心后者的h原子(h2分子)于半导体层37内形成空隙。由于此种空隙会导致半导体层37断线或高电阻化,所以非优选。另外,在图11(c)中,通过p离子注入导入的p原子也与半导体层37内的si原子键合。

97.此处,对本实施方式的半导体层37内的p原子进行说明。

98.本实施方式的半导体层37于退火前具有所谓1.0

×

10

21

cm-3

以上的高p原子浓度。在本实施方式中,除了图7(b)的工序中的p原子导入外,还通过图7(b)及图8(a)的工序中的p原子导入,实现此种高p原子浓度。由此,能将退火前的h原子浓度限制为与比较例同等程度,且提高退火前的p原子浓度。

99.在本实施方式的半导体层37的退火后,si原子除了通过图7(b)的工序导入的p原子外,还与通过图8(a)的工序导入的p原子键合。结果,h原子容易从半导体层37脱离,半导体层37内的h原子浓度大幅降低。由此,能将半导体层37内的h原子浓度设为1.0

×

10

19

cm-3

以下的低浓度,能抑制产生半导体层37内的空隙。

100.图12为用以对第1实施方式的比较例的半导体层37的性质进行说明的图表。

101.图12(a)表示本比较例的半导体层37内的各个部位的h浓度。图12(a)的横轴表示半导体层37内的各部位的深度,也就是半导体层37的上表面到半导体层37内的各部位的z方向的距离。图12(a)的纵轴表示半导体层37内的各部位的h原子浓度。因此,图12(a)表示本比较例的半导体层37内的h原子的浓度分布。

102.在图12(a)中,曲线a1表示在图7(b)的工序中形成半导体层37时的h原子浓度,曲线a2表示在图8(b)中对半导体层37进行退火后的h原子浓度。根据曲线a2,半导体层37内的h原子浓度在深度100nm附近变高。认为这是因为在半导体层37内的深度100nm附近,产生了空隙。

103.图12(b)表示本比较例的半导体层37内的各个部位的p浓度。图12(b)与图12(a)同样,表示本比较例的半导体层37内的p原子的浓度分布。

104.图12(b)中,曲线b1表示在图7(b)的工序中形成半导体层37时的p原子浓度,曲线b2表示在图8(b)中对半导体层37进行退火后的p原子浓度。本比较例的半导体层37内的p原子浓度在任何深度都比1.0

×

10

21

cm-3

低。

105.图13为用以对第1实施方式的半导体层37的性质进行说明的图表。

106.图13(a)表示本实施方式的半导体层37内的各个部位的h浓度。图13(a)与图12(a)及图12(b)同样,表示本实施方式的半导体层37内的h原子的浓度分布。

107.在图13(a)中,曲线c1表示在图7(b)的工序中形成半导体层37时的h原子浓度,曲线c2表示在图8(b)中对半导体层37进行退火后的h原子浓度。曲线c2所示的h原子浓度几乎在任何深度都比曲线c1所示的h原子浓度低。认为这是因为对半导体层37进行了图8(a)所示的p离子注入。

108.图13(b)表示本实施方式的半导体层37内的各个部位的p浓度。图13(b)与图12(a)~图13(a)同样,表示本比较例的半导体层37内的p原子的浓度分布。

109.图13(b)中,曲线d1表示在图7(b)的工序中形成半导体层37时的p原子浓度,曲线d2表示在图8(b)中对半导体层37进行退火后的p原子浓度。本比较例的半导体层37内的p原子浓度在120nm以内的几乎任何深度都为1.0

×

10

21

cm-3

以上。

110.如上所述,在本实施方式中,形成包含p原子及h原子的半导体层37,之后还对半导体层37内注入p原子。因此,根据本实施方式,通过之后的退火,能充分降低半导体层37内的h原子浓度。根据本实施方式,能形成包含1.0

×

10

21

cm-3

以上的原子浓度的p原子、与1.0

×

10

19

cm-3

以下的原子浓度的h原子的半导体层37。此外,根据本实施方式,通过导入p原子实现h原子的脱离,由此能将半导体层37设为n型半导体层。

111.(第2实施方式)图14及图15为表示第2实施方式的半导体装置的制造方法的剖视图。

112.图14(a)与图8(a)同样,表示对半导体层37的p离子注入。本实施方式的半导体装置的制造方法从图4(a)的工序到图8(a)的工序,与第1实施方式的半导体装置的制造方法同样地进行。图14(a)所示的半导体层37例如包含1.0

×

10

21

cm-3

以上的浓度的p原子、与浓度比1.0

×

10

19

cm-3

高的h原子。

113.接着,于半导体层37上形成下部膜61a,于下部膜61a上形成上部膜61b(图14(b))。结果,包含下部膜61a与上部膜61b的盖层61形成于半导体层37上。下部膜61a例如为sio2膜。上部膜61b例如为sin膜。盖层61为第1层的例。下部膜61a及上部膜61b分别为第1膜及第

2膜的例。

114.接着,对半导体层37进行退火(图14(b))。所述退火与图8(b)中的退火同样地进行。结果,半导体层37结晶化,从非晶半导体层变化为多晶半导体层。于所述退火时,半导体层37内的至少一部分h原子从半导体层37脱离,半导体层37内的h原子的浓度降低。所述退火例如以半导体层37内的h原子浓度成为1.0

×

10

19

cm-3

以下的方式进行。根据本实施方式,由高浓度的p原子充分促进h原子从半导体层37脱离,由此能将h原子浓度设为此种低浓度。

115.接着,从半导体层37的上表面去除盖层61(图15(a))。接着,于半导体层37上形成源极层28的金属层38,于金属层38上形成绝缘膜29(图15(b))。

116.之后,将电路晶圆w1及阵列晶圆w2切断为多个芯片。所述芯片以各芯片包含电路区域1与阵列区域2的方式被切断。如此,制造图1的半导体装置。

117.图16为用以对第2实施方式的半导体层37的性质进行说明的剖视图。

118.图16(a)表示在于半导体层37上未设置盖层61的状态下,进行图14(b)中的退火的状况,作为本实施方式的比较例。在所述退火中,半导体层37熔解。因此,担心在冷却半导体层37后,于半导体层37的上表面产生凹凸。原因在于半导体层37的上表面未由盖层61盖住。另外,由于半导体层37的上表面未由盖层61盖住,所以如图16(a)所示,半导体层37内的h2气体的气泡62容易成为空隙63。

119.图16(b)表示如本实施方式般,在于半导体层37上设置着盖层61的状态下,进行图14(b)中的退火的状况。此种情况下,由于半导体层37的上表面由盖层61压住,所以即便半导体层37熔解并冷却,也能抑制在半导体层37的上表面产生凹凸。另外,由于即便气泡62成为空隙63,空隙63的生长也受盖层61阻碍,所以能抑制产生空隙63。

120.另外,盖层61也可在对半导体层37注入p离子前,形成于半导体层37上。但,在对半导体层37注入p离子后形成盖层61有容易将p离子注入半导体层37内的优点。

121.(第3实施方式)图17为表示第3实施方式的半导体装置的制造方法的俯视图。

122.本实施方式的半导体装置与第1实施方式的半导体装置同样,通过图4(a)~图8(b)的工序制造。图17表示图8(b)的工序结束,且被切断为多个芯片前的电路晶圆w1及阵列晶圆w2的平面构造。

123.本实施方式的电路晶圆w1及阵列晶圆w2具备多个器件区域r1、与逐一包围所述器件区域r1的切割区域r2。各器件区域r1于所述切断后成为1个半导体装置(1个芯片)。各器件区域r1包含1个电路区域1、与1个阵列区域2(参考图1)。切割区域r2为于所述切断时供切割机抵接的区域。切割区域r2也称为划线区域或切槽区域。

124.各器件区域r1具备多个存储器部71、多个切槽切割部72、及边缘密封部73。各存储器部71包含存储器单元阵列41或晶体管12(参考图3)。各切槽切割部72与对应的存储器部71相邻而设置。边缘密封部73沿各器件区域r1的4条边(边缘)设置,具有包围存储器部71及切槽切割部72的环状的平面形状。边缘密封部73例如包含用以密封各器件区域r1的保护环。

125.图18为表示第3实施方式的半导体装置的整体构造的剖视图。

126.图18表示沿图17所示的线l的制造后的(完成后的)半导体装置的剖面。因此,图18表示1个存储器部71、1个切槽切割部72、及1个边缘密封部73的剖面。图18所示的存储器部71具有与图3所示的构造同样的构造。

127.切槽切割部72具备设置于电路区域1内的金属部81、与设置于阵列区域2内的金属部82。金属部81设置于衬底11上,贯通层间绝缘膜13。金属部82设置于金属部81上,贯通层间绝缘膜21、源极层28、及绝缘膜29。切槽切割部72还具备设置于金属部82上,由钝化膜47覆盖的金属垫46。

128.边缘密封部73具备设置于电路区域1内的金属部83、与设置于阵列区域2内的金属部84。金属部83设置于衬底11上,贯通层间绝缘膜13。金属部84设置于金属部83上,贯通层间绝缘膜21、源极层28、及绝缘膜29。边缘密封部73还具备设置于金属部82上,由钝化膜47覆盖的金属垫46。边缘密封部73内的金属部83、金属部84、及金属垫46例如形成保护环。

129.此外,金属部81、83例如以与接触插塞14、配线层15、配线层15’、配线层15”、通孔插塞16、及金属垫17相同的材料形成。另外,金属部82、84例如以与金属垫22、通孔插塞23、配线层24’、配线层24、及通孔插塞45相同的材料形成。

130.本实施方式的半导体层37包含设置于存储器部71内的区域37a、设置于切槽切割部72内的区域37b、及设置于边缘密封部73内的区域37c。区域37a为第1区域的例。区域37b、37c为第2区域的例。

131.以下,对本实施方式的半导体层37的2个例进行说明。

132.第1例中,区域37a、37b、37c都为多晶硅层等多晶半导体层,且包含1.0

×

10

21

cm-3

以上的原子浓度的p原子、与1.0

×

10

19

cm-3

以下的原子浓度的h原子。此种半导体层37例如能通过在图8(a)的工序中对半导体层37整体注入p离子,在图8(b)的工序中对半导体层37整体进行退火而形成。第1例中,有无需区分进行离子注入及退火的区域与不进行的区域等优点。

133.第2例中,区域37a为多晶硅层等多晶半导体层,且包含1.0

×

10

21

cm-3

以上的原子浓度的p原子、与1.0

×

10

19

cm-3

以下的原子浓度的h原子。另一方面,区域37b、37c为非晶硅层等非晶半导体层,包含原子浓度比1.0

×

10

19

cm-3

高的h原子。此种半导体层37例如能通过在图8(a)的工序中对半导体层37整体或仅对区域37a注入p离子,在图8(b)的工序中仅对区域37a进行退火而形成。在对半导体层37整体注入p离子的情况下,区域37b、37c内的p原子浓度为1.0

×

10

21

cm-3

以上。另一方面,在仅对区域37a注入p离子的情况下,区域37b、37c内的p原子浓度比1.0

×

10

21

cm-3

低。第2例中,通过将进行离子注入及退火的区域限定于区域37a,能避免对于区域37b、37c的无用的离子注入及退火。

134.第1及第2例中,进行退火的区域内的半导体层37在图8(b)的工序中从非晶半导体层变化为多晶半导体层,而不进行退火的区域内的半导体层37在图8(b)的工序中维持非晶半导体层。第1及第2例中,也可预先对进行退火的区域内注入p离子,不对不进行退火的区域内预先注入p离子。此外,所述区域也可以与第1及第2例不同的形式设定。例如,可仅对半导体层37内的区域37a、37b进行离子注入及退火。

135.图18表示衬底11的端面e1、与位于端面e1的上方的半导体层37的侧面e2。端面e1或侧面e2设置于边缘密封部73内,侧面e2相当于区域37c的侧面。端面e1或侧面e2位于图17中的器件区域r1与切割区域r2的边界。

136.第1例中,侧面e2中的半导体层37为多晶半导体层,包含1.0

×

10

21

cm-3

以上的原子浓度的p原子、与1.0

×

10

19

cm-3

以下的原子浓度的h原子。第2例中,侧面e2中的半导体层37为非晶半导体层,包含原子浓度比1.0

×

10

19

cm-3

高的h原子。另外,半导体层37于侧面e2的

一部分为多晶半导体层,于侧面e2的另一部分为非晶半导体层。

137.如上所述,本实施方式的半导体层37可仅包含多晶半导体层,也可包含多晶半导体层及非晶半导体层。另外,本实施方式的半导体层37也可具有因每个区域而异的p原子浓度及h原子浓度。

138.以上,虽已说明多个实施方式,但所述实施方式仅是作为例而提出的,并非意欲限定发明的范围。本说明书中说明的新颖的装置及方法可以其它各种方式实施。另外,对于本说明书中说明的装置及方法的方式,在未脱离发明的主旨的范围内,能进行各种省略、置换、变更。附加的权利要求范围及与其均等的范围意图包含发明范围或主旨所包含的此种方式或变化例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1