防静电涂层的制作方法

1.本发明涉及改进涂层以减少静电充电和放电以及生产这种涂层的方法。

背景技术:

2.多种沉积技术用于涂覆基底。气相沉积技术在各种类型的应用中通常用于形成薄膜沉积层,这些应用包括微电子应用和重防腐应用。这种沉积技术可分为两大类。这种沉积技术的第一类称为化学气相沉积(cvd)。cvd通常是指由于化学反应而发生的沉积工艺。cvd工艺的常见示例包括半导体硅层沉积、外延和热氧化。

3.第二类沉积通常称为物理气相沉积(pvd)。pvd通常是指由于物理过程而发生的固体物质的沉积。pvd工艺的主要概念是沉积的材料通过直接物质转移而物理转移到基板表面。通常,在工艺过程中不发生化学反应,且沉积层的厚度与化学反应动力学无关,这与cvd工艺相反。

4.溅射是一种已知的用于在基板上沉积化合物的物理气相沉积技术,其中原子、离子或分子通过粒子轰击从靶材(也称为溅射靶材)中喷射出来,使得喷射出的原子或分子在基板表面上积聚为薄膜。

5.另一种已知的物理气相沉积技术是阴极气相电弧(cathodic vapor arc)(cva)沉积方法。在这种方法中,电弧用于从阴极靶材蒸发材料。因此,所得到的汽化材料在基底上凝结形成涂层薄膜。

6.非晶碳是不具有结晶形式的碳的一种游离的、活性的形式。存在各种形式的非晶碳膜,它们通常按膜的氢含量和膜中的碳原子的sp2:sp3比进行分类。

7.在本领域的文献实例中,非晶碳膜分为7类(参见下表,摘自fraunhofer institut schich-und的“碳涂层名称索引(name index of carbon coatings)”):

[0008][0009]

四面体型不含氢非晶碳(ta-c)的特征在于,它含有很少氢或不含氢(小于5%mol,通常小于2%mol)和高含量的sp3杂化碳原子(通常大于80%的碳原子处于sp3状态)。

[0010]

尽管术语“类金刚石碳”(dlc)有时用于指代所有形式的非晶碳材料,但本文所用的该术语指的是除ta-c之外的非晶碳材料。dlc制造的常用方法使用碳氢化合物(如乙炔),因此将氢引入薄膜中(与原料通常为无氢高纯度石墨的ta-c薄膜形成对比)。

[0011]

换言之,dlc通常具有大于50%的sp2碳含量和/或20%mol及以上的氢含量。dlc可以未掺杂有金属或非金属或掺杂有金属或非金属(见上表)。

[0012]

近年来,电气元件的制造日趋自动化,以降低人力成本并降低洁净室内人员的存在和人工操作造成的污染风险。特别是,半导体制造业已经发生日趋自动化的趋势。

[0013]

自动化机器人设备现在实现了生产半导体成品晶圆所需的许多工艺步骤。这意味着现在有更多的“拾取和放置”操作,将晶圆从前开式晶圆传送盒(foup)移动到处理系统或分析工具中。由于静电充电和随后的放电(esd)或颗粒的静电吸引,整个制造过程中重复的机械操作和移动的规模是半导体生产中潜在的器件损坏的一个重要因素。

[0014]

半导体芯片和晶圆产品容易受到静电的影响,尤其是在处理和运输期间。静电放电会以一种退化的方式改变半导体器件的电气特性,甚至破坏它。静电荷的积累和随后的静电放电是半导体行业的主要故障原因。

[0015]

目前,市场上的静电消散方法大多是基于“湿法”工艺,在集成电路和晶圆产品上喷涂防静电涂层。然而,众所周知,这些产品具有低表面耐磨性,缩短了这些产品的使用寿命。

[0016]

当前的静电消散方法涉及对制造的产品自身进行涂层。这会影响所得产品的特性,从而降低这些产品的质量和/或使用寿命。

[0017]

因此,存在对这样的涂层的需求:能够减少静电充电和放电,但所制造的产品不具有上述低表面耐磨性问题或其他缺点。

技术实现要素:

[0018]

本发明的一个目的是提供这样的涂层,可加以采用而解决本领域中存在的一个或多个问题,并且优选地在减少静电荷积聚并因此减少静电放电(esd)方面提供改进。

[0019]

本技术的发明人已经发现,具有一层或多层ta-c和一层或多层dlc的碳涂层具有合适的静电消散性能,能够减少静电积聚和随后的静电放电。

[0020]

因此,本发明提供具有呈多层形式的涂层的基底,依次包括:

[0021]

i.基底,

[0022]

ii.种子层,

[0023]

iii.含ta-c层,和

[0024]

iv.含dlc层,

[0025]

其中涂层具有105ω/sq至109ω/sq的表面电阻。

[0026]

类似地提供了用于基底的涂层,依次包括:

[0027]

i.种子层,

[0028]

ii.含ta-c层,和

[0029]

iii.含dlc层,

[0030]

其中涂层具有105ω/sq至109ω/sq的表面电阻。

[0031]

适当地,如实施例中所说明的,本发明提供了一种经涂覆的基底,依次包括:

[0032]

i.金属基底,

[0033]

ii.导电金属种子层(例如钛或铬),

[0034]

iii.含ta-c层,和

[0035]

iv.含dlc层,

[0036]

其中涂层具有105ω/sq至109ω/sq的表面电阻。

[0037]

本发明还提供了一种经涂覆的基底,依次包括:

[0038]

i.包含硅或玻璃的基底,

[0039]

ii.包含硅的种子层,

[0040]

iii.含ta-c层,和

[0041]

iv.含dlc层,

[0042]

其中涂层具有105ω/sq至109ω/sq的表面电阻。

[0043]

还提供了一种制备涂层基底的方法,包括提供基底,以及按以下顺序在基底上进行涂敷:

[0044]

i.种子层,

[0045]

ii.含ta-c层,和

[0046]

iii.含dlc层

[0047]

其中涂层具有105ω/sq至109ω/sq的表面电阻。

[0048]

可以通过改变涂层内含dlc层的厚度来改变表面电阻。也可以通过改变cvd源设计、涂敷温度、气流、偏置电压和占空比(duty cycle)中的一项或多项来改变表面电阻。因此,本发明提供了具有可调表面电阻(tuneable surface resistance)的静电消散涂层。这些涂层减少了静电积聚和随后的静电放电,如以下更详细描述的本发明实施例的测试所示。

[0049]

如上所述,本文所用的术语“四面体非晶碳”(ta-c或tac)是指具有低氢含量和低sp2碳含量的非晶碳。

[0050]

ta-c是一种密度大的非晶材料,描述为由无序sp3组成,通过强键相互连接,类似于无序金刚石中存在的那些(参见neuville s,“四面体非晶碳涂层的新应用前瞻”,qscience connect 2014:8,http://dx.doi.org/10.5339/connect.2014.8)。由于其与金刚石的结构相似性,ta-c也是一种非常坚硬的材料,硬度值通常大于30gpa。

[0051]

例如,ta-c的氢含量可小于10%,通常为5%或更少,优选为2%或更少(例如1%或更少)。这里提供的氢的百分比含量是指摩尔百分比(而不是氢的质量百分比)。ta-c的sp2碳含量可小于30%,通常为20%或更少,优选15%或更少。优选地,ta-c可以具有2%或更少的氢含量和15%或更少的sp2碳含量。ta-c优选不掺杂其他材料(无论金属还是非金属)。

[0052]

相比之下,本文所用的术语“类金刚石碳”(dlc)是指除ta-c之外的非晶碳。因此,dlc比ta-c具有更高的氢含量和更高的sp2碳含量。例如,dlc可以具有20%或更大的氢含量,通常为25%或更大,例如30%或更大。这里提供的氢的百分比含量还是指摩尔百分比(而不是氢的质量百分比)。dlc可以具有50%或更高的sp2碳含量,通常为60%或更高。通常,dlc可以具有大于20%的氢含量和大于50%的sp2碳含量。dlc可以未掺杂金属和/或非金属或掺杂有金属和/或非金属。

[0053]

本发明有利地提供了静电消散涂层,其导致减少静电荷的积累并因此减少静电放

电。

[0054]

因此,本发明提供具有呈多层形式的涂层的基底,依次包括:

[0055]

i.基底,

[0056]

ii.种子层,

[0057]

iii.含ta-c层,和

[0058]

iv.含dlc层,

[0059]

其中涂层具有105ω/sq至109ω/sq的表面电阻。

[0060]

含dlc层

[0061]

含dlc层允许本发明的涂层导电。这是通过防止静电积聚和随后的静电放电使涂层用作静电消散涂层所需要的。

[0062]

涂层的最上层(即暴露在环境的层)是含dlc的层。在优选实施例中,含dlc层与含ta-c层相邻。该层可以包含按重量计大于70%,例如大于80%,优选大于90%的dlc,或者该层可以由dlc构成。在优选实施例中,含dlc层由dlc构成。

[0063]

dlc可具有20%或更大的氢含量,通常为25%或更大,例如30%或更大。这里提供的氢的百分比含量还是指摩尔百分比(而不是氢的质量百分比)。

[0064]

dlc可具有60%或更大、通常70%或更大、优选80%或更大或90%或更大的sp2碳含量。

[0065]

dlc可具有40%或更少、通常30%或更少、优选20%或更少或10%或更少的sp3碳含量。

[0066]

通常,dlc可以具有大于20%的氢含量和大于50%的sp2碳含量。

[0067]

在特别优选的实施例中,含dlc层由dlc构成,其中dlc具有大于20%的氢含量和大于50%的sp2碳含量。

[0068]

dlc可以未掺杂金属和/或非金属或掺杂有金属和/或非金属。

[0069]

dlc通常通过cvd方法(优选pacvd)沉积,如下文进一步详细描述的。含dlc层通常通过fcva以外的方法沉积。

[0070]

含dlc层的厚度通常为0.5μm或以上,例如1.0μm或以上,优选1.5μm或以上。dlc涂层通常还具有4.5μm或更小的厚度,例如4.0μm或更小,优选3.5μm或更小。因此,dlc涂层可具有0.5μm至4.5μm的厚度,例如1.0μm至4.0μm,优选1.5μm至3.5μm。

[0071]

含ta-c层

[0072]

含ta-c层增加了本发明的涂覆基底的硬度从而耐磨性。这又增加了本发明涂覆基底的寿命。含ta-c层还增加了dlc层相对于种子层的粘附性,减少了分层并因此增加了本发明涂覆基底的寿命。

[0073]

通常,含ta-c层与含dlc层相邻。通常,含ta-c层与种子层相邻。在优选实施例中,含ta-c层与含dlc层和种子层相邻。

[0074]

含ta-c层可以包含按重量计大于70%,例如大于80%,优选大于90%的ta-c,或者该层可以由ta-c构成。在优选实施例中,含ta-c层由ta-c构成。

[0075]

ta-c的氢含量通常为5%或以下,优选为2%或以下,最优选为1%或以下。

[0076]

ta-c通常具有20%或更少,优选15%或更少的sp2碳含量。

[0077]

ta-c通常具有80%或更高、优选85%或更高的sp3碳含量。

[0078]

通常,ta-c可具有5%或更少的氢含量和20%或更少的sp2碳含量,优选地,ta-c可具有2%或更少的氢含量和15%或更少的sp2含量。

[0079]

在特别优选的实施例中,含ta-c层由ta-c构成,其中ta-c具有5%或更少的氢含量和20%或更少的sp2碳含量。

[0080]

含ta-c层的厚度通常为0.01μm或以上,例如0.05μm或以上,优选0.1μm或以上。含ta-c层的厚度通常也为2.0μm或更小,例如1.5μm或更小,优选1.0μm或更小。因此,含ta-c层的厚度可为0.01μm至2.0μm,例如0.05μm至1.5μm,优选0.1μm至1.0μm。

[0081]

ta-c优选通过pvd方法沉积,例如cva方法(优选fcva)。

[0082]

种子层

[0083]

种子层被纳入以提高含ta-c层与下面的基底的粘附性。种子层增加了基底和含ta-c层之间的粘附力。这降低了涂层从基底上分层的可能性。

[0084]

通常,种子层与含ta-c层相邻。通常,种子层与基底相邻。在优选实施例中,种子层与含ta-c层和基底相邻。

[0085]

种子层通常也是导电的以提供导电表面,含碳的ta-c和dlc层可以沉积在该导电表面上。

[0086]

因此,种子层的性质将取决于基底的性质。种子层的厚度通常为0.05μm或以上,例如0.1μm或以上,优选0.3μm或以上。种子层的厚度通常也为2μm或以下,例如1μm或以下,优选0.8μm或以下。因此,种子层的厚度可以为0.05μm至2μm,例如0.1μm至1μm,优选0.3μm至0.8μm。

[0087]

通常,种子层是导电金属。通常,当基底是金属时,种子层是导电金属。当基底是金属时,种子层优选包含ti或cr。在最优选的实施例中,当基底是金属时,种子层是ti。当基底是硅或玻璃时,种子层通常包含硅。

[0088]

种子层通常通过pvd方法沉积并且优选地种子层通过溅射沉积。

[0089]

基底

[0090]

基底材料的选择范围很广,可以涂覆由多种材料制成的许多基底。基底通常是金属的并且通常是或包含金属、合金、硅或玻璃。

[0091]

在一个实施例中,合适的基底包括各种钢(例如钢、不锈钢、hss、工具钢和合金钢)、铜或其合金和铝或其合金。制品通常由基底制成,于是施加/沉积本发明的涂层。

[0092]

在另一个实施例中,合适的基底包括硅和玻璃。

[0093]

基底可以是静电放电可能造成问题的任何装置,例如与半导体接触的装置。

[0094]

应指出,涂层可施用于设备而不是制造装置内的产品。因此,无需将抗静电涂层应用于制造品。这有利地防止了与涂覆产品自身相关的任何缺点。特别是,这些产品的质量和/或寿命不会降低。事实上,设备上的涂层有助于延长所制造产品的使用寿命。

[0095]

整体涂层基底

[0096]

涂层(包括种子层、含dlc层和含ta-c层)的总厚度通常为0.7μm或更大,合适地为1.0μm或更大,例如2.0μm或更大,优选3.0μm或更大。涂层的总厚度通常也为9.0μm或更小,适当地为7.0μm或更小,例如5.0μm或更小,优选4.0μm或更小。因此,涂层的总厚度可以为0.7μm至9.0μm,合适地为1.0μm至7.0μm,例如2.0μm至5.0μm,优选3.0μm至4.0μm。

[0097]

涂敷基底具有可调节的电阻,取决于含dlc层的厚度。施加含dlc层的温度和速度

也会影响涂覆基底的表面电阻。通常,涂层的表面电阻为104ω/sq至10

12

ω/sq,合适地为105ω/sq至10

10

ω/sq,优选为105ω/sq至109ω/sq,以及最优选为106ω/sq至107ω/sq。

[0098]

涂层通常具有500hv或更高的硬度,优选1000hv或更高,最优选1500hv或更高。涂层通常还具有3500hv或更低的硬度,优选3000hv或更低,最优选2000hv或更低。因此,涂层可具有500hv至3500hv、优选1000hv至3000hv、最优选1500hv至2000hv的硬度。

[0099]

硬度可采用维氏硬度测试(vickers hardness test)(由vickers ltd的robert l.smith和george e.sandland于1921年研制;标准测试另见astm e384-17)进行测量,其可用于所有金属并在各种硬度测试当中应用范围最广。测试给出的硬度单位称为维氏角锥硬度值(vickers pyramid number)(hv),可以转换为帕斯卡单位(gpa)。硬度值由测试中使用的压痕表面积上的载荷确定。作为例子,作为一种硬刚的马氏体其hv约为1000,而金刚石的hv约为10,000hv(约98gpa)。金刚石的硬度随具体的晶体结构和取向而变化,但常见的硬度在约90到超过100gpa之间。

[0100]

通常,含ta-c层和含dlc层是相邻的,即在含ta-c层和含dlc层之间不存在其他层。此外,种子层和含ta-c层优选地彼此相邻,即在种子层和含ta-c层之间不存在其他层。基底和种子层优选地也是相邻的,即在基底和种子层之间不存在其他层。

[0101]

在优选实施例中,种子层和含ta-c层是相邻的,并且含ta-c层和含dlc层是相邻的。在其他实施例中,基底和种子层是相邻的,并且含ta-c层和含dlc层是相邻的。在其他实施例中,基底和种子层是相邻的并且种子层和含ta-c层是相邻的。在特别优选的实施例中,基底和种子层相邻,以及种子层和含ta-c层相邻,并且含ta-c层和含dlc层相邻。

[0102]

在本发明的一个实施方案中,提供了一种涂覆基底,依次包括:

[0103]

i.基底,

[0104]

ii.种子层,

[0105]

iii.含ta-c的层,和

[0106]

iv.含dlc层.

[0107]

其中涂层具有105ω/sq至109ω/sq的表面电阻。

[0108]

基底、种子层、含ta-c层和含dlc层可具有上述特性。

[0109]

在进一步的实施方案中,本发明提供了一种涂覆基底,依次包括:

[0110]

i.金属基底,

[0111]

ii.导电金属种子层(例如钛或铬),

[0112]

iii.含ta-c的层,和

[0113]

iv.含dlc层。

[0114]

在另一个实施方案中,本发明提供了一种涂覆基底,其依次包括:

[0115]

i.包含硅或玻璃的基板,

[0116]

ii.包含硅的种子层,

[0117]

iii.含ta-c的层,和

[0118]

iv.含dlc层。

[0119]

方法

[0120]

本发明还提供了一种制备根据上述公开内容的涂覆基底的方法,包括提供基底,并依次在基底上涂覆下述各层:

[0121]

i.种子层,

[0122]

ii.含ta-c层,和

[0123]

iii.含dlc层

[0124]

其中涂层具有105ω/sq至109ω/sq(例如106ω/sq至107ω/sq)的表面电阻。

[0125]

传统的cvd和pvd方法,特别是cva和fcva工艺,是已知的并用于广泛的基底,并且本发明的方法同样适用于涂覆广泛的基底。固体,无论是导电的还是不导电的,通常都是合适的,种子层和粘附层可以用来提高涂层粘附性和强度,并使表面易于涂覆。可以涂覆由金属、合金、陶瓷及其混合物制成的基底。通常,基底容易积聚静电荷并因此容易产生静电放电。

[0126]

本文所述的涂覆工艺可以全部在低温下进行,例如在100℃或更低的温度下,例如在70℃的温度下。另外,本文所述的涂覆工艺可在80℃至220℃、可选地在100℃至200℃、通常在100℃至150℃、优选地在110℃至130℃、更优选地在115℃至125℃(例如120℃)的温度下进行。这是一个优点,因为涂覆基底的方法因此可以在相对低的温度下进行,以避免与涂覆工艺相关的能源成本。

[0127]

本发明的涂层可以是多层的,并且各个层可以使用一系列已知的和常规的沉积技术独立地进行沉积,包括cvd、pvd、磁控溅射和多弧离子镀。溅射是一种合适的方法,特别是对于种子层。pvd适用于含ta-c层,例如cva。cva工艺通常是过滤阴极真空电弧(fcva)工艺,例如如下所述。fcva涂层的设备和方法是已知的并且可以用作本发明方法的一部分。fcva涂覆设备通常包括真空室、阳极、阴极组件,用于从靶产生等离子体,和用于将基底偏置于给定电压的电源。fcva的特性是常规的而不是本发明的一部分。

[0128]

cvd工艺可以利用离子源(包括端部霍尔离子源(end-hall ion sources)、考夫曼离子源(kaufman ion sources)、阳极层源、热丝离子源和空心阴极离子源)来沉积材料。cvd工艺可以优选地为等离子体活化cvd工艺(plasma activated cvd process)(pacvd,也称为等离子体增强cvd,pecvd)。与传统的(即热活化)cvd工艺相比,pacvd工艺具有较低的沉积温度、更高的纯度和更容易控制反应参数。与传统的cvd工艺相比,pacvd工艺还具有更高的涂层能量,从而导致更好的涂层附着性以及更高的涂层硬度和密度。与传统的cvd工艺相比,pacvd工艺还可导致更好的涂层覆盖率和均匀性。另外,涂层材料可以作为气体提供,然后使用电源(例如直流电源、脉冲直流电源或射频电源)对其进行充电/电离。

[0129]

在优选实施例中,种子层通过溅射沉积。在其他优选实施例中,含ta-c层通过fcva沉积。在进一步优选的实施例中,含dlc层通过cvd,最优选pacvd,进行沉积。

[0130]

涂层的表面电阻(也称为表面电阻或薄层电阻)通过在施加含dlc层期间控制含dlc层的厚度、控制该层的施加速度和温度以及控制气流、偏置电压和占空比来进行确定。因此,本文所公开的方法可包括改变dlc层的厚度以获得具有所需电阻的涂敷基板。该方法还可以包括独立地改变施加含dlc层的温度、气流、偏置电压和占空比中的一项或多项,以获得具有所需电阻的涂覆基底。

[0131]

增加含dlc层的厚度会降低涂层的电导率,并因此会增加涂层的表面电阻。不希望受理论束缚,这是因为增加含dlc层的厚度会增加导电层的厚度,并且表面电阻与厚度成反比。

[0132]

该方法还可以包括独立地改变dlc和/或ta-c施加的速度和/或温度以获得具有所

需电阻的涂敷基底。上面论述了沉积含dlc层的合适温度范围,因为相同(或相似)的温度可用于整个涂覆工艺。

[0133]

在含dlc层的cvd沉积过程中,受控的气流通过沉积室。气流可为50sccm至200sccm,通常为75sccm至150sccm,优选为80sccm至120sccm,最优选为90sccm至110sccm。使用的气体可以选自ch4、c2h6或c2h2,优选的气体是c2h2。在如本文所述的含dlc层的cvd沉积的优选实施例中,气体是c2h2并且气流是从90sccm到110sccm(例如100sccm)。

[0134]

本文所述的含dlc层的沉积可以在-50v至-1200v、可选地在-200v至-1200v、通常在-500v至-1200v、优选在-800v至-1200v、最优选在-1000v到-1200v的负偏压下进行。3.2%至100%的占空比可用于沉积含dlc层。可选地,占空比为3.2%至75%,通常为3.2%至50%,优选3.2%至20%,以及最优选3.2%至10%。在本文所述的含dlc层的cvd沉积的优选实施例中,偏压为-1000v至-1200v(例如-1200v)并且占空比为3.2%至10%(例如3.2%)。

附图说明

[0135]

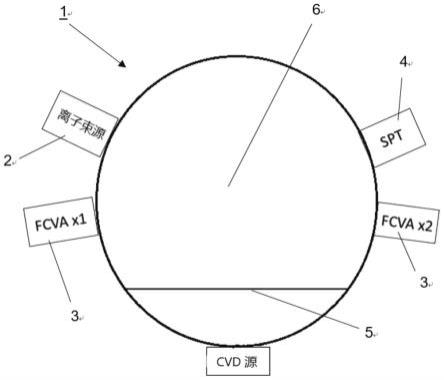

图1显示了用于生产本发明的涂敷基底的涂敷设备。

具体实施方式

[0136]

示例1-涂层方法(1)

[0137]

如图1所示,使用具有围绕中央涂敷室设置的ti溅射源、两个fcva源、cvd源和离子束源的涂敷设备生产涂敷基底。

[0138]

涂敷设备1具有中央涂敷室6。在涂敷室周围有离子束源2、两个fcva源3和溅射源4。在使用中,基底(未示出)安装在涂敷夹具(未示出)上,然后将涂敷夹具装入涂敷室并居中定位在平台5上。然后可以密封涂敷室6并在基底被涂层之前将其抽至所需的真空度。

[0139]

通过按顺序执行以下步骤来涂覆基底:

[0140]

1.将预先清洁的钢基底安装到涂敷夹具(也称为基底支架)上。

[0141]

2.将安装有基底的涂敷夹具装入涂敷室,并将其抽至所需的真空度(见下文,了解每个步骤所需的压力)。加热器温度设置为100℃,并在整个涂敷过程中予以保持。

[0142]

3.使用离子束源蚀刻基底。

[0143]

4.通过用ti靶溅射施加ti层,直到达到所需的厚度。在溅射过程中,腔室压力约为2.0x10-3

torr。在溅射步骤期间,基底支架以50%占空比偏置在-300v。

[0144]

5.使用石墨源通过fcva施加ta-c层,直到达到所需的厚度。在fcva期间,fcva涂敷压力低于2.0x10-5

torr。在fcva步骤期间,基板支架以3.2%占空比偏置在-1200v。

[0145]

6.使用c2h

2 cvd源通过cvd施加dlc层,直到达到所需的厚度。cvd压力约为2.0x10-3

torr。在cvd步骤期间,衬底支架以3.2%占空比偏置在-1200v。

[0146]

7.解除真空,并将安装的涂敷基底从涂敷室中取出。

[0147]

8.从涂敷夹具中取出涂敷基底。

[0148]

所得到的涂敷基底具有以下特性:

[0149][0150]

dlc层的杨氏模量为90gpa,密度为2.410kg/m3。针对涂敷基底进行一些进一步的测试,下面提供了详细信息。

[0151]

示例2-测试表面电阻

[0152]

使用prs-801电阻系统测量表面电阻,测得的表面电阻为5.7x107ω/sq。

[0153]

示例3-测试硬度

[0154]

实施例1中描述的本发明涂层的硬度使用具有500mn最大载荷的nmt3纳米压痕测试仪进行测定。然而,只有4mn用于测量硬度。使用16mn/min的加载/卸载速率和30秒的暂停。根据显示力与压痕的加载/卸载曲线,涂层的维氏硬度值(hv)被确定为3000hv。

[0155]

示例4-测试耐磨性

[0156]

使用bruker tribolab系统进行摩擦测试(tribo test),以确定涂层在重复的强力振荡运动下的耐磨性。摩擦测试是一种往复“销盘(pin-on-disk)”式滑动测试,并模拟使用过程中可能发生的振荡磨损。涂层通过了400n下1500次循环测试。该涂层还通过了750g负载和cs-17尖端(cs-17tip)下10000次循环测试。

[0157]

示例5-涂敷方法(2)

[0158]

如图1所示,使用具有围绕中央涂敷室设置的ti溅射源、两个fcva源、cvd源和离子束源的涂敷设备生产涂敷基底。cvd源是pacvd源。

[0159]

通过按顺序执行以下步骤来涂覆基底:

[0160]

1.将预先清洁的钢基底安装到涂覆夹具(也称为基底支架)上。

[0161]

2.将安装有基板的涂覆夹具装入涂覆室,并将其抽至所需的真空度(见下文,了解每个步骤所需的压力)。加热器温度设置为120℃,并在整个涂覆过程中予以保持。

[0162]

3.使用离子束源蚀刻基板。

[0163]

4.通过用ti靶溅射施加ti层,直到达到所需的厚度。在溅射过程中,腔室压力约为2.0x10-3

torr。在溅射步骤期间,基底支架以50%占空比偏置在-300v。

[0164]

5.使用石墨源通过fcva施加ta-c层,直到达到所需的厚度。在fcva期间,fcva涂敷压力低于2.0x10-5

torr。在fcva步骤期间,基板支架以3.2%的占空比偏置在-1200v。

[0165]

6.利用c2h

2 pacvd源通过pacvd施加dlc层,直到达到所需的厚度。pacvd压力约为2.0x10-3

torr。在pacvd步骤期间,衬底支架以3.2%占空比偏置在-1200v。在pacvd步骤期间,c2h2气流在100sccm下进入涂敷室。

[0166]

7.解除真空,并将安装的涂敷基底从涂敷室中取出。

[0167]

8.从涂敷夹具中取出涂敷基底。

[0168]

涂敷基底被确定为具有107ω/sq的表面电阻。该涂层还具有理想的膜硬度、密度和均匀性。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1