电子器件的制造方法和电子器件与流程

电子器件的制造方法和电子器件

1.本技术是分案申请,其原申请的中国国家申请号为202010077646.5,申请日为2020年01月31日,发明名称为“蒸镀掩模组、电子器件的制造方法和电子器件”。

技术领域

2.本技术的实施方式涉及电子器件的制造方法和电子器件。

背景技术:

3.智能手机、平板电脑等便携式设备中使用的显示装置优选为高精细,例如优选像素密度为400ppi以上。另外,对于便携式设备,应对超高分辨率的需要也正在提高。在超高分辨率的情况下,显示装置的像素密度例如优选为800ppi以上。

4.显示装置之中,有机el显示装置由于响应性好、耗电低、对比度高而受到关注。作为形成有机el显示装置的像素的方法,已知有下述方法:使用形成有贯通孔的蒸镀掩模,形成像素或电极。例如,首先,准备以与像素对应的图案形成有阳极的基板。接着,藉由蒸镀掩模的贯通孔使有机材料附着于阳极上,在阳极上形成有机层。接着,藉由蒸镀掩模的贯通孔使导电性材料附着于有机层上,在有机层上形成阴极。

5.现有技术文献

6.专利文献

7.专利文献1:日本特开2000-82582号公报

技术实现要素:

8.发明所要解决的课题

9.有机el显示装置等电子器件的阴极不仅形成于在沿着基板的法线方向观察时与阳极和有机层重叠的部分,有时还形成于不与阳极和有机层重叠的部分。阴极的面积越大,则阴极的电阻越低,电气特性越高。另一方面,阴极的面积越大,则包含基板、阳极、有机层和阴极的电子器件中的透光率越低。

10.本技术的实施方式的目的在于提供一种能够有效解决这种课题的蒸镀掩模组。

11.用于解决课题的手段

12.本技术的一个实施方式的蒸镀掩模组具备:第1蒸镀掩模,其具有沿不同的两个方向排列的两个以上的第1贯通孔;第2蒸镀掩模,其具有沿不同的两个方向排列的两个以上的第2贯通孔;和第3蒸镀掩模,其具有两个以上的第3贯通孔。在将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重合时,第1贯通孔与第2贯通孔或第3贯通孔部分重叠。

13.发明效果

14.在本技术的至少一个实施方式中,能够调整形成于基板的电极的电阻和面积。

附图说明

15.图1是示出使用本技术的一个实施方式的蒸镀掩模组制作的电子器件的一例的截

面图。

16.图2是将图1的电子器件的元件放大示出的截面图。

17.图3是示出形成有第1电极的状态的基板的一例的俯视图。

18.图4是示出形成有第1电极和通电层的状态的基板的一例的俯视图。

19.图5是示出形成有第1电极、通电层和第2电极的第1层的状态的基板的一例的俯视图。

20.图6是示出形成有第1电极、通电层、第2电极的第1层和第2电极的第2层的状态的基板的一例的俯视图。

21.图7是示出具备蒸镀掩模装置的蒸镀装置的图。

22.图8是示出蒸镀掩模装置的俯视图。

23.图9是将具备第1蒸镀掩模的蒸镀掩模装置放大示出的俯视图。

24.图10是将具备第2蒸镀掩模的蒸镀掩模装置放大示出的俯视图。

25.图11是示出蒸镀掩模的截面结构的一例的图。

26.图12是示出第1蒸镀掩模的一例的俯视图。

27.图13是将图12的第1蒸镀掩模放大示出的俯视图。

28.图14是示出第2蒸镀掩模的一例的俯视图。

29.图15是将图14的第2蒸镀掩模放大示出的俯视图。

30.图16是示出将第1蒸镀掩模与第2蒸镀掩模重叠时的图。

31.图17是示出形成有第1通电层、第2通电层和第3通电层的状态的基板的一例的俯视图。

32.图18是示出在第1通电层、第2通电层和第3通电层上形成有第2电极的状态的基板的一例的俯视图。

33.图19是沿着图18的电子器件的xix-xix线的截面图。

34.图20是沿着图18的电子器件的xx-xx线的截面图。

35.图21是沿着图18的电子器件的xxi-xxi线的截面图。

36.图22是示出第1蒸镀掩模的一例的俯视图。

37.图23是示出第2蒸镀掩模的一例的俯视图。

38.图24是示出第3蒸镀掩模的一例的俯视图。

39.图25是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

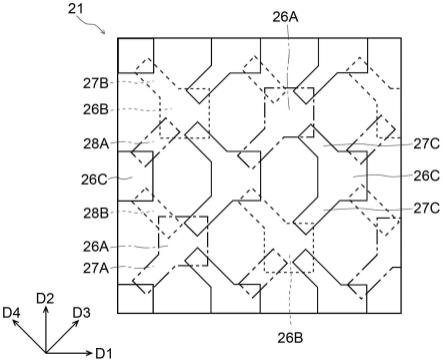

40.图26是示出第1蒸镀掩模的一例的俯视图。

41.图27是示出第2蒸镀掩模的一例的俯视图。

42.图28是示出第3蒸镀掩模的一例的俯视图。

43.图29是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

44.图30是示出具备第1通电层、第2通电层和第3通电层的电子器件的一例的俯视图。

45.图31是沿着图30的电子器件的xxxi-xxxi线的截面图。

46.图32是示出第1蒸镀掩模的一例的俯视图。

47.图33是示出第2蒸镀掩模的一例的俯视图。

48.图34是示出第3蒸镀掩模的一例的俯视图。

49.图35是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

50.图36是示出形成有第1通电层、第2通电层和第3通电层的状态的基板的一例的俯视图。

51.图37是示出在第1通电层、第2通电层和第3通电层上形成有第2电极的状态的基板的一例的俯视图。

52.图38是沿着图36的电子器件的xxxviii-xxxviii线的截面图。

53.图39是示出第1蒸镀掩模的一例的俯视图。

54.图40是示出第2蒸镀掩模的一例的俯视图。

55.图41是示出第3蒸镀掩模的一例的俯视图。

56.图42a是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

57.图42b是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

58.图43是示出在第1通电层、第2通电层和第3通电层上形成有第2电极的状态的基板的一例的俯视图。

59.图44是沿着图43的电子器件的xxxxiv-xxxxiv线的截面图。

60.图45是示出第1蒸镀掩模的一例的俯视图。

61.图46是示出第2蒸镀掩模的一例的俯视图。

62.图47是示出第3蒸镀掩模的一例的俯视图。

63.图48a是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

64.图48b是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

65.图49是示出在第1通电层、第2通电层和第3通电层上形成有第2电极的状态的基板的一例的俯视图。

66.图50是沿着图49的电子器件的xxxxx-xxxxx线的截面图。

67.图51是示出第1蒸镀掩模的一例的俯视图。

68.图52是示出第2蒸镀掩模的一例的俯视图。

69.图53是示出第3蒸镀掩模的一例的俯视图。

70.图54a是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

71.图54b是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

72.图55是示出形成有第1通电层、第2通电层和第3通电层的状态的基板的一例的俯视图。

73.图56是示出在第1通电层、第2通电层和第3通电层上形成有第2电极的状态的基板的一例的俯视图。

74.图57是示出第1蒸镀掩模的一例的俯视图。

75.图58是示出第2蒸镀掩模的一例的俯视图。

76.图59是示出第3蒸镀掩模的一例的俯视图。

77.图60是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

78.图61是示出形成有第1通电层、第2通电层和第3通电层的状态的基板的一例的俯视图。

79.图62是示出在第1通电层、第2通电层和第3通电层上形成有第2电极的状态的基板的一例的俯视图。

80.图63是示出第1蒸镀掩模的一例的俯视图。

81.图64是示出第2蒸镀掩模的一例的俯视图。

82.图65是示出第3蒸镀掩模的一例的俯视图。

83.图66是示出将第1蒸镀掩模、第2蒸镀掩模和第3蒸镀掩模重叠时的图。

84.图67是示出在第1通电层、第2通电层和第3通电层上形成有第2电极的状态的基板的一例的俯视图。

85.图68是示出第1蒸镀掩模的一例的俯视图。

86.图69是示出第2蒸镀掩模的一例的俯视图。

87.图70是示出将第1蒸镀掩模与第2蒸镀掩模重叠时的图。

88.图71是示出第1蒸镀掩模的一例的俯视图。

89.图72是示出电子器件的一例的俯视图。

90.图73是示出电子器件的一例的俯视图。

具体实施方式

91.本说明书和本附图中,只要没有特别说明,则“基板”、“基材”、“板”、“片”、“膜”等意味着作为某个构成的基础的物质的术语并不是仅基于称呼的差异来相互区分的。

92.本说明书和本附图中,只要没有特别说明,则关于指定形状或几何学的条件以及它们的程度的、例如“平行”、“正交”等术语和长度、角度的值等,不限于严格的含义,包括可期待同样功能的程度的范围来进行解释。

93.本说明书和本附图中,只要没有特别说明,则在某一部件或某一区域等的某一构成处于另一部件或另一区域等的另一构成之“上”或“下”、“上侧”或“下侧”、或者“上方”或“下方”的情况下,包括某一构成直接接触另一构成的情况。进而,还包括在某一构成与另一构成之间包含其他构成的情况、即间接接触的情况。另外,只要没有特别说明,则“上”、“上侧”、“上方”、或者“下”、“下侧”、“下方”这样的语句中,上下方向可以颠倒。

94.本说明书和本附图中,只要没有特别说明,对相同部分或具有同样功能的部分标注相同的符号或相似的符号,并有时省略其重复说明。另外,为了便于说明,有时附图的尺寸比例与实际的比例不同,或者有时从附图中省略一部分构成。

95.本说明书和本附图中,只要没有特别说明,本说明书的一个实施方式可以在不产生矛盾的范围内与其他实施方式组合。另外,其他实施方式彼此也可以在不产生矛盾的范围内进行组合。

96.本说明书和本附图中,只要没有特别说明,在关于制造方法等方法公开了多个工序的情况下,可以在所公开的工序之间实施未公开的其他工序。另外,所公开的工序的顺序在不产生矛盾的范围内是任意的。

97.本说明书和本附图中,只要没有特别说明,由符号“~”表述的数值范围包括置于符号“~”前后的数值。例如,由“34~38质量%”这样的表述划定的数值范围与由“34质量%以上且38质量%以下”这样的表述划定的数值范围相同。

98.本实施方式中,对具备两个以上的蒸镀掩模的蒸镀掩模组被用于在制造有机el显示装置时以所期望的图案在基板上形成电极的示例进行说明。其中,蒸镀掩模组的用途没有特别限定,可以将本实施方式应用于在各种用途中使用的蒸镀掩模组。例如,本实施方式的蒸镀掩模组可以用于形成用于表现虚拟现实(所谓的vr)或增强现实(所谓的ar)的图像、

用于显示或投影屏幕图像的装置的电极。另外,本实施方式的蒸镀掩模组也可以用于形成液晶显示装置的电极等有机el显示装置以外的显示装置的电极。另外,本实施方式的蒸镀掩模组也可以用于形成压力传感器的电极等显示装置以外的电子器件的电极。

99.以下,参照附图详细地对本公开的一个实施方式进行说明。需要说明的是,以下所示的实施方式为本公开的实施方式的一例,本公开并不仅限于这些实施方式来进行解释。

100.本技术的第1方式为一种蒸镀掩模组,其具备:

101.第1蒸镀掩模,其具有沿不同的两个方向排列的两个以上的第1贯通孔,

102.第2蒸镀掩模,其具有沿不同的两个方向排列的两个以上的第2贯通孔;和

103.第3蒸镀掩模,其具有两个以上的第3贯通孔,

104.在将上述第1蒸镀掩模、上述第2蒸镀掩模和上述第3蒸镀掩模重合时,上述第1贯通孔与上述第2贯通孔或上述第3贯通孔部分重叠。

105.本技术的第2方式为,在上述的第1方式的蒸镀掩模组中,

106.两个以上的上述第1贯通孔可以包含:两个以上的掩模第1基本区域,它们沿不同的两个方向排列;和两个以上的掩模第1扩张区域,它们从上述掩模第1基本区域延伸出以便在将上述第1蒸镀掩模、上述第2蒸镀掩模和上述第3蒸镀掩模重合时与上述第2贯通孔或上述第3贯通孔部分重叠。

107.本技术的第3方式为,在上述的第2方式的蒸镀掩模组中,

108.两个以上的上述第2贯通孔可以包含沿不同的两个方向排列的两个以上的掩模第2基本区域、和从上述掩模第2基本区域延伸出的两个以上的掩模第2扩张区域,或者,两个以上的上述第3贯通孔包含沿不同的两个方向排列的两个以上的掩模第3基本区域、和从上述掩模第3基本区域延伸出的两个以上的掩模第3扩张区域,

109.在将上述第1蒸镀掩模、上述第2蒸镀掩模和上述第3蒸镀掩模重合时,两个以上的上述掩模第1扩张区域的至少一部分与上述掩模第2扩张区域或上述掩模第3扩张区域整体或部分重叠。

110.本技术的第4的方式为,在上述的第3方式的蒸镀掩模组中,

111.上述掩模第2扩张区域或上述掩模第3扩张区域中的与上述掩模第1扩张区域重叠的区域可以与上述掩模第1基本区域部分重叠。

112.本技术的第5方式为,在上述的第2方式至上述的第4方式各自的蒸镀掩模组中,

113.在与上述掩模第1扩张区域的延伸方向正交的方向上,上述掩模第1扩张区域的尺寸可以为上述掩模第1基本区域的尺寸的0.9倍以下。

114.本技术的第6方式为,在上述的第2方式至上述的第5方式各自的蒸镀掩模组中,

115.上述掩模第1基本区域的排列方向与上述掩模第1扩张区域从上述掩模第1基本区域延伸出的方向可以一致。

116.本技术的第7方式为,在上述的第2方式至上述的第5方式各自的蒸镀掩模组中,

117.上述掩模第1基本区域的排列方向与上述掩模第1扩张区域从上述掩模第1基本区域延伸出的方向可以不同。

118.本技术的第8方式为,在上述的第1方式的蒸镀掩模组中,

119.两个以上的上述第1贯通孔可以包含沿不同的两个方向排列的两个以上的掩模第1基本区域、和两个以上的掩模第1辅助区域,

120.在将上述第1蒸镀掩模、上述第2蒸镀掩模和上述第3蒸镀掩模重合时,上述掩模第1辅助区域可以按照与相邻的两个上述第2贯通孔、相邻的两个上述第3贯通孔、或者相邻的上述第2贯通孔和上述第3贯通孔部分重叠的方式延伸。

121.本技术的第9方式为,在上述的第8方式的蒸镀掩模组中,

122.在与上述掩模第1辅助区域的延伸方向正交的方向上,上述掩模第1辅助区域的尺寸可以为上述掩模第1基本区域的尺寸的0.9倍以下。

123.本技术的第10方式为,在上述的第9方式的蒸镀掩模组中,

124.上述掩模第1辅助区域可以与上述掩模第1基本区域连接。

125.本技术的第11方式为,在上述的第9方式的蒸镀掩模组中,

126.上述掩模第1辅助区域可以不与上述掩模第1基本区域连接。

127.本技术的第12方式为,在上述的第1方式至上述的第11方式各自的蒸镀掩模组中,

128.在将上述第1蒸镀掩模、上述第2蒸镀掩模和上述第3蒸镀掩模重合时,两个以上的上述第1贯通孔中的至少一部分上述第1贯通孔可以藉由上述第2贯通孔和上述第3贯通孔与其他上述第1贯通孔连接。

129.本技术的第13方式为,在上述的第1方式至上述的第11方式各自的蒸镀掩模组中,

130.在将上述第1蒸镀掩模、上述第2蒸镀掩模和上述第3蒸镀掩模重合时,两个以上的上述第1贯通孔中的至少一部分上述第1贯通孔可以藉由上述第2贯通孔或上述第3贯通孔与其他上述第1贯通孔连接。

131.本技术的第14方式为一种蒸镀掩模组,其具备:

132.第1蒸镀掩模,其具有沿第1方向排列的两个以上的第1贯通孔;和

133.第2蒸镀掩模,其具有两个以上的第2贯通孔,

134.上述第1贯通孔包含:两个以上的掩模第1基本区域,它们沿与上述第1方向交叉的第2方向排列;和掩模第1扩张区域,它们按照连接上述第2方向上相邻的两个上述掩模第1基本区域的方式延伸、并在与上述第2方向正交的方向上具有小于上述掩模第1基本区域的尺寸,

135.在将上述第1蒸镀掩模与上述第2蒸镀掩模重合时,上述第1贯通孔与上述第2贯通孔部分重叠。

136.本技术的第15方式为,在上述的第14方式的蒸镀掩模组中,

137.在将上述第1蒸镀掩模与上述第2蒸镀掩模重合时,两个以上的上述掩模第1基本区域中的至少一部分上述掩模第1基本区域可以藉由上述第2贯通孔与其他上述掩模第1基本区域连接。

138.本技术的第16方式为,在上述的第14方式或上述的第15方式各自的蒸镀掩模组中,

139.在将上述第1蒸镀掩模与上述第2蒸镀掩模重合时,上述掩模第1扩张区域与上述第2贯通孔可以整体或部分重叠。

140.本技术的第17方式为,在上述的第16方式的蒸镀掩模组中,

141.在将上述第1蒸镀掩模与上述第2蒸镀掩模重合时,上述第2贯通孔可以与上述第2方向上相邻的两个上述掩模第1基本区域以及与上述两个上述掩模第1基本区域连接的上述掩模第1扩张区域整体或部分重叠。

142.本技术的第18方式为,在上述的第14方式至上述的第17方式各自的蒸镀掩模组中,

143.在与上述第2方向正交的方向上,上述掩模第1扩张区域的尺寸可以为上述掩模第1基本区域的尺寸的0.9倍以下。

144.本技术的第19方式为一种蒸镀掩模组,其具备:

145.第1蒸镀掩模,其具有两个以上的第1贯通孔;和

146.第2蒸镀掩模,其具有两个以上的第2贯通孔,

147.两个以上的上述第1贯通孔包含:两个以上的掩模第1基本区域,它们沿第1方向排列、并且沿与上述第1方向交叉的第2方向排列;和两个以上的掩模第1辅助区域,它们位于上述第2方向上相邻的两个上述掩模第1基本区域之间,并在上述第2方向上具有小于上述掩模第1基本区域的尺寸,

148.两个以上的上述第2贯通孔沿上述第1方向和上述第2方向排列,

149.在将上述第1蒸镀掩模与上述第2蒸镀掩模重合时,上述掩模第1辅助区域按照与上述第1方向上相邻的两个上述第2贯通孔部分重叠的方式延伸。

150.本技术的第20方式为,在上述的第19方式的蒸镀掩模组中,

151.在将上述第1蒸镀掩模与上述第2蒸镀掩模重合时,上述第2贯通孔可以按照与上述第2方向上相邻的两个上述掩模第1基本区域部分重叠的方式延伸。

152.本技术的第21方式为,在上述的第19方式或上述的第20方式各自的蒸镀掩模组中,

153.在上述第2方向上,上述掩模第1辅助区域的尺寸可以为上述掩模第1基本区域的尺寸的0.9倍以下。

154.本技术的第22方式为一种电子器件的制造方法,该电子器件的制造方法具备在基板上的第1电极上的通电层上使用上述的第1方式至上述的第13方式中的任一种蒸镀掩模组形成第2电极的第2电极形成工序,

155.上述第2电极形成工序具备:

156.通过使用上述第1蒸镀掩模的蒸镀法形成上述第2电极的第1层的工序;

157.通过使用上述第2蒸镀掩模的蒸镀法形成上述第2电极的第2层的工序;和

158.通过使用上述第3蒸镀掩模的蒸镀法形成上述第2电极的第3层的工序。

159.本技术的第23方式为一种电子器件的制造方法,该电子器件的制造方法具备在基板上的第1电极上的通电层上使用上述的第14方式至上述的第21方式中的任一种蒸镀掩模组形成第2电极的第2电极形成工序,

160.上述第2电极形成工序具备:

161.通过使用上述第1蒸镀掩模的蒸镀法形成上述第2电极的第1层的工序;和

162.通过使用上述第2蒸镀掩模的蒸镀法形成上述第2电极的第2层的工序。

163.本技术的第24方式为一种电子器件,该电子器件具备:

164.第1电极,其位于基板上;

165.两个以上的通电层,它们位于上述第1电极上并沿不同的两个方向排列;和

166.两个以上的第2电极,它们位于上述通电层上,

167.上述第2电极具备:沿不同的两个方向排列的两个以上的第1层、沿不同的两个方

向排列的两个以上的第2层、和两个以上的第3层,

168.上述第1层与上述第2层或上述第3层部分重叠。

169.本技术的第25方式为,在上述的第24方式的电子器件中,

170.两个以上的上述第1层可以包含:两个以上的电极第1基本区域,它们沿不同的两个方向排列;和两个以上的电极第1扩张区域,它们按照与上述第2层或上述第3层部分重叠的方式从上述电极第1基本区域延伸出。

171.本技术的第26方式为,在上述的第25方式的电子器件中,

172.两个以上的上述第2层可以包含沿不同的两个方向排列的两个以上的电极第2基本区域、和从上述电极第2基本区域延伸出的两个以上的电极第2扩张区域,或者,两个以上的上述第3层可以包含沿不同的两个方向排列的两个以上的电极第3基本区域、和从上述电极第3基本区域延伸出的两个以上的电极第3扩张区域,

173.两个以上的上述电极第1扩张区域的至少一部分与上述电极第2扩张区域或上述电极第3扩张区域整体或部分重叠。

174.本技术的第27方式为,在上述的第26方式的电子器件中,

175.上述电极第2扩张区域或上述电极第3扩张区域中的与上述电极第1扩张区域重叠的区域可以与上述电极第1基本区域部分重叠。

176.本技术的第28方式为,在上述的第25方式至上述的第27方式各自的电子器件中,

177.在与上述电极第1扩张区域的延伸方向正交的方向上,上述电极第1扩张区域的尺寸可以为上述电极第1基本区域的尺寸的0.9倍以下。

178.本技术的第29方式为,在上述的第25方式至上述的第28方式各自的电子器件中,

179.上述电极第1基本区域的排列方向与上述电极第1扩张区域从上述电极第1基本区域延伸出的方向可以一致。

180.本技术的第30方式为,在上述的第25方式至上述的第28方式各自的电子器件中,

181.上述电极第1基本区域的排列方向与上述电极第1扩张区域从上述电极第1基本区域延伸出的方向可以不同。

182.本技术的第31方式为,在上述的第24方式的电子器件中,

183.两个以上的上述第1层可以包含沿不同的两个方向排列的两个以上的电极第1基本区域和两个以上的电极第1辅助区域,

184.上述电极第1辅助区域可以按照与相邻的两个上述第2层、相邻的两个上述第3层、或者相邻的上述第2层和上述第3层部分重叠的方式延伸。

185.本技术的第32方式为,在上述的第31方式的电子器件中,

186.在与上述电极第1辅助区域的延伸方向正交的方向上,上述电极第1辅助区域的尺寸可以为上述电极第1基本区域的尺寸的0.9倍以下。

187.本技术的第33方式为,在上述的第32方式的电子器件中,

188.上述电极第1辅助区域可以与上述电极第1基本区域连接。

189.本技术的第34方式为,在上述的第32方式的电子器件中,

190.上述电极第1辅助区域可以不与上述电极第1基本区域连接。

191.本技术的第35方式为,在上述的第24方式至上述的第34方式各自的电子器件中,

192.两个以上的上述第1层中的至少一部分上述第1层可以藉由上述第2层和上述第3

层与其他上述第1层连接。

193.本技术的第36方式为,在上述的第24方式至上述的第34方式各自的电子器件中,

194.两个以上的上述第1层中的至少一部分上述第1层可以藉由上述第2层或上述第3层与其他上述第1层连接。

195.本技术的第37方式为一种电子器件,该电子器件具备:

196.第1电极,其位于基板上;

197.通电层,其位于上述第1电极上;和

198.第2电极,其位于上述通电层上,

199.上述第2电极具备:沿第1方向排列的两个以上的第1层、和两个以上的第2层,

200.上述第1层包含:两个以上的电极第1基本区域,它们沿与上述第1方向交叉的第2方向排列;和电极第1扩张区域,其按照连接上述第2方向上相邻的两个上述电极第1基本区域的方式延伸、并在与上述第2方向正交的方向上具有小于上述电极第1基本区域的尺寸,

201.上述第1层与上述第2层部分重叠。

202.本技术的第38方式为,在上述的第37方式的电子器件中,

203.两个以上的上述电极第1基本区域中的至少一部分上述电极第1基本区域可以藉由上述第2层与其他上述电极第1基本区域连接。

204.本技术的第39方式为,在上述的第37方式或上述的第38方式各自的电子器件中,

205.上述电极第1扩张区域与上述第2层可以整体或部分重叠。

206.本技术的第40方式为,在上述的第39方式的电子器件中,

207.上述第2层可以与上述第2方向上相邻的两个上述电极第1基本区域以及与上述两个上述电极第1基本区域连接的上述电极第1扩张区域整体或部分重叠。

208.本技术的第41方式为,在上述的第37方式至上述的第40方式各自的电子器件中,

209.在与上述第2方向正交的方向上,上述电极第1扩张区域的尺寸可以为上述电极第1基本区域的尺寸的0.9倍以下。

210.本技术的第42方式为一种电子器件,该电子器件具备:

211.第1电极,其位于基板上;

212.通电层,其位于上述第1电极上;和

213.第2电极,其位于上述通电层上,

214.上述第2电极具备两个以上的第1层和两个以上的第2层,

215.两个以上的上述第1层包含:两个以上的电极第1基本区域,它们沿第1方向排列并且沿与上述第1方向交叉的第2方向排列;和两个以上的电极第1辅助区域,它们位于上述第2方向上相邻的两个上述电极第1基本区域之间,并在上述第2方向上具有小于上述电极第1基本区域的尺寸,

216.两个以上的上述第2层沿上述第1方向和上述第2方向排列,

217.上述电极第1辅助区域按照与上述第1方向上相邻的两个上述第2层部分重叠的方式延伸。

218.本技术的第43方式为,在上述的第42方式的电子器件中,

219.上述第2层可以按照与上述第2方向上相邻的两个上述电极第1基本区域部分重叠的方式延伸。

220.本技术的第44方式为,在上述的第42方式或上述的第43方式各自的电子器件中,

221.在上述第2方向上,上述电极第1辅助区域的尺寸可以为上述电极第1基本区域的尺寸的0.9倍以下。

222.以下,对具备通过使用本实施方式的蒸镀掩模组形成的电极的电子器件100的一例进行说明。

223.图1是示出电子器件100的截面图。电子器件100可以具备基板91、和沿着基板91的面内方向排列的两个以上的元件110。虽未图示,但元件110也可以沿图1的纵深方向排列。元件110可以具有第1电极120、位于第1电极120上的通电层130、和位于通电层130上的第2电极140。

224.基板91可以为具有绝缘性的板状的部件。基板91优选具有使光透过的透明性。

225.基板91具有规定的透明性时,基板91的透明性优选为能够使来自通电层130的发光透过而进行显示的程度的透明性。例如,可见光区域的基板91的透射率优选为80%以上、更优选为90%以上。基板91的透射率可以通过依照jis k7361-1的塑料-透明材料的全光线透射率的试验方法进行测定。

226.基板91可以具有挠性,也可以不具有挠性,可以根据电子器件100的用途适当选择。

227.作为基板91的材料,可以举出例如石英玻璃、pyrex(注册商标)玻璃、合成石英板等不具有挠性的刚性材料、或者树脂膜、光学用树脂板、薄玻璃等具有挠性的柔性材料等。另外,基材也可以是在树脂膜的单面或双面具有阻隔层的层积体。

228.基板91的厚度可以根据基板91中使用的材料或电子器件100的用途等适当选择,例如可以为0.005mm以上。另外,基板91的厚度可以为5mm以下。

229.元件110构成为:通过在第1电极120与第2电极140之间施加电压,或者通过在第1电极120与第2电极140之间流通电流,从而实现某种功能。

230.第1电极120包含具有导电性的材料。例如,第1电极120包含金属、具有导电性的金属氧化物、其他具有导电性的无机材料等。第1电极120也可以包含铟锡氧化物等具有透明性和导电性的金属氧化物。

231.作为构成第1电极120的材料的示例,可以举出au、cr、mo、ag、mg等金属;被称为ito的氧化铟锡、被称为izo的氧化铟锌、氧化锌、氧化铟等无机氧化物;经金属掺杂的聚噻吩等导电性高分子等。这些导电性材料可以单独使用,也可以将两种以上组合使用。在使用两种以上的情况下,可以对由各材料构成的层进行层积。另外,也可以使用包含两种以上的材料的合金。例如,可以举出mgag等镁合金等。

232.通电层130是通过通电而发挥出某种功能的层。通电是指对通电层130施加电压、或者在通电层130流通电流。作为通电层130的示例,可以举出通过通电而放出光的层、通过通电而使光的透射率或折射率发生变化的层等。通电层130也可以包含半导体材料。半导体材料可以为有机半导体材料,也可以为无机半导体材料。

233.通电层130包含通过通电而放出光的发光层时,通电层130可以进一步包含空穴注入层、空穴传输层、电子传输层、电子注入层等。

234.例如,第1电极120为阳极的情况下,通电层130可以在发光层与第1电极120之间具有空穴注入传输层。空穴注入传输层可以为具有空穴注入功能的空穴注入层,可以为具有

空穴传输功能的空穴传输层,也可以为具有空穴注入功能和空穴传输功能这两种功能的层。另外,空穴注入传输层也可以为空穴注入层和空穴传输层层积而成的层。

235.第2电极140为阴极的情况下,通电层130可以在发光层与第2电极140之间具有电子注入传输层。电子注入传输层可以为具有电子注入功能的电子注入层,可以为具有电子传输功能的电子传输层,也可以为具有电子注入功能和电子传输功能这两种功能的层。另外,电子注入传输层也可以为电子注入层和电子传输层层积而成的层。

236.发光层包含发光材料。发光层也可以包含改善流平性的添加剂。

237.作为发光材料,可以使用公知的材料,可以使用例如色素系材料、金属络合物系材料、高分子系材料等发光材料。

238.作为色素系材料,可以举出例如环戊二烯衍生物、四苯基丁二烯衍生物、三苯胺衍生物、噁二唑衍生物、吡唑并喹啉衍生物、二苯乙烯基苯衍生物、二苯乙烯基亚芳基衍生物、噻咯衍生物、噻吩环化合物、吡啶环化合物、紫环酮衍生物、苝衍生物、低聚噻吩衍生物、噁二唑二聚物、吡唑啉二聚物等。

239.作为金属络合物系材料,可以举出例如羟基喹啉铝络合物、苯并羟基喹啉铍络合物、苯并噁唑锌络合物、苯并噻唑锌络合物、偶氮甲基锌络合物、卟啉锌络合物、铕络合物等中心金属具有al、zn、be等或tb、eu、dy等稀土金属、配体具有噁二唑、噻二唑、苯基吡啶、苯基苯并咪唑、喹啉结构等的金属络合物。

240.作为高分子系材料,可以举出例如聚对苯撑乙烯衍生物、聚噻吩衍生物、聚对苯撑衍生物、聚硅烷衍生物、聚乙炔衍生物、聚乙烯基咔唑衍生物、聚芴衍生物、聚喹喔啉衍生物、和它们的共聚物等。

241.出于提高发光效率或改变发射光波长等目的,发光层可以包含掺杂剂。作为掺杂剂,可以举出例如苝衍生物、香豆素衍生物、红荧烯衍生物、喹吖啶酮衍生物、方酸内鎓盐衍生物、卟啉衍生物、苯乙烯基系色素、并四苯衍生物、吡唑啉衍生物、十环烯、吩噁嗪酮、喹喔啉衍生物、咔唑衍生物、芴衍生物等。另外,作为掺杂剂,也可以使用中心具有铂或铱等重金属离子、并显示出磷光的有机金属络合物。掺杂剂可以单独使用1种,也可以使用2种以上。

242.另外,作为发光材料和掺杂剂,也可以使用例如日本特开2010-272891号公报的[0094]~[0099]、国际公开第2012/132126号的[0053]~[0057]中记载的材料。

[0243]

关于发光层的膜厚,只要是能够提供电子与空穴的再结合场所而表现出发光功能的膜厚就没有特别限定,例如可以为1nm以上,另外可以为500nm以下。

[0244]

作为用于空穴注入传输层的空穴注入传输性材料,可以使用公知的材料。可以举出例如三唑衍生物、噁二唑衍生物、咪唑衍生物、聚芳基烷烃衍生物、吡唑啉衍生物、吡唑啉酮衍生物、苯二胺衍生物、芳基胺衍生物、氨基取代查耳酮衍生物、噁唑衍生物、苯乙烯基蒽衍生物、芴酮衍生物、腙衍生物、均二苯代乙烯衍生物、硅氮烷衍生物、聚噻吩衍生物、聚苯胺衍生物、聚吡咯衍生物、苯基胺衍生物、蒽衍生物、咔唑衍生物、芴衍生物、二苯乙烯基苯衍生物、聚苯乙炔衍生物、卟啉衍生物、苯乙烯基胺衍生物等。另外,可示例出螺环化合物、酞菁化合物、金属氧化物等。另外,也可以适当选择使用例如日本特开2011-119681号公报、国际公开第2012/018082号、日本特开2012-069963号公报、国际公开第2012/132126号的[0106]中记载的化合物。

[0245]

需要说明的是,空穴注入传输层为空穴注入层和空穴传输层层积而成的层时,可

以使空穴注入层含有添加剂a,也可以使空穴传输层含有添加剂a,还可以使空穴注入层和空穴传输层含有添加剂a。添加剂a可以为低分子化合物,也可以为高分子化合物。具体而言,可以举出氟系化合物、酯系化合物、烃系化合物等。

[0246]

作为用于电子注入传输层的电子注入传输性材料,可以使用公知的材料。可以举出例如碱金属类、碱金属的合金、碱金属的卤化物、碱土金属类、碱土金属的卤化物、碱土金属的氧化物、碱金属的有机络合物、镁的卤化物或氧化物、氧化铝等。另外,作为电子注入传输性材料,可以举出例如浴铜灵、红菲绕啉、菲咯啉衍生物、三唑衍生物、噁二唑衍生物、吡啶衍生物、硝基取代芴衍生物、蒽醌二甲烷衍生物、二苯基醌衍生物、噻喃二氧化物衍生物、萘或苝等芳香环四羧酸酐、碳化二亚胺、亚芴基甲烷衍生物、蒽醌二甲烷衍生物、蒽酮衍生物、喹喔啉衍生物、羟基喹啉络合物等金属络合物、酞菁化合物、二苯乙烯基吡嗪衍生物等。

[0247]

另外,也可以形成在电子传输性的有机材料中掺杂碱金属或碱土金属的金属掺杂层,将其作为电子注入传输层。作为电子传输性的有机材料,可以举出例如浴铜灵、红菲绕啉、菲咯啉衍生物、三唑衍生物、噁二唑衍生物、吡啶衍生物、三(8-羟基喹啉络)铝(alq3)等金属络合物以及它们的高分子衍生物等。另外,作为进行掺杂的金属,可以举出li、cs、ba、sr等。

[0248]

第2电极140包含金属等具有导电性的材料。第2电极140通过使用后述蒸镀掩模20的蒸镀法形成于通电层130上。作为构成第2电极140的材料的示例,可以举出铂、金、银、铜、铁、锡、铬、铝、铟、锂、钠、钾、钙、镁、铬、碳等。这些材料可以单独使用,也可以将两种以上组合使用。在使用两种以上的情况下,可以对由各材料构成的层进行层积。另外,也可以使用包含两种以上的材料的合金。可以举出例如mgag等镁合金、alli、alca、almg等铝合金、碱金属类和碱土金属类的合金等。

[0249]

电子器件100为有机el显示装置的情况下,元件110为像素,通电层130包含发光层。

[0250]

如图1所示,在一个基板91上可以设有与两个以上的电子器件100对应的两个以上的元件110。电子器件100为有机el显示装置等显示装置的情况下,一个电子器件100相当于一个画面。

[0251]

图2是将电子器件100放大示出的截面图。图2是后述的图6所示的电子器件100的沿着ii-ii线的截面图。图2中,沿着基板91的法线方向观察时第1电极120与第2电极140重叠,并且在第1电极120与第2电极140之间存在通电层130的部分作为元件以符号110来表示。如图2所示,在沿着基板91的法线方向观察时,第2电极140不仅位于与第1电极120重叠的区域,还可以位于不与第1电极120重叠的区域。需要说明的是,在以下说明中,当沿着基板91或蒸镀掩模20之类的板状构件的面的法线方向观察时两个构成要素重叠可简单表示为“重叠”。

[0252]

对图2的第2电极140进行详细说明。第2电极140具有第1层140a和第2层140b。第1层140a是通过使用后述第1蒸镀掩模20a的蒸镀法形成的层。第1层140a包含:与第1电极120重叠的电极第1基本区域141a、和位于相邻的两个元件110之间的电极第1扩张区域142a。电极第1扩张区域142a可以与电极第1基本区域141a连接,也可以不连接。电极第1扩张区域142a不与电极第1基本区域141a连接的情况下,电极第1扩张区域142a藉由第2层140b与电极第1基本区域141a电连接。

[0253]

第2层140b是通过使用后述第2蒸镀掩模20b的蒸镀法形成的层。如图2所示,第2层140b与第1层140a的电极第1扩张区域142a重叠。通过设置第2层140b,位于相邻的两个元件110之间的第2电极140的厚度增加。因此,与不存在第2层140b的情况相比,能够降低相邻的两个元件110的电极第1基本区域141a之间的电阻。

[0254]

图2中,符号t1表示第2电极140中的构成元件110的部分的厚度的最小值,符号t2表示第2电极140中的位于相邻的两个元件110之间的部分的厚度的最大值。厚度t2比厚度t1大第2层140b的厚度的量。厚度t2可以为厚度t1的1.2倍以上、可以为1.5倍以上、可以为1.8倍以上、可以为2.0倍以上、可以为2.2倍以上、也可以为2.5倍以上。由此,能够降低相邻的两个元件110的电极第1基本区域141a之间的电阻。另外,厚度t2可以为厚度t1的5.0倍以下、可以为4.5倍以下、可以为4.0倍以下、可以为3.5倍以下、也可以为3.0倍以下。

[0255]

厚度t2相对于厚度t1的比例即t2/t1的范围可以由1.2、1.5、1.8、2.0、2.2、2.5构成的第1组、和/或3.0、3.5、4.0、4.5、5.0构成的第2组确定。t2/t1的范围可以由上述的第1组中包含的值中的任意一者与上述的第2组中包含的值中的任意一者的组合确定。t2/t1的范围可以由上述的第1组中包含的值中的任意两者的组合确定。t2/t1的范围可以由上述的第2组中包含的值中的任意两者的组合确定。例如,t2/t1可以为1.2以上5.0以下、可以为1.2以上4.5以下、可以为1.2以上4.0以下、可以为1.2以上3.5以下、可以为1.2以上3.0以下、可以为1.2以上2.5以下、可以为1.2以上2.2以下、可以为1.2以上2.0以下、可以为1.2以上1.8以下、可以为1.2以上1.5以下、可以为1.5以上5.0以下、可以为1.5以上4.5以下、可以为1.5以上4.0以下、可以为1.5以上3.5以下、可以为1.5以上3.0以下、可以为1.5以上2.5以下、可以为1.5以上2.2以下、可以为1.5以上2.0以下、可以为1.5以上1.8以下、可以为1.8以上5.0以下、可以为1.8以上4.5以下、可以为1.8以上4.0以下、可以为1.8以上3.5以下、可以为1.8以上3.0以下、可以为1.8以上2.5以下、可以为1.8以上2.2以下、可以为1.8以上2.0以下、可以为2.0以上5.0以下、可以为2.0以上4.5以下、可以为2.0以上4.0以下、可以为2.0以上3.5以下、可以为2.0以上3.0以下、可以为2.0以上2.5以下、可以为2.0以上2.2以下、可以为2.2以上5.0以下、可以为2.2以上4.5以下、可以为2.2以上4.0以下、可以为2.2以上3.5以下、可以为2.2以上3.0以下、可以为2.2以上2.5以下、可以为2.5以上5.0以下、可以为2.5以上4.5以下、可以为2.5以上4.0以下、可以为2.5以上3.5以下、可以为2.5以上3.0以下、可以为3.0以上5.0以下、可以为3.0以上4.5以下、可以为3.0以上4.0以下、可以为3.0以上3.5以下、可以为3.5以上5.0以下、可以为3.5以上4.5以下、可以为3.5以上4.0以下、可以为4.0以上5.0以下、可以为4.0以上4.5以下、也可以为4.5以上5.0以下。

[0256]

关于厚度t2相对于厚度t1的比例的上述各范围也可以以图1~图16所示的实施方式以外的方式来采用。

[0257]

厚度t1可以为10nm以上、可以为20nm以上、可以为50nm以上、可以为100nm以上、也可以为200nm以上。另外,厚度t1可以为10μm以下、可以为5μm以下、可以为2μm以下、可以为1μm以下、也可以为500nm以下。

[0258]

厚度t1的范围可以由10nm、20nm、50nm、100nm、200nm构成的第1组、和/或10μm、5μm、2μm、1μm、500nm构成的第2组确定。厚度t1的范围可以由上述的第1组中包含的值中的任意一者与上述的第2组中包含的值中的任意一者的组合确定。厚度t1的范围可以由上述的第1组中包含的值中的任意两者的组合确定。厚度t1的范围可以由上述的第2组中包含的值

中的任意两者的组合确定。例如,厚度t1可以为10nm以上10μm以下、可以为10nm以上5μm以下、可以为10nm以上2μm以下、可以为10nm以上1μm以下、可以为10nm以上500nm以下、可以为10nm以上200nm以下、可以为10nm以上100nm以下、可以为10nm以上50nm以下、可以为10nm以上20nm以下、可以为20nm以上10μm以下、可以为20nm以上5μm以下、可以为20nm以上2μm以下、可以为20nm以上1μm以下、可以为20nm以上500nm以下、可以为20nm以上200nm以下、可以为20nm以上100nm以下、可以为20nm以上50nm以下、可以为50nm以上10μm以下、可以为50nm以上5μm以下、可以为50nm以上2μm以下、可以为50nm以上1μm以下、可以为50nm以上500nm以下、可以为50nm以上200nm以下、可以为50nm以上100nm以下、可以为100nm以上10μm以下、可以为100nm以上5μm以下、可以为100nm以上2μm以下、可以为100nm以上1μm以下、可以为100nm以上500nm以下、可以为100nm以上200nm以下、可以为200nm以上10μm以下、可以为200nm以上5μm以下、可以为200nm以上2μm以下、可以为200nm以上1μm以下、可以为200nm以上500nm以下、可以为500nm以上10μm以下、可以为500nm以上5μm以下、可以为500nm以上2μm以下、可以为500nm以上1μm以下、可以为1μm以上10μm以下、可以为1μm以上5μm以下、可以为1μm以上2μm以下、可以为2μm以上10μm以下、可以为2μm以上5μm以下、也可以为5μm以上10μm以下。

[0259]

关于厚度t1的上述各范围也可以以图1~图16所示的实施方式以外的方式来采用。

[0260]

接着,对沿着基板91的法线方向观察时的电子器件100的元件110的各层构成的一例进行说明。

[0261]

图3是示出形成有第1电极120的状态的基板91的一例的俯视图。如图3所示,第1电极120可以具有在第1方向d1延伸的条纹状的形状。另外,两个以上的第1电极120也可以沿与第1方向d1交叉的第2方向d2排列。在图3所示的示例中,第1方向d1和第2方向d2为基板91的外缘延伸的方向。第2方向d2可以与第1方向d1正交。

[0262]

在基板91可以形成有沿基板91的外缘排列的两个以上的端子部125、将端子部125与第1电极120电连接的配线126等。端子部125、配线126可以利用与第1电极120相同的材料、由同一工序形成于基板91上。

[0263]

另外,在基板91可以形成有对准标记93。对准标记93例如形成于基板91的角落。对准标记93在于基板91形成元件110的各层的工序中可以用于基板91的位置对准。例如,基板91可以用于调整后述的蒸镀掩模20相对于基板91的位置。

[0264]

图4是示出形成有第1电极120和通电层130的状态的基板91的一例的俯视图。在图4所示的示例中,通电层130形成为遍布展开在两个以上的第1电极120上。图4所示的通电层130例如可以通过利用蒸镀法使有机材料附着于基板91上或第1电极120上而形成,该蒸镀法使用了形成有与通电层130的形状对应的贯通孔的蒸镀掩模。

[0265]

图5是示出形成有第1电极120、通电层130和第2电极140的第1层140a的状态的基板91的一例的俯视图。如图5所示,第1层140a可以在第2方向d2上延伸。另外,两个以上的第1层140a也可以在第1方向d1上排列。

[0266]

如图5所示,第1层140a可以包含:两个以上的电极第1基本区域141a,它们沿第2方向d2排列;和电极第1扩张区域142a,其以连接在第2方向d2上相邻的两个电极第1基本区域141a的方式延伸。电极第1基本区域141a配置成与第1电极120整体或部分重叠。这种情况

下,若对第1电极120与第2电极140的电极第1基本区域141a之间施加电压,则位于两者之间的通电层130被驱动。通电层130为发光层时,从通电层130放出光,光从第2电极140侧或第1电极120侧被取出到外部。

[0267]

如图5所示,在基板91可以形成有沿基板91的外缘排列的两个以上的端子部145a、将端子部145a与第2电极140的第1层140a电连接的配线146a等。端子部145a、配线146a可以利用与第2电极140的第1层140a相同的材料、由同一工序形成于基板91上。即,端子部145a、配线146a可以通过使用第1蒸镀掩模20a的蒸镀法与第1层140a同时形成。由此,能够提高相对于第1层140a的端子部145a、配线146a的相对位置精度。

[0268]

如图5所示,在与相邻的两个电极第1基本区域141a排列的方向即第2方向d2正交的方向上,电极第1扩张区域142a的尺寸小于电极第1基本区域141a的尺寸。即,电极第1扩张区域142a的宽度小于电极第1基本区域141a的宽度。换言之,第1层140a在与第2方向d2正交的方向上具有第1尺寸以及小于第1尺寸的第2尺寸。具有第1尺寸的区域和具有第2尺寸的区域分别在第2方向d2上交替排列。因此,在第2方向d2上相邻的两个元件110之间的区域,光容易透过电子器件100。由此,例如,与电极第1扩张区域142a具有与电极第1基本区域141a相同宽度的情况相比,能够提高电子器件100整体的透射率。

[0269]

如后所述,电极第1基本区域141a主要由穿过第1蒸镀掩模20a的掩模第1基本区域26a的蒸镀材料构成。另外,电极第1扩张区域142a主要由穿过第1蒸镀掩模20a的掩模第1扩张区域27a的蒸镀材料构成。因此,电极第1基本区域141a的尺寸与掩模第1基本区域26a的尺寸对应,电极第1扩张区域142a的尺寸与掩模第1扩张区域27a的尺寸对应。例如,电极第1扩张区域142a的宽度相对于电极第1基本区域141a的宽度的比例对应于后述的掩模第1扩张区域27a的尺寸w12相对于掩模第1基本区域26a的尺寸w11的比例。

[0270]

另外,若使电极第1扩张区域142a的宽度小于电极第1基本区域141a的宽度,则相邻的两个电极第1基本区域141a之间的电阻增加。考虑到这点,本实施方式中,在电极第1扩张区域142a上形成了上述的第2层140b。

[0271]

图6是示出形成有第1电极120、通电层130、第2电极140的第1层140a和第2电极140的第2层140b的状态的基板91的一例的俯视图。如图6所示,第2层140b与位于第2方向d2上相邻的两个电极第1基本区域141a之间的电极第1扩张区域142a整体或部分重叠。由此,能够降低相邻的两个电极第1基本区域141a之间的电阻。第2层140b也可以与在第2方向d2上相邻的两个电极第1基本区域141a部分重叠。

[0272]

需要说明的是,上述的端子部145a、配线146a也可以通过使用第2蒸镀掩模20b的蒸镀法与第2层140b同时形成。由此,能够提高相对于第2层140b的端子部145a、配线146a的相对位置精度。另外,上述的端子部145a、配线146a除了可以包含通过使用第1蒸镀掩模20a的蒸镀法形成的层以外,还可以包含通过使用第2蒸镀掩模20b的蒸镀法形成的层。

[0273]

接着,对通过蒸镀法形成上述的电子器件100的第2电极140的方法进行说明。图7是示出实施使蒸镀材料蒸镀于对象物的蒸镀处理的蒸镀装置80的图。

[0274]

如图7所示,蒸镀装置80可以在其内部具备蒸镀源81、加热器83以及蒸镀掩模装置10。另外,蒸镀装置80也可以进一步具备用于使蒸镀装置80的内部为真空气氛的排气单元。蒸镀源81例如为坩埚,其容纳有机发光材料等蒸镀材料82。加热器83对蒸镀源81进行加热,在真空气氛下使蒸镀材料82蒸发。蒸镀掩模装置10配置成与蒸镀源81对置。

[0275]

如图7所示,蒸镀掩模装置10具备至少一个蒸镀掩模20。蒸镀掩模装置10也可以进一步具备支撑蒸镀掩模20的框架15。为了抑制蒸镀掩模20弯曲,框架15以对蒸镀掩模20施加张力的状态支撑蒸镀掩模20。

[0276]

作为蒸镀掩模装置10的蒸镀掩模20,可以使用后述的第1蒸镀掩模20a、第2蒸镀掩模20b、第3蒸镀掩模20c等。在下述说明中,对蒸镀掩模的构成中的第1蒸镀掩模20a、第2蒸镀掩模20b、第3蒸镀掩模20c等共通的构成进行说明时,使用“蒸镀掩模20”的术语和符号。关于有效区域等蒸镀掩模20的蒸镀掩模的构成要素,同样地,对第1蒸镀掩模20a、第2蒸镀掩模20b、第3蒸镀掩模20c等共通的内容进行说明时,作为符号,使用“22”等不带有字母的仅为数字的符号。另一方面,对第1蒸镀掩模20a、第2蒸镀掩模20b、第3蒸镀掩模20c各自特有的内容进行说明时,使用在数字后带有“a”、“b”、“c”等对应的字母的符号。

[0277]

如图7所示,蒸镀掩模装置10配置于蒸镀装置80内,使得蒸镀掩模20对附着蒸镀材料82的对象物即基板91对置。蒸镀掩模20具有使从蒸镀源81飞来的蒸镀材料82穿过的两个以上的贯通孔25。在下述说明中,将蒸镀掩模20的面中的、飞来的蒸镀材料82附着的位于基板91侧的面称为第1面201,将位于第1面201的相反侧的面称为第2面202。

[0278]

如图7所示,蒸镀掩模装置10也可以具备配置于基板91的与蒸镀掩模20相反侧的面的磁铁85。通过设置磁铁85,利用磁力将蒸镀掩模20向磁铁85侧吸引,能够使蒸镀掩模20与基板91密合。由此,能够抑制在蒸镀工序中产生阴影,能够提高利用附着于基板91的蒸镀材料82在基板91形成的蒸镀层的尺寸精度及位置精度。另外,也可以使用利用静电力的静电夹头使蒸镀掩模20与基板91密合。

[0279]

图8是示出从蒸镀掩模20的第1面201侧观察蒸镀掩模装置10时的俯视图。如图8所示,蒸镀掩模装置10可以具备两个以上的蒸镀掩模20。本实施方式中,各蒸镀掩模20具有沿第1方向d1等一个方向延伸的矩形形状。在蒸镀掩模装置10中,两个以上的蒸镀掩模20在与蒸镀掩模20的长度方向交叉的宽度方向上排列。各蒸镀掩模20在蒸镀掩模20的长度方向的两端部例如通过焊接被固定于框架15。另外,虽未图示,但蒸镀掩模装置10也可以具备被固定于框架15并在蒸镀掩模20的厚度方向与蒸镀掩模20部分重叠的部件。作为这种部件的示例,可以举出:在与蒸镀掩模20的长度方向交叉的方向上延伸并对蒸镀掩模20进行支撑的部件;与相邻的两个蒸镀掩模之间的间隙重叠的部件;等。

[0280]

图8所示的蒸镀掩模20具有:通过焊接等被固定于框架15的一对耳部17;和位于耳部17之间的中间部18。中间部18可以具有至少一个有效区域22和位于有效区域22的周围的周围区域23。在图8所示的示例中,中间部18包含沿着蒸镀掩模20的长度方向隔开规定间隔而排列的两个以上的有效区域22。周围区域23包围两个以上的有效区域22。

[0281]

在使用蒸镀掩模20制作有机el显示装置等显示装置时,一个有效区域22对应于一个有机el显示装置的显示区域、即一个画面。需要说明的是,一个有效区域22也可以对应于两个以上的显示区域。另外,虽未图示,但也可以在蒸镀掩模20的宽度方向隔开规定间隔排列有两个以上的有效区域22。

[0282]

有效区域22可以具有例如在俯视时为近似四边形形状、更准确地说在俯视时为近似矩形的轮廓。需要说明的是,虽未图示,但各有效区域22可以根据有机el显示装置的显示区域的形状具有各种形状的轮廓。例如各有效区域22可以具有圆形的轮廓。

[0283]

图9是将具备在形成上述的第2电极140的第1层140a时使用的第1蒸镀掩模20a的

第1蒸镀掩模装置10a的一部分放大示出的俯视图。第1蒸镀掩模20a具有包含沿不同的两个方向排列的区域的两个以上的第1贯通孔25a。在图9所示的示例中,不同的两个方向为第1方向d1和第2方向d2。

[0284]

图10是将具备在形成上述的第2电极140的第2层140b时使用的第2蒸镀掩模20b的第2蒸镀掩模装置10b的一部分放大示出的俯视图。第2蒸镀掩模20b具有沿不同的两个方向排列的两个以上的第2贯通孔25b。在图10所示的示例中,不同的两个方向为第1方向d1和第2方向d2。

[0285]

第2蒸镀掩模装置10b例如用于在蒸镀装置80中使用第1蒸镀掩模装置10a在基板91形成第2电极140的第1层140a后,在蒸镀装置80中在基板91形成第2电极140的第2层140b。这样,在制造电子器件100的工序中,依次使用第1蒸镀掩模20a、第2蒸镀掩模20b等两个以上的蒸镀掩模20。将为了制造电子器件100而使用的两个以上的蒸镀掩模20的组也称为“蒸镀掩模组”。

[0286]

图11是示出第1蒸镀掩模20a、第2蒸镀掩模20b、第3蒸镀掩模20c等蒸镀掩模20的截面结构的一例的图。蒸镀掩模20具有形成于金属板50的两个以上的贯通孔25。贯通孔25使金属板50从第1面201贯通至第2面202。

[0287]

图11所示的贯通孔25可以通过从第1面201侧和第2面202侧蚀刻金属板50而形成。贯通孔25的壁面包括位于第1面201侧的第1壁面31、和位于第2面202侧的第2壁面36。第1壁面31是从第1面201侧蚀刻金属板50时形成的第1凹部30的面。第2壁面36是从第2面202侧蚀刻金属板50时形成的第2凹部35的面。第1凹部30的第1壁面31与第2凹部35的第2壁面36在连接部42连接。

[0288]

在使用蒸镀掩模20的蒸镀法中,从第2面202侧向第1面201侧在贯通孔25中穿过的蒸镀材料82附着于基板91上,由此在基板91形成上述的第1层140a、第2层140b等层。形成于基板91的层的在基板91的面内方向上的轮廓由第1面201上的贯通孔25的端部251的轮廓决定。在后述的图12~图16等俯视图中所示的贯通孔25的轮廓为贯通孔25的端部251的轮廓。

[0289]

蒸镀掩模20的厚度t优选为100μm以下。蒸镀掩模20的厚度t可以为50μm以下、可以为40μm以下、可以为35μm以下、可以为30μm以下、可以为25μm以下、也可以为20μm以下。另一方面,蒸镀掩模20的厚度过小时,蒸镀掩模20的强度降低,蒸镀掩模20容易产生损伤或变形。考虑到这点,蒸镀掩模20的厚度t优选为5μm以上。蒸镀掩模20的厚度t可以为8μm以上、可以为10μm以上、可以为12μm以上、可以为13μm以上、也可以为15μm以上。

[0290]

蒸镀掩模20的厚度t的范围可以由5μm、8μm、10μm、12μm、13μm、15μm构成的第1组、和/或100μm、50μm、40μm、35μm、30μm、25μm、20μm构成的第2组确定。厚度t的范围可以由上述的第1组中包含的值中的任意一者与上述的第2组中包含的值中的任意一者的组合确定。厚度t的范围可以由上述的第1组中包含的值中的任意两者的组合确定。厚度t的范围可以由上述的第2组中包含的值中的任意两者的组合确定。例如,蒸镀掩模20的厚度t的范围可以为5μm以上100μm以下、可以为5μm以上50μm以下、可以为5μm以上40μm以下、可以为5μm以上35μm以下、可以为5μm以上30μm以下、可以为5μm以上25μm以下、可以为5μm以上20μm以下、可以为5μm以上15μm以下、可以为5μm以上13μm以下、可以为5μm以上12μm以下、可以为5μm以上10μm以下、可以为5μm以上8μm以下、可以为8μm以上100μm以下、可以为8μm以上50μm以下、可以为8μm以上40μm以下、可以为8μm以上35μm以下、可以为8μm以上30μm以下、可以为8μm以上

25μm以下、可以为8μm以上20μm以下、可以为8μm以上15μm以下、可以为8μm以上13μm以下、可以为8μm以上12μm以下、可以为8μm以上10μm以下、可以为10μm以上100μm以下、可以为10μm以上50μm以下、可以为10μm以上40μm以下、可以为10μm以上35μm以下、可以为10μm以上30μm以下、可以为10μm以上25μm以下、可以为10μm以上20μm以下、可以为10μm以上15μm以下、可以为10μm以上13μm以下、可以为10μm以上12μm以下、可以为12μm以上100μm以下、可以为12μm以上50μm以下、可以为12μm以上40μm以下、可以为12μm以上35μm以下、可以为12μm以上30μm以下、可以为12μm以上25μm以下、可以为12μm以上20μm以下、可以为12μm以上15μm以下、可以为12μm以上13μm以下、可以为13μm以上100μm以下、可以为13μm以上50μm以下、可以为13μm以上40μm以下、可以为13μm以上35μm以下、可以为13μm以上30μm以下、可以为13μm以上25μm以下、可以为13μm以上20μm以下、可以为13μm以上15μm以下、可以为15μm以上100μm以下、可以为15μm以上50μm以下、可以为15μm以上40μm以下、可以为15μm以上35μm以下、可以为15μm以上30μm以下、可以为15μm以上25μm以下、可以为15μm以上20μm以下、可以为20μm以上100μm以下、可以为20μm以上50μm以下、可以为20μm以上40μm以下、可以为20μm以上35μm以下、可以为20μm以上30μm以下、可以为20μm以上25μm以下、可以为25μm以上100μm以下、可以为25μm以上50μm以下、可以为25μm以上40μm以下、可以为25μm以上35μm以下、可以为25μm以上30μm以下、可以为30μm以上100μm以下、可以为30μm以上50μm以下、可以为30μm以上40μm以下、可以为30μm以上35μm以下、可以为35μm以上100μm以下、可以为35μm以上50μm以下、可以为35μm以上40μm以下、可以为40μm以上100μm以下、可以为40μm以上50μm以下、也可以为50μm以上100μm以下。

[0291]

需要说明的是,蒸镀掩模20的厚度t是周围区域23的厚度、即蒸镀掩模20中的未形成贯通孔25的部分的厚度。

[0292]

关于蒸镀掩模20的厚度t的上述各范围也可以以图1~图16所示的实施方式以外的方式来采用。

[0293]

作为测定蒸镀掩模20的厚度的方法,可以采用接触式的测定方法。作为接触式的测定方法,可以使用具备滚珠导套式柱塞的、heidenhain公司制造的测长仪heidenhaim-metro的“mt1271”。

[0294]

需要说明的是,蒸镀掩模20的贯通孔25的截面形状不限于图11所示的形状。另外,蒸镀掩模20的贯通孔25的形成方法不限于蚀刻,可以采用各种方法。例如,通过以产生贯通孔25的方式进行镀覆,也可以形成蒸镀掩模20。

[0295]

作为构成蒸镀掩模20的材料,例如,可以使用包含镍的铁合金。铁合金除了包含镍以外还可以进一步包含钴。例如,作为蒸镀掩模20的材料,可以使用镍和钴的含量合计为30质量%以上且54质量%以下、并且钴的含量为0质量%以上且6质量%以下的铁合金。作为包含镍或镍和钴的铁合金的具体例,可以举出包含34质量%以上且38质量%以下的镍的因瓦合金材料、除了包含30质量%以上且34质量%以下的镍以外还进一步包含钴的超因瓦合金材料、包含38质量%以上且54质量%以下的镍的低热膨胀fe-ni系镀覆合金等。通过使用这样的铁合金,能够降低蒸镀掩模20的热膨胀系数。例如,在使用玻璃基板作为基板91的情况下,能够使蒸镀掩模20的热膨胀系数为与玻璃基板同等的低值。由此,在蒸镀工序时,能够抑制形成于基板91的蒸镀层的尺寸精度、位置精度因蒸镀掩模20与基板91之间的热膨胀系数差而降低。

[0296]

关于构成蒸镀掩模20的材料的组成的上述各范围也可以以图1~图16所示的实施方式以外的方式来采用。

[0297]

接着,对第1蒸镀掩模20a进行详细说明。图12是示出从第1面201侧观察时的第1蒸镀掩模20a的一例的俯视图。图13是将图12的第1蒸镀掩模20a的一部分放大示出的俯视图。

[0298]

如图12所示,第1蒸镀掩模20a具有两个以上的第1贯通孔25a,该两个以上的第1贯通孔25a包含沿不同的两个方向排列的区域。两个以上的第1贯通孔25a包含沿不同的两个方向排列的两个以上的掩模第1基本区域26a、与以连接相邻的两个掩模第1基本区域26a的方式延伸的掩模第1扩张区域27a。

[0299]

掩模第1基本区域26a是构成上述第2电极140的第1层140a的电极第1基本区域141a的蒸镀材料主要穿过的区域。在图12所示的示例中,两个以上的掩模第1基本区域26a沿第1方向d1和第2方向d2排列。如图12所示,在第2方向d2上相邻的两个掩模第1基本区域26a之间的间隔小于在第1方向d1上相邻的两个掩模第1基本区域26a之间的间隔。

[0300]

掩模第1扩张区域27a是构成上述第2电极140的第1层140a的电极第1扩张区域142a的蒸镀材料主要穿过的区域。在图12所示的示例中,掩模第1扩张区域27a以连接在第2方向d2上相邻的两个掩模第1基本区域26a的方式沿第2方向d2延伸。

[0301]

掩模第1扩张区域27a在与相邻的两个掩模第1基本区域26a排列的方向正交的方向上具有小于掩模第1基本区域26a的尺寸。在图13所示的示例中,掩模第1扩张区域27a在与在第2方向d2上相邻的两个掩模第1基本区域26a排列的方向即第2方向d2正交的第1方向d1上具有小于掩模第1基本区域26a的尺寸。换言之,第1贯通孔25a在与第2方向d2正交的第1方向d1上具有第1尺寸w11以及小于第1尺寸w11的第2尺寸w12。具有第1尺寸w11的区域和具有第2尺寸w12的区域分别在第2方向d2上交替排列。在第1方向d1上,掩模第1扩张区域27a的尺寸w12可以为掩模第1基本区域26a的尺寸w11的0.9倍以下、可以为0.8倍以下、可以为0.7倍以下、可以为0.6倍以下、也可以为0.5倍以下。由此,在与掩模第1基本区域26a对应形成的第2电极140的两个电极第1基本区域141a之间的区域,光容易透过电子器件100。另外,在第1方向d1上,掩模第1扩张区域27a的尺寸w12可以为掩模第1基本区域26a的尺寸w11的0.05倍以上、可以为0.1倍以上、可以为0.2倍以上、可以为0.3倍以上、也可以为0.4倍以上。

[0302]

尺寸w12相对于尺寸w11的比例即w12/w11的范围可以由0.05、0.1、0.2、0.3、0.4构成的第1组、和/或0.9、0.8、0.7、0.6、0.5构成的第2组确定。w12/w11的范围可以由上述的第1组中包含的值中的任意一者与上述的第2组中包含的值中的任意一者的组合确定。例如,w12/w11可以为0.05以上0.9以下、可以为0.05以上0.8以下、可以为0.05以上0.7以下、可以为0.05以上0.6以下、可以为0.05以上0.5以下、可以为0.05以上0.4以下、可以为0.05以上0.3以下、可以为0.05以上0.2以下、可以为0.05以上0.1以下、可以为0.1以上0.9以下、可以为0.1以上0.8以下、可以为0.1以上0.7以下、可以为0.1以上0.6以下、可以为0.1以上0.5以下、可以为0.1以上0.4以下、可以为0.1以上0.3以下、可以为0.1以上0.2以下、可以为0.2以上0.9以下、可以为0.2以上0.8以下、可以为0.2以上0.7以下、可以为0.2以上0.6以下、可以为0.2以上0.5以下、可以为0.2以上0.4以下、可以为0.2以上0.3以下、可以为0.3以上0.9以下、可以为0.3以上0.8以下、可以为0.3以上0.7以下、可以为0.3以上0.6以下、可以为0.3以上0.5以下、可以为0.3以上0.4以下、可以为0.4以上0.9以下、可以为0.4以上0.8以下、可以

为0.4以上0.7以下、可以为0.4以上0.6以下、可以为0.4以上0.5以下、可以为0.5以上0.9以下、可以为0.5以上0.8以下、可以为0.5以上0.7以下、可以为0.5以上0.6以下、可以为0.6以上0.9以下、可以为0.6以上0.8以下、可以为0.6以上0.7以下、可以为0.7以上0.9以下、可以为0.7以上0.8以下、也可以为0.8以上0.9以下。

[0303]

如图12所示,第1蒸镀掩模20a可以具有对准标记29a。对准标记29a例如形成于第1蒸镀掩模20a的有效区域22a的角落。对准标记29a在利用第1蒸镀掩模20a通过蒸镀法在基板91形成第2电极140的第1层140a的工序中,可以用于第1蒸镀掩模20a相对于基板91的位置对准。

[0304]

接着,对第2蒸镀掩模20b进行详细说明。图14是示出从第1面201侧观察时的第2蒸镀掩模20b的一例的俯视图。图15是将图14的第2蒸镀掩模20b的一部分放大示出的俯视图。

[0305]

如图14和图15所示,第2蒸镀掩模20b具有沿不同的两个方向排列的两个以上的第2贯通孔25b。第2贯通孔25b是构成上述第2电极140的第2层140b的蒸镀材料主要穿过的区域。在图12所示的示例中,第2贯通孔25b沿第2方向d2延伸。

[0306]

图15中,符号w21表示与第2贯通孔25b延伸的第2方向d2正交的第1方向d1上的第2贯通孔25b的尺寸。在第1方向d1上,第2贯通孔25b的尺寸w21小于上述第1蒸镀掩模20a的第1贯通孔25a的掩模第1基本区域26a的尺寸w11。第2贯通孔25b的尺寸w21相对于掩模第1基本区域26a的尺寸w11的比例的范围与掩模第1扩张区域27a的尺寸w12相对于掩模第1基本区域26a的尺寸w11的比例的上述范围相同,因此省略详细的说明。

[0307]

在第1方向d1上,第2贯通孔25b的尺寸w21可以小于或大于上述第1蒸镀掩模20a的掩模第1扩张区域27a的尺寸w12,也可以相同。

[0308]

如图14所示,第2蒸镀掩模20b可以具有对准标记29b。对准标记29b与第1蒸镀掩模20a的情况同样地例如形成于第2蒸镀掩模20b的有效区域22b的角落。对准标记29b在使用第2蒸镀掩模20b通过蒸镀法在基板91形成第2电极140的第2层140b的工序中,可以用于第2蒸镀掩模20b相对于基板91的位置对准。

[0309]

接着,对制造电子器件100的方法的一例进行说明。

[0310]

首先,如图3所示,准备形成有第1电极120的基板91。第1电极120例如通过下述方式形成:通过溅射法等在基板91上形成构成第1电极120的导电层后,通过光刻法等将导电层图案化,由此形成。

[0311]

接着,如图4所示,在第1电极120上形成通电层130。通电层130例如通过利用蒸镀法使有机材料等附着于基板91上或第1电极120上而形成,该蒸镀法使用了具有与通电层130对应的贯通孔的蒸镀掩模。

[0312]

接着,实施在通电层130上形成第2电极140的第2电极形成工序。例如,如图5所示,在通电层130上形成第2电极140的第1层140a。具体而言,第1层140a通过利用蒸镀法使金属等导电性材料附着于通电层130上而形成,该蒸镀法使用了具备第1蒸镀掩模20a的第1蒸镀掩模装置10a。

[0313]

接着,如图6所示,在通电层130上和第2电极140的第1层140a上形成第2电极140的第2层140b。具体而言,第2层140b通过利用蒸镀法使金属等导电性材料附着于通电层130上和第1层140a上而形成,该蒸镀法使用了具备第2蒸镀掩模20b的第2蒸镀掩模装置10b。这样,可以得到具备形成于基板91上的第1电极120、通电层130、第2电极140的第1层140a和第

2层140b的电子器件100。

[0314]

参照图16,对通过使用具备第1蒸镀掩模20a和第2蒸镀掩模20b的蒸镀掩模组形成第2电极140而能实现的效果进行说明。图16是示出通过将第1蒸镀掩模20a与第2蒸镀掩模20b重叠而得到的层积体21的图。在层积体21中,可以按照第1蒸镀掩模20a的第1对准标记29a与第2蒸镀掩模20b的第2对准标记29b重叠的方式使第1蒸镀掩模20a与第2蒸镀掩模20b重叠。此时,可以对第1蒸镀掩模20a和第2蒸镀掩模20b施加张力,也可以不施加张力。

[0315]

需要说明的是,将第1蒸镀掩模20a和第2蒸镀掩模20b之类的两个以上的蒸镀掩模20重叠的状态的图16的图也可以通过将各蒸镀掩模20的图像数据重叠而得到。例如,首先,使用拍摄装置,分别取得关于第1蒸镀掩模20a的第1贯通孔25a的轮廓和第2蒸镀掩模20b的第2贯通孔25b的轮廓的图像数据,接着,使用图像处理装置,将第1蒸镀掩模20a的图像数据与第2蒸镀掩模20b的图像数据重叠,由此可以制作图16这样的图。后述将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重叠的情况下也相同。

[0316]

图16中,第1蒸镀掩模20a的第1贯通孔25a用虚线表示,第2蒸镀掩模20b的第2贯通孔25b用实线表示。如图16所示,在将第1蒸镀掩模20a与第2蒸镀掩模20b重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b部分重叠。这意味着,利用穿过第1贯通孔25a的蒸镀材料在基板91形成的第2电极140的第1层140a与利用穿过第2贯通孔25b的蒸镀材料在基板91形成的第2电极140的第2层140b部分重叠。因此,与仅利用第1层140a构成第2电极140的情况相比,能够降低第2电极140的电阻。

[0317]

对第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b的重叠进行详细说明。如图16所示,在将第1蒸镀掩模20a与第2蒸镀掩模20b重合时,第1蒸镀掩模20a的掩模第1扩张区域27a与第2蒸镀掩模20b的第2贯通孔25b整体或部分重叠。如上所述,在第1蒸镀掩模20a的掩模第1扩张区域27a穿过并附着于基板91的蒸镀材料形成将相邻的两个元件110的第2电极140的电极第1基本区域141a连接的电极第1扩张区域142a。通过使第1蒸镀掩模20a的掩模第1扩张区域27a与第2蒸镀掩模20b的第2贯通孔25b重叠,能够在第2电极140的电极第1扩张区域142a上形成第2层140b。即,第2层140b能够与电极第1扩张区域142a重叠。由此,即使在电极第1扩张区域142a的尺寸和第2层140b的尺寸小于电极第1基本区域141a的尺寸的情况下,也能降低相邻的两个元件110的电极第1基本区域141a之间的电阻。另外,通过使电极第1扩张区域142a的尺寸和第2层140b的尺寸小于电极第1基本区域141a的尺寸,在第2方向d2上相邻的两个元件110之间的区域,光容易透过电子器件100。由此,能够提高电子器件100整体的透射率。

[0318]

如图16所示,在将第1蒸镀掩模20a与第2蒸镀掩模20b重合时,第2蒸镀掩模20b的第2贯通孔25b可以与第1蒸镀掩模20a的相邻的两个掩模第1基本区域26a以及与两个掩模第1基本区域26a连接的掩模第1扩张区域27a整体或部分重叠。即,第2蒸镀掩模20b的第2贯通孔25b从第1蒸镀掩模20a的相邻的两个掩模第1基本区域26a中的一者延伸至另一者。换言之,在将第1蒸镀掩模20a与第2蒸镀掩模20b重合的情况下,第1蒸镀掩模20a的相邻的两个掩模第1基本区域26a可以藉由第2蒸镀掩模20b的第2贯通孔25b而连接。这种情况下,与第2贯通孔25b对应形成的第2层140b能够重叠于与掩模第1基本区域26a对应形成的电极第1基本区域141a。

[0319]

接着,参照图17~图25,对使用蒸镀掩模组形成电子器件100的第2电极140的其他

示例进行说明。此处,对蒸镀掩模组包含第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c、通电层130包含第1通电层130a、第2通电层130b和第3通电层130c的示例进行说明。第1通电层130a、第2通电层130b和第3通电层130c例如为红色发光层、蓝色发光层和绿色发光层。

[0320]

两个以上的通电层130可以在基板91的面内方向沿不同的两个方向排列。图17是将形成有第1通电层130a、第2通电层130b和第3通电层130c的状态的基板91的一部分放大示出的图。两个以上的第1通电层130a可以在基板91的面内方向沿不同的两个方向排列。第2通电层130b和第3通电层130c也同样。需要说明的是,虽未图示,但在基板91与第1通电层130a、第2通电层130b和第3通电层130c之间形成有第1电极120。在图17所示的示例中,两个以上的第1通电层130a沿着第3方向d3和与第3方向d3交叉的第4方向d4排列。第3方向d3也可以为相对于第1方向d1呈45

°

的方向。另外,第4方向d4也可以为相对于第2方向d2呈45

°

的方向。两个以上的第2通电层130b也与第1通电层130a同样地沿着第3方向d3和与第3方向d3交叉的第4方向d4排列。两个以上的第3通电层130c沿着第1方向d1和第2方向d2排列。

[0321]

图18是示出图17所示的在第1通电层130a、第2通电层130b和第3通电层130c上形成有第2电极140的状态的基板91的俯视图。另外,图19是沿着图18的电子器件100的xix-xix线的截面图。另外,图20是沿着图18的电子器件100的xx-xx线的截面图。另外,图21是沿着图18的电子器件100的xxi-xxi线的截面图。如图18所示,电子器件100包含未设有第2电极140的非电极区域150。

[0322]

如图19和图21所示,第2电极140具有第1层140a、第2层140b和第3层140c。第1层140a是通过使用第1蒸镀掩模20a的蒸镀法形成的层。第1层140a可以在基板91的面内方向沿不同的两个方向排列。第2层140b是通过使用第2蒸镀掩模20b的蒸镀法形成的层。第2层140b可以在基板91的面内方向沿不同的两个方向排列。第3层140c是通过使用第3蒸镀掩模20c的蒸镀法形成的层。第3层140c可以在基板91的面内方向沿不同的两个方向排列。

[0323]

第1层140a至少具有与第1电极120和第1通电层130a重叠的电极第1基本区域141a。第1电极120、第1通电层130a和电极第1基本区域141a构成了电子器件100的第1元件110a。另外,第2层140b至少具有与第1电极120和第2通电层130b重叠的电极第2基本区域141b。第1电极120、第2通电层130b和电极第2基本区域141b构成了电子器件100的第2元件110b。另外,第3层140c至少具有与第1电极120和第3通电层130c重叠的电极第3基本区域141c。第1电极120、第3通电层130c和电极第3基本区域141c构成了电子器件100的第3元件110c。

[0324]

如图20所示,第1层140a可以包含按照将第1层140a的电极第1基本区域141a与第3层140c的电极第3基本区域141c电连接的方式从电极第1基本区域141a延伸出的电极第1扩张区域142a。电极第1扩张区域142a可以与电极第3基本区域141c部分重叠。电极第1扩张区域142a在与电极第1扩张区域142a从电极第1基本区域141a延伸出的方向正交的方向上具有小于电极第1基本区域141a和电极第3基本区域141c的尺寸。

[0325]

虽未图示,与第1层140a同样地,但第2层140b也可以包含按照将第2层140b的电极第2基本区域141b与第3层140c的电极第3基本区域141c电连接的方式从电极第2基本区域141b延伸出的电极第2扩张区域。电极第2扩张区域可以与电极第3基本区域141c部分重叠。电极第2扩张区域在与电极第2扩张区域从电极第2基本区域141b延伸出的方向正交的方向

上具有小于电极第2基本区域141b和电极第3基本区域141c的尺寸。

[0326]

另外,如图20和图21所示,第3层140c可以包含按照将第3层140c的电极第3基本区域141c与第1层140a的电极第1基本区域141a电连接的方式从电极第3基本区域141c延伸出的电极第3扩张区域142c。电极第3扩张区域142c可以与电极第1基本区域141a部分重叠。电极第3扩张区域142c在与电极第3扩张区域142c从电极第3基本区域141c延伸出的方向正交的方向上具有小于电极第1基本区域141a和电极第3基本区域141c的尺寸。

[0327]

虽未图示,但第3层140c可以包含按照将第3层140c的电极第3基本区域141c与第2层140b的电极第2基本区域141b电连接的方式从电极第3基本区域141c延伸出的电极第3扩张区域。电极第3扩张区域可以与电极第2基本区域141b部分重叠。与上述电极第3扩张区域142c同样地,该电极第3扩张区域也在与电极第3扩张区域从电极第3基本区域141c延伸出的方向正交的方向上具有小于电极第2基本区域141b和电极第3基本区域141c的尺寸。

[0328]

如图21所示,第1层140a可以包含按照将第2层140b的电极第2基本区域141b与第3层140c的电极第3基本区域141c电连接的方式延伸的电极第1辅助区域143a。电极第1辅助区域143a可以与电极第2基本区域141b和电极第3基本区域141c部分重叠。电极第1辅助区域143a可以不与电极第1基本区域141a和电极第1扩张区域142a连接。电极第1辅助区域143a在与电极第1辅助区域143a延伸的方向正交的方向上具有小于电极第2基本区域141b和电极第3基本区域141c的尺寸。

[0329]

虽未图示,与第1层140a同样地,第2层140b也可以包含按照将第1层140a的电极第1基本区域141a与第3层140c的电极第3基本区域141c电连接的方式延伸的电极第2辅助区域。电极第2辅助区域可以与电极第1基本区域141a和电极第3基本区域141c部分重叠。电极第2辅助区域可以不与电极第2基本区域141b和电极第2扩张区域142b连接。电极第2辅助区域在与电极第2辅助区域延伸的方向正交的方向上具有小于电极第1基本区域141a和电极第3基本区域141c的尺寸。

[0330]

接着,对为了形成上述的第2电极140的第1层140a、第2层140b和第3层140c而使用的第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c进行说明。

[0331]

图22是示出从第1面201侧观察时的第1蒸镀掩模20a的俯视图。如图22所示,第1蒸镀掩模20a具有包含沿不同的两个方向排列的区域的两个以上的第1贯通孔25a。两个以上的第1贯通孔25a至少包含沿不同的两个方向排列的两个以上的掩模第1基本区域26a。两个以上的第1贯通孔25a也可以包含沿不同的两个方向排列的两个以上的掩模第1扩张区域27a。另外,两个以上的第1贯通孔25a也可以包含沿不同的两个方向排列的两个以上的掩模第1辅助区域28a。

[0332]

掩模第1基本区域26a是构成上述第2电极140的第1层140a的电极第1基本区域141a的蒸镀材料主要穿过的区域。在图22所示的示例中,两个以上的掩模第1基本区域26a沿着第3方向d3和第4方向d4排列。

[0333]

掩模第1扩张区域27a是构成上述第2电极140的第1层140a的电极第1扩张区域142a的蒸镀材料主要穿过的区域。在图22所示的示例中,掩模第1扩张区域27a在相邻的两个掩模第1基本区域26a排列的第3方向d3上从掩模第1基本区域26a延伸出。

[0334]

掩模第1扩张区域27a在与掩模第1扩张区域27a从掩模第1基本区域26a延伸出的方向正交的方向上具有小于掩模第1基本区域26a的尺寸。在图22所示的示例中,掩模第1扩

张区域27a在与掩模第1扩张区域27a从掩模第1基本区域26a延伸出的方向即第3方向d3正交的第4方向d4上具有小于掩模第1基本区域26a的尺寸。在第4方向d4上,掩模第1扩张区域27a的尺寸w12可以为掩模第1基本区域26a的尺寸w11的0.9倍以下、可以为0.8倍以下、可以为0.7倍以下、可以为0.6倍以下、也可以为0.5倍以下。另外,在第4方向d4上,掩模第1扩张区域27a的尺寸w12可以为掩模第1基本区域26a的尺寸w11的0.05倍以上、可以为0.1倍以上、可以为0.2倍以上、可以为0.3倍以上、也可以为0.4倍以上。

[0335]

尺寸w12相对于尺寸w11的比例即w12/w11的范围可以由0.05、0.1、0.2、0.3、0.4构成的第1组、和/或0.9、0.8、0.7、0.6、0.5构成的第2组确定。w12/w11的范围可以由上述的第1组中包含的值中的任意一者与上述的第2组中包含的值中的任意一者的组合确定。例如,w12/w11可以为0.05以上0.9以下、可以为0.05以上0.8以下、可以为0.05以上0.7以下、可以为0.05以上0.6以下、可以为0.05以上0.5以下、可以为0.05以上0.4以下、可以为0.05以上0.3以下、可以为0.05以上0.2以下、可以为0.05以上0.1以下、可以为0.1以上0.9以下、可以为0.1以上0.8以下、可以为0.1以上0.7以下、可以为0.1以上0.6以下、可以为0.1以上0.5以下、可以为0.1以上0.4以下、可以为0.1以上0.3以下、可以为0.1以上0.2以下、可以为0.2以上0.9以下、可以为0.2以上0.8以下、可以为0.2以上0.7以下、可以为0.2以上0.6以下、可以为0.2以上0.5以下、可以为0.2以上0.4以下、可以为0.2以上0.3以下、可以为0.3以上0.9以下、可以为0.3以上0.8以下、可以为0.3以上0.7以下、可以为0.3以上0.6以下、可以为0.3以上0.5以下、可以为0.3以上0.4以下、可以为0.4以上0.9以下、可以为0.4以上0.8以下、可以为0.4以上0.7以下、可以为0.4以上0.6以下、可以为0.4以上0.5以下、可以为0.5以上0.9以下、可以为0.5以上0.8以下、可以为0.5以上0.7以下、可以为0.5以上0.6以下、可以为0.6以上0.9以下、可以为0.6以上0.8以下、可以为0.6以上0.7以下、可以为0.7以上0.9以下、可以为0.7以上0.8以下、也可以为0.8以上0.9以下。

[0336]

掩模第1辅助区域28a是构成上述第2电极140的第1层140a的电极第1辅助区域143a的蒸镀材料主要穿过的区域。在图22所示的示例中,掩模第1辅助区域28a在从掩模第1基本区域26a和掩模第1扩张区域27a离开的位置沿第3方向d3和第4方向d4排列。在图22所示的示例中,掩模第1辅助区域28a沿第3方向d3延伸。

[0337]

掩模第1辅助区域28a在与掩模第1辅助区域28a延伸的方向正交的方向上具有小于掩模第1基本区域26a的尺寸。在图22所示的示例中,掩模第1辅助区域28a在与掩模第1辅助区域28a延伸的方向即第3方向d3正交的第4方向d4上具有小于掩模第1基本区域26a的尺寸。在第4方向d4上,掩模第1辅助区域28a的尺寸w13可以为掩模第1基本区域26a的尺寸w11的0.9倍以下、可以为0.8倍以下、可以为0.7倍以下、可以为0.6倍以下、也可以为0.5倍以下。另外,在第4方向d4上,掩模第1辅助区域28a的尺寸w13可以为掩模第1基本区域26a的尺寸w11的0.05倍以上、可以为0.1倍以上、可以为0.2倍以上、可以为0.3倍以上、也可以为0.4倍以上。

[0338]

尺寸w13相对于尺寸w11的比例即w13/w11的范围可以由0.05、0.1、0.2、0.3、0.4构成的第1组、和/或0.9、0.8、0.7、0.6、0.5构成的第2组确定。w13/w11的范围可以由上述的第1组中包含的值中的任意一者与上述的第2组中包含的值中的任意一者的组合确定。例如,w13/w11可以为0.05以上0.9以下、可以为0.05以上0.8以下、可以为0.05以上0.7以下、可以为0.05以上0.6以下、可以为0.05以上0.5以下、可以为0.05以上0.4以下、可以为0.05以上

0.3以下、可以为0.05以上0.2以下、可以为0.05以上0.1以下、可以为0.1以上0.9以下、可以为0.1以上0.8以下、可以为0.1以上0.7以下、可以为0.1以上0.6以下、可以为0.1以上0.5以下、可以为0.1以上0.4以下、可以为0.1以上0.3以下、可以为0.1以上0.2以下、可以为0.2以上0.9以下、可以为0.2以上0.8以下、可以为0.2以上0.7以下、可以为0.2以上0.6以下、可以为0.2以上0.5以下、可以为0.2以上0.4以下、可以为0.2以上0.3以下、可以为0.3以上0.9以下、可以为0.3以上0.8以下、可以为0.3以上0.7以下、可以为0.3以上0.6以下、可以为0.3以上0.5以下、可以为0.3以上0.4以下、可以为0.4以上0.9以下、可以为0.4以上0.8以下、可以为0.4以上0.7以下、可以为0.4以上0.6以下、可以为0.4以上0.5以下、可以为0.5以上0.9以下、可以为0.5以上0.8以下、可以为0.5以上0.7以下、可以为0.5以上0.6以下、可以为0.6以上0.9以下、可以为0.6以上0.8以下、可以为0.6以上0.7以下、可以为0.7以上0.9以下、可以为0.7以上0.8以下、也可以为0.8以上0.9以下。

[0339]

图23是示出从第1面201侧观察时的第2蒸镀掩模20b的俯视图。如图23所示,第2蒸镀掩模20b具有包含沿不同的两个方向排列的区域的两个以上的第2贯通孔25b。两个以上的第2贯通孔25b至少包含沿不同的两个方向排列的两个以上的掩模第2基本区域26b。两个以上的第2贯通孔25b也可以包含沿不同的两个方向排列的两个以上的掩模第2扩张区域27b。另外,两个以上的第2贯通孔25b也可以包含沿不同的两个方向排列的两个以上的掩模第2辅助区域28b。

[0340]

掩模第2基本区域26b是构成上述第2电极140的第2层140b的电极第2基本区域141b的蒸镀材料主要穿过的区域。在图23所示的示例中,两个以上的掩模第2基本区域26b沿着第3方向d3和第4方向d4排列。

[0341]

掩模第2扩张区域27b是构成上述第2电极140的第2层140b的电极第2扩张区域142b的蒸镀材料主要穿过的区域。在图23所示的示例中,掩模第2扩张区域27b在相邻的两个掩模第2基本区域26b排列的第4方向d4上从掩模第2基本区域26b延伸出。

[0342]

与上述掩模第1扩张区域27a同样地,掩模第2扩张区域27b在与掩模第2扩张区域27b从掩模第2基本区域26b延伸出的方向正交的方向上具有小于掩模第2基本区域26b的尺寸。在图23所示的示例中,掩模第2扩张区域27b在与相邻的两个掩模第2基本区域26b排列的方向即第4方向d4正交的第3方向d3上具有小于掩模第2基本区域26b的尺寸。第3方向d3上的掩模第2扩张区域27b的尺寸w22与掩模第2基本区域26b的尺寸w21的关系和上述掩模第1扩张区域27a的尺寸w12与掩模第1基本区域26a的尺寸w11的关系相同,因此省略详细的说明。

[0343]

掩模第2辅助区域28b是构成上述第2电极140的第2层140b的电极第2辅助区域143b的蒸镀材料主要穿过的区域。在图23所示的示例中,两个以上的掩模第2辅助区域28b在从掩模第2基本区域26b和掩模第2扩张区域27b离开的位置沿着第3方向d3和第4方向d4排列。在图23所示的示例中,掩模第2辅助区域28b沿第4方向d4延伸。

[0344]

掩模第2辅助区域28b在与掩模第2辅助区域28b的延伸方向正交的方向上具有小于掩模第2基本区域26b的尺寸。在图23所示的示例中,掩模第2辅助区域28b在与掩模第2辅助区域28b延伸的方向即第4方向d4正交的第3方向d3上具有小于掩模第2基本区域26b的尺寸。第3方向d3上的掩模第2辅助区域28b的尺寸w23与掩模第2基本区域26b的尺寸w21的关系和上述掩模第1辅助区域28a的尺寸w13与掩模第1基本区域26a的尺寸w11的关系相同,因

此省略详细的说明。

[0345]

图24是示出从第1面201侧观察时的第3蒸镀掩模20c的俯视图。如图24所示,第3蒸镀掩模20c具有包含沿不同的两个方向排列的区域的两个以上的第3贯通孔25c。两个以上的第3贯通孔25c至少包含沿不同的两个方向排列的两个以上的掩模第3基本区域26c。两个以上的第3贯通孔25c也可以包含沿不同的两个方向排列的两个以上的掩模第3扩张区域27c。

[0346]

掩模第3基本区域26c是构成上述第2电极140的第3层140c的电极第3基本区域141c的蒸镀材料主要穿过的区域。在图24所示的示例中,两个以上的掩模第3基本区域26c沿着第1方向d1和第2方向d2排列。

[0347]

掩模第3扩张区域27c是构成上述第2电极140的第3层140c的电极第3扩张区域142c的蒸镀材料主要穿过的区域。掩模第3扩张区域27c可以在第1蒸镀掩模20a的掩模第1基本区域26a排列的第3方向d3上从掩模第3基本区域26c延伸出。另外,掩模第2扩张区域27b可以在第2蒸镀掩模20b的掩模第2基本区域26b排列的第4方向d4上从掩模第3基本区域26c延伸出。

[0348]

在与掩模第3扩张区域27c从掩模第3基本区域26c延伸出的方向正交的方向上,掩模第3扩张区域27c的尺寸w32小于掩模第3基本区域26c的尺寸w31。掩模第3扩张区域27c的尺寸w32与掩模第3基本区域26c的尺寸w31的关系和上述掩模第1扩张区域27a的尺寸w12与掩模第1基本区域26a的尺寸w11的关系相同,因此省略详细的说明。

[0349]

接着,对制造电子器件100的方法的一例进行说明。

[0350]

首先,准备形成有在第3方向d3和第4方向d4排列的两个以上的第1电极120的基板91。接着,如图17所示,在第1电极120上形成第1通电层130a、第2通电层130b和第3通电层130c。第1通电层130a例如通过利用蒸镀法使有机材料等附着于与第1通电层130a对应的第1电极120上而形成,该蒸镀法使用了具有与第1通电层130a对应的贯通孔的蒸镀掩模。第2通电层130b也可以通过利用蒸镀法使有机材料等附着于与第2通电层130b对应的第1电极120上而形成,该蒸镀法使用了具有与第2通电层130b对应的贯通孔的蒸镀掩模。第3通电层130c也可以通过利用蒸镀法使有机材料等附着于与第3通电层130c对应的第1电极120上而形成,该蒸镀法使用了具有与第3通电层130c对应的贯通孔的蒸镀掩模。

[0351]

接着,通过使用具备第1蒸镀掩模20a的第1蒸镀掩模装置10a的蒸镀法使金属等导电性材料附着于基板91上等,从而形成第2电极140的第1层140a。接着,通过使用具备第2蒸镀掩模20b的第2蒸镀掩模装置10b的蒸镀法使金属等导电性材料附着于基板91上等,从而形成第2电极140的第2层140b。接着,通过使用具备第3蒸镀掩模20c的第3蒸镀掩模装置10c的蒸镀法使金属等导电性材料附着于基板91上等,从而形成第2电极140的第3层140c。由此,如图18~图21所示,能够形成包含第1层140a、第2层140b和第3层140c的第2电极140。需要说明的是,形成第1层140a、第2层140b和第3层140c的顺序没有特别限定。例如,可以为第3层140c、第2层140b、第1层140a的顺序。

[0352]

参照图25,对通过使用具备第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c的蒸镀掩模组形成第2电极140而能实现的效果进行说明。图25是示出通过将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重叠而得到的层积体21的图。

[0353]

图25中,第1蒸镀掩模20a的第1贯通孔25a用点划线表示,第2蒸镀掩模20b的第2贯

通孔25b用虚线表示,第3蒸镀掩模20c的第3贯通孔25c用实线表示。如图25所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b或第3蒸镀掩模20c的第3贯通孔25c部分重叠。这意味着,利用通过第1贯通孔25a的蒸镀材料在基板91形成的第2电极140的第1层140a与利用通过第2贯通孔25b的蒸镀材料在基板91形成的第2电极140的第2层140b或利用通过第3贯通孔25c的蒸镀材料在基板91形成的第2电极140的第3层140c部分重叠。由此,能够将第1层140a与第2层140b或第3层140c电连接,能够容易稳定地控制第2电极140的电位。

[0354]

对第1蒸镀掩模20a的第1贯通孔25a、第2蒸镀掩模20b的第2贯通孔25b和第3蒸镀掩模20c的第3贯通孔25c的重叠进行详细说明。如图25所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的掩模第1扩张区域27a可以按照与第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式从掩模第1基本区域26a延伸出。由此,与掩模第1扩张区域27a对应形成的第1层140a的电极第1扩张区域142a能够部分重叠于与掩模第3基本区域26c对应形成的第3层140c的电极第3基本区域141c。另外,第2蒸镀掩模20b的掩模第2扩张区域27b可以按照与第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式从掩模第2基本区域26b延伸出。由此,第2层140b的电极第2扩张区域142b能够与第3层140c的电极第3基本区域141c部分重叠。另外,第3蒸镀掩模20c的掩模第3扩张区域27c可以按照与第1蒸镀掩模20a的掩模第1基本区域26a部分重叠的方式从掩模第3基本区域26c延伸出。由此,第3层140c的电极第3扩张区域142c能够与第1层140a的电极第1基本区域141a部分重叠。另外,第3蒸镀掩模20c的掩模第3扩张区域27c可以按照与第2蒸镀掩模20b的掩模第2基本区域26b部分重叠的方式从掩模第3基本区域26c延伸出。由此,第3层140c的电极第3扩张区域142c能够与第2层140b的电极第2基本区域141b部分重叠。

[0355]

另外,如图25所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的掩模第1辅助区域28a可以按照与第2蒸镀掩模20b的掩模第2基本区域26b和第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式在两者之间延伸。由此,与掩模第1辅助区域28a对应形成的第1层140a的电极第1辅助区域143a能够与第2层140b的电极第2基本区域141b和第3层140c的电极第3基本区域141c部分重叠。另外,第2蒸镀掩模20b的掩模第2辅助区域28b可以按照与第1蒸镀掩模20a的掩模第1基本区域26a和第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式在两者之间延伸。由此,与掩模第2辅助区域28b对应形成的第2层140b的电极第2辅助区域143b能够与第1层140a的电极第1基本区域141a和第3层140c的电极第3基本区域141c部分重叠。

[0356]

优选的是,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a藉由第2蒸镀掩模20b的第2贯通孔25b、或者藉由第3蒸镀掩模20c的第3贯通孔25c与其他的第1贯通孔25a连接。由此,能够介由第2层140b或第3层140c将第1层140a电连接至其他的第1层140a。另外,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a可以藉由第2蒸镀掩模20b的第2贯通孔25b和第3蒸镀掩模20c的第3贯通孔25c与其他的第1贯通孔25a连接。由此,能够介由第2层140b和第3层140c将第1层140a电连接至其他的第1层140a。

[0357]

根据图17~图25所示的实施方式,如图18所示,能够在包含第1通电层130a的第1元件110a与包含第2通电层130b的第2元件110b之间形成未设有第2电极140的非电极区域

150。另外,能够在包含第3通电层130c的两个第3元件110c之间形成未设有第2电极140的非电极区域150。由此,与在基板91的整个区域形成有第2电极140的情况相比,能够提高电子器件100中的光的透射率。

[0358]

另外,根据图17~图25所示的实施方式,第1元件110a的第1层140a的电极第1基本区域141a、第2元件110b的第2层140b的电极第2基本区域141b以及第3元件110c的第3层140c的电极第3基本区域141c藉由上述的扩张区域142a、142b、142c或电极辅助区域143a、143b等而相互电连接。由此,容易稳定地控制第2电极140的电位。

[0359]

另外,根据图17~图25所示的实施方式,通过使用不同的蒸镀掩模20的蒸镀法来形成第2电极140的第1层140a、第2层140b和第3层140c,因此能够独立地设定第1层140a、第2层140b和第3层140c的结构。例如,作为第1层140a的材料,能够使用与第2层140b的材料或第3层140c的材料不同的材料。另外,能够使第1层140a的厚度与第2层140b的厚度或第3层140c的厚度不同。由此,容易个别地控制各元件110a、110b、110c的特性。

[0360]

另外,根据图17~图25所示的实施方式,第1层140a与第2层140b或第3层140c能够部分重叠。两个层重叠的第2电极140的区域的电阻低于两个层构成的第2电极140的区域的电阻。两个层重叠的第2电极140的区域沿着通电层130的排列方向等周期性地存在。因此,与由一个导电层构成第2电极140的情况相比,能够降低基板91的面内方向的第2电极140的电阻。

[0361]

需要说明的是,在图17~图25所示的实施方式中,示出了掩模第1扩张区域27a从第1蒸镀掩模20a的第1贯通孔25a的掩模第1基本区域26a延伸出的示例,但不限定于此。例如如图26所示,第1蒸镀掩模20a的第1贯通孔25a也可以包含未连接有掩模第1扩张区域27a的掩模第1基本区域26a。同样地,例如如图27所示,第2蒸镀掩模20b的第2贯通孔25b也可以包含未连接有掩模第2扩张区域27b的掩模第2基本区域26b。同样地,例如如图28所示,第3蒸镀掩模20c的第3贯通孔25c也可以包含未连接有掩模第3扩张区域27c的掩模第3基本区域26c。

[0362]

如图26所示,在与掩模第1扩张区域27a从掩模第1基本区域26a延伸出的第3方向d3正交的方向上,掩模第1扩张区域27a的尺寸w12可以小于掩模第1基本区域26a的尺寸w11。尺寸w12与尺寸w11的关系和图22的示例的情况相同,因而省略说明。

[0363]

如图26所示,在与掩模第1辅助区域28a延伸的第3方向d3正交的方向上,掩模第1辅助区域28a的尺寸w13可以小于掩模第1基本区域26a的尺寸w11。尺寸w13与尺寸w11的关系和图22的示例的情况相同,因而省略说明。

[0364]

如图27所示,在与掩模第2扩张区域27b从掩模第2基本区域26b延伸出的第4方向d4正交的方向上,掩模第2扩张区域27b的尺寸w22可以小于掩模第2基本区域26b的尺寸w21。尺寸w22与尺寸w21的关系和图23的示例的情况相同,因而省略说明。

[0365]

如图27所示,在与掩模第2辅助区域28b延伸的第4方向d4正交的方向上,掩模第2辅助区域28b的尺寸w23可以小于掩模第2基本区域26b的尺寸w21。尺寸w23与尺寸w21的关系和图23的示例的情况相同,因而省略说明。

[0366]

如图28所示,在与掩模第3扩张区域27c从掩模第3基本区域26c延伸出的第3方向d3或第4方向d4正交的方向上,掩模第3扩张区域27c的尺寸w32可以小于掩模第3基本区域26c的尺寸w31。尺寸w32与尺寸w31的关系和图24的示例的情况相同,因而省略说明。

[0367]

图29是示出通过将图26的第1蒸镀掩模20a、图27第2蒸镀掩模20b和图28的第3蒸镀掩模20c重叠而得到的层积体21的图。根据图26~图29所示的实施方式,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合的情况下,如图29所示,在第3方向d3或第4方向d4上相邻的掩模第1基本区域26a与掩模第3基本区域26c之间、或者掩模第2基本区域26b与掩模第3基本区域26c之间,能够设置不存在蒸镀掩模20的贯通孔25的区域21v。由此,在第3方向d3或第4方向d4上相邻的第1元件110a与第3元件110c之间、或者第2元件110b与第3元件110c之间能够形成未设有第2电极140的非电极区域150。由此,能够提高电子器件100中的非电极区域150的比例,能够提高电子器件100中的光的透射率。

[0368]

在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合的情况下,可以按照第1蒸镀掩模20a的掩模第1扩张区域27a或第2蒸镀掩模20b的掩模第2扩张区域27b与第3蒸镀掩模20c的掩模第3扩张区域27c重叠的方式构成各蒸镀掩模20a、20b、20c。例如如图29所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合的情况下,两个以上的掩模第1扩张区域27a中的一部分掩模第1扩张区域27a与两个以上的掩模第3扩张区域27c中的一部分掩模第3扩张区域27c可以重叠。这种状态可以如下实现:例如如图26所示,第1蒸镀掩模20a的第1贯通孔25a包含在第3方向d3上的一侧从掩模第1基本区域26a延伸出的掩模第1扩张区域27a、与在第3方向d3上的另一侧从掩模第1基本区域26a延伸出的掩模第1扩张区域27a。根据图29所示的示例,在掩模第1扩张区域27a与掩模第3扩张区域27c重叠的部分,按照第2电极140的电极第1扩张区域142a与电极第3扩张区域142c重叠的方式形成第2电极140。由此,能够降低电极第1基本区域141a与电极第3基本区域141c之间的电阻。因此,如图29所示,即使在第3方向d3或第4方向d4上相邻的掩模第1基本区域26a与掩模第3基本区域26c之间、或者掩模第2基本区域26b与掩模第3基本区域26c之间设有不存在蒸镀掩模20的贯通孔25的区域21v的情况下,也能较低地维持第2电极140整体的电阻。

[0369]

在掩模第1扩张区域27a与掩模第3扩张区域27c重叠的部分,如图29所示,掩模第1扩张区域27a可以按照也与掩模第3基本区域26c部分重叠的方式延伸。另外,在掩模第1扩张区域27a与掩模第3扩张区域27c重叠的部分,掩模第3扩张区域27c可以按照也与掩模第1基本区域26a部分重叠的方式延伸。两个以上的蒸镀掩模20的贯通孔重叠时,对应形成的第2电极140的两个以上的层能够重叠。

[0370]

接着,参照图30~图35,对使用蒸镀掩模组形成电子器件100的第2电极140的其他示例进行说明。在图30~图35所示的实施方式中,对于可与图17~图25所示的实施方式同样构成的部分,使用与对图17~图25所示的实施方式中的对应部分使用的符号相同的符号,并省略重复的说明。

[0371]

图30是示出图17所示的在第1通电层130a、第2通电层130b和第3通电层130c上形成有第2电极140的状态的基板91的俯视图。另外,图31是沿着图30的电子器件100的xxx-xxx线的截面图。如图30所示,电子器件100包含未设有第2电极140的非电极区域150。如图31所示,第1层140a可以包含按照将第3层140c的电极第3基本区域141c与第1层140a的电极第1基本区域141a电连接的方式沿第1方向d1延伸的电极第1辅助区域143a。同样地,虽未图示,但第2层140b也可以包含按照将第3层140c的电极第3基本区域141c与第2层140b的电极第2基本区域141b电连接的方式沿第1方向d1延伸的电极第2辅助区域。

[0372]

图32是示出从第1面201侧观察时的第1蒸镀掩模20a的俯视图。如图32所示,第1蒸

镀掩模20a的掩模第1辅助区域28a沿第1方向d1延伸。如图32所示,掩模第1辅助区域28a可以与掩模第1基本区域26a连接。掩模第1辅助区域28a在掩模第1辅助区域28a延伸的方向即第1方向d1上具有大于掩模第1基本区域26a的尺寸。

[0373]

如图32所示,掩模与第1辅助区域28a延伸的方向即第1方向d1正交的第2方向d2上的掩模第1辅助区域28a的尺寸w13小于第2方向d2上的掩模第1基本区域26a的尺寸w11。掩模第1辅助区域28a的尺寸w13与掩模第1基本区域26a的尺寸w11的关系和上述图22所示的例中的掩模第1辅助区域28a的尺寸w13与掩模第1基本区域26a的尺寸w11的关系相同,因此省略详细的说明。

[0374]

图33是示出从第1面201侧观察时的第2蒸镀掩模20b的俯视图。如图33所示,第2蒸镀掩模20b的掩模第2辅助区域28b沿第1方向d1延伸。如图33所示,掩模第2辅助区域28b可以与掩模第2基本区域26b连接。掩模第2辅助区域28b在掩模第2辅助区域28b延伸的方向即第1方向d1上具有大于掩模第2基本区域26b的尺寸。

[0375]

如图33所示,与掩模第2辅助区域28b延伸的方向即第1方向d1正交的第2方向d2上的掩模第2辅助区域28b的尺寸w23小于第2方向d2上的掩模第2基本区域26b的尺寸w21。掩模第2辅助区域28b的尺寸w23与掩模第2基本区域26b的尺寸w21的关系和上述图23所示的例中的掩模第2辅助区域28b的尺寸w23与掩模第2基本区域26b的尺寸w21的关系相同,因此省略详细的说明。

[0376]

如图34所示,第3贯通孔25c至少包含掩模第3基本区域26c。如图34所示,第3贯通孔25c也可以不包含上述掩模第3扩张区域27c。虽未图示,但第3贯通孔25c也可以包含上述掩模第3扩张区域27c。

[0377]

图35是示出通过将图32的第1蒸镀掩模20a、图33的第2蒸镀掩模20b和图34的第3蒸镀掩模20c重叠而得到的层积体21的图。在图30~图35所示的实施方式中,将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b或第3蒸镀掩模20c的第3贯通孔25c也部分重叠。由此,能够将第1层140a与第2层140b或第3层140c电连接,能够容易稳定地控制第2电极140的电位。另外,第1层140a与第2层140b或第3层140c能够部分重叠。由此,能够降低基板91的面内方向的第2电极140的电阻。

[0378]

对第1蒸镀掩模20a的第1贯通孔25a、第2蒸镀掩模20b的第2贯通孔25b和第3蒸镀掩模20c的第3贯通孔25c的重叠进行详细说明。如图35所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的掩模第1辅助区域28a可以按照与第1方向d1上相邻的两个掩模第3基本区域26c部分重叠的方式沿第1方向d1延伸。由此,与掩模第1辅助区域28a对应形成的第1层140a的电极第1辅助区域143a能够部分重叠于与掩模第3基本区域26c对应形成的第3层140c的电极第3基本区域141c。另外,第2蒸镀掩模20b的掩模第2辅助区域28b可以按照与第1方向d1上相邻的两个掩模第3基本区域26c部分重叠的方式沿第1方向d1延伸。由此,与掩模第2辅助区域28b对应形成的第2层140b的电极第2辅助区域143b能够与第3层140c的电极第3基本区域141c部分重叠。

[0379]

另外,在图30~图35所示的实施方式中,如图30所示,在包含第1通电层130a的第1元件110a与包含第2通电层130b的第2元件110b之间也能形成未设有第2电极140的非电极区域150。另外,在包含第3通电层130c的两个第3元件110c之间能够形成未设有第2电极140

的非电极区域150。由此,与在基板91的整个区域形成有第2电极140的情况相比,能够提高电子器件100中的光的透射率。

[0380]

接着,参照图36~图42b,对使用蒸镀掩模组形成电子器件100的第2电极140的其他示例进行说明。在图36~图42b所示的实施方式中,对于可与图17~图25所示的实施方式同样构成的部分,使用与对图17~图25所示的实施方式中的对应部分使用的符号相同的符号,并省略重复的说明。

[0381]

图36是将形成有第1通电层130a、第2通电层130b和第3通电层130c的状态的基板91的一部分放大示出的图。在图36所示的例中,两个以上的第1通电层130a沿第1方向d1排列。两个以上的第2通电层130b沿第1方向d1排列。两个以上的第3通电层130c沿第1方向d1排列。另外,如图36所示,在第1方向d1排列的第1通电层130a的列、在第1方向d1排列的第2通电层130b的列以及在第1方向d1排列的第3通电层130c的列沿着与第1方向d1交叉的第2方向d1依次排列。因此,两个以上的第1通电层130a沿第1方向d1和第2方向d2排列。第2通电层130b和第3通电层130c也同样。第2方向d2可以是与第1方向d1正交的方向。

[0382]

图37是示出图36所示的在第1通电层130a、第2通电层130b和第3通电层130c上形成有第2电极140的状态的基板91的俯视图。另外,图38是沿着图37的电子器件100的xxxviii-xxxviii线的截面图。如图37所示,电子器件100包含未设有第2电极140的非电极区域150。

[0383]

如图38所示,第1层140a包含与第1电极120和第1通电层130a重叠的电极第1基本区域141a。第2层140b包含与第1电极120和第2通电层130b重叠的电极第2基本区域141b。第3层140c包含与第1电极120和第3通电层130c重叠的电极第3基本区域141c。

[0384]

如图38所示,第1层140a进一步包含按照将电极第1基本区域141a与电极第2基本区域141b电连接的方式从电极第1基本区域141a延伸出的电极第1扩张区域142a。第2层140b进一步包含按照将电极第2基本区域141b与电极第3基本区域141c电连接的方式从电极第2基本区域141b延伸出的电极第2扩张区域142b。第3层140c进一步包含按照将电极第3基本区域141c与电极第1基本区域141a电连接的方式从电极第3基本区域141c延伸出的电极第3扩张区域142c。

[0385]

接着,对为了形成图37和图38所示的第2电极140的第1层140a、第2层140b和第3层140c而使用的第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c进行说明。

[0386]

图39是示出从第1面201侧观察时的第1蒸镀掩模20a的俯视图。如图39所示,第1蒸镀掩模20a具有沿第1方向d1和第2方向d2排列的两个以上的第1贯通孔25a。两个以上的第1贯通孔25a包含沿第1方向d1和第2方向d2排列的两个以上的掩模第1基本区域26a。两个以上的第1贯通孔25a可以包含沿第1方向d1和第2方向d2排列的两个以上的掩模第1扩张区域27a。掩模第1扩张区域27a在相邻的两个掩模第1基本区域26a排列的第2方向d2上从掩模第1基本区域26a延伸出。

[0387]

在与掩模第1扩张区域27a从掩模第1基本区域26a延伸出的第2方向d2正交的方向上,掩模第1扩张区域27a的尺寸w12可以小于掩模第1基本区域26a的尺寸w11。尺寸w12与尺寸w11的关系和图22的示例的情况相同,因而省略说明。

[0388]

图40是示出从第1面201侧观察时的第2蒸镀掩模20b的俯视图。如图40所示,第2蒸镀掩模20b具有沿第1方向d1和第2方向d2排列的两个以上的第2贯通孔25b。两个以上的第2

贯通孔25b包含沿第1方向d1和第2方向d2排列的两个以上的掩模第2基本区域26b。两个以上的第2贯通孔25b可以包含沿第1方向d1和第2方向d2排列的两个以上的掩模第2扩张区域27b。掩模第2扩张区域27b可以在相邻的两个掩模第2基本区域26b排列的第2方向d2上从掩模第2基本区域26b延伸出。

[0389]

在与掩模第2扩张区域27b从掩模第2基本区域26b延伸出的第2方向d2正交的方向上,掩模第2扩张区域27b的尺寸w22可以小于掩模第2基本区域26b的尺寸w21。尺寸w22与尺寸w21的关系和图23的示例的情况相同,因而省略说明。

[0390]

图41是示出从第1面201侧观察时的第3蒸镀掩模20c的俯视图。如图41所示,第3蒸镀掩模20c具有沿第1方向d1和第2方向d2排列的两个以上的第3贯通孔25c。两个以上的第3贯通孔25c包含沿第1方向d1和第2方向d2排列的两个以上的掩模第3基本区域26c。两个以上的第3贯通孔25c可以包含沿第1方向d1和第2方向d2排列的两个以上的掩模第3扩张区域27c。掩模第3扩张区域27c在相邻的两个掩模第3基本区域26c排列的第2方向d2上从掩模第3基本区域26c延伸出。

[0391]

在与掩模第3扩张区域27c从掩模第3基本区域26c延伸出的第2方向d2正交的方向上,掩模第3扩张区域27c的尺寸w32可以小于掩模第3基本区域26c的尺寸w31。尺寸w32与尺寸w31的关系和图24的示例的情况相同,因而省略说明。

[0392]

图42a是示出将图39的第1蒸镀掩模20a、图40的第2蒸镀掩模20b和图41的第3蒸镀掩模20c重叠而得到的层积体21的图。图42b是在更宽的范围示出图42a的层积体21的图。在图36~图42b所示的实施方式中,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b或第3蒸镀掩模20c的第3贯通孔25c也部分重叠。由此,能够将第1层140a与第2层140b或第3层140c电连接,容易稳定地控制第2电极140的电位。另外,第1层140a与第2层140b或第3层140c能够部分重叠。由此,能够降低基板91的面内方向的第2电极140的电阻。

[0393]

对第1蒸镀掩模20a的第1贯通孔25a、第2蒸镀掩模20b的第2贯通孔25b和第3蒸镀掩模20c的第3贯通孔25c的重叠进行详细说明。如图42a所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的掩模第1扩张区域27a可以按照与第2蒸镀掩模20b的掩模第2基本区域26b部分重叠的方式从掩模第1基本区域26a延伸出。由此,与掩模第1扩张区域27a对应形成的第1层140a的电极第1扩张区域142a能够部分重叠于与掩模第2基本区域26b对应形成的第2层140b的电极第2基本区域141b。另外,第2蒸镀掩模20b的掩模第2扩张区域27b可以按照与第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式从掩模第2基本区域26b延伸出。由此,第2层140b的电极第2扩张区域142b能够与第3层140c的电极第3基本区域141c部分重叠。另外,第3蒸镀掩模20c的掩模第3扩张区域27c可以按照与第1蒸镀掩模20a的掩模第1基本区域26a部分重叠的方式从掩模第3基本区域26c延伸出。由此,第3层140c的电极第3扩张区域142c能够与第1层140a的电极第1基本区域141a部分重叠。

[0394]

接着,参照图43~图48b,对使用蒸镀掩模组形成电子器件100的第2电极140的其他示例进行说明。在图43~图48b所示的实施方式中,对于可与图36~图42b所示的实施方式同样构成的部分,使用与对图36~图42b所示的实施方式中的对应部分使用的符号相同的符号,并省略重复的说明。

[0395]

图43是示出图36所示的在第1通电层130a、第2通电层130b和第3通电层130c上形成有第2电极140的状态的基板91的俯视图。另外,图44是沿着图43的电子器件100的xxxxiv-xxxxiv线的截面图。如图43所示,电子器件100包含未设有第2电极140的非电极区域150。

[0396]

如图44所示,第1层140a可以包含:在第2方向d2上朝向第2层140b从电极第1基本区域141a延伸出的电极第1扩张区域142a;和在第2方向d2上朝向第3层140c从电极第1基本区域141a延伸出的电极第1扩张区域142a。第2层140b可以包含:在第2方向d2上朝向第1层140a从电极第2基本区域141b延伸出的电极第2扩张区域142b;和在第2方向d2上朝向第3层140c从电极第2基本区域141b延伸出的电极第2扩张区域142b。第3层140c可以包含:在第2方向d2上朝向第1层140a从电极第3基本区域141c延伸出的电极第3扩张区域142c;和在第2方向d2上朝向第2层140b从电极第3基本区域141c延伸出的电极第3扩张区域142c。

[0397]

接着,对为了形成图43和图44所示的第2电极140的第1层140a、第2层140b和第3层140c而使用的第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c进行说明。

[0398]

图45是示出从第1面201侧观察时的第1蒸镀掩模20a的俯视图。如图45所示,第1贯通孔25a可以包含:向第2方向d2的一侧从掩模第1基本区域26a延伸出的掩模第1扩张区域27a;和向第2方向d2的另一侧从掩模第1基本区域26a延伸出的掩模第1扩张区域27a。

[0399]

在与掩模第1扩张区域27a从掩模第1基本区域26a延伸出的第2方向d2正交的方向上,掩模第1扩张区域27a的尺寸w12可以小于掩模第1基本区域26a的尺寸w11。尺寸w12与尺寸w11的关系和图22的示例的情况相同,因而省略说明。

[0400]

图46是示出从第1面201侧观察时的第2蒸镀掩模20b的俯视图。如图46所示,第2贯通孔25b可以包含:向第2方向d2的一侧从掩模第2基本区域26b延伸出的掩模第2扩张区域27b;和向第2方向d2的另一侧从掩模第2基本区域26b延伸出的掩模第2扩张区域27b。

[0401]

在与掩模第2扩张区域27b从掩模第2基本区域26b延伸出的第2方向d2正交的方向上,掩模第2扩张区域27b的尺寸w22可以小于掩模第2基本区域26b的尺寸w21。尺寸w22与尺寸w21的关系和图23的示例的情况相同,因而省略说明。

[0402]

图47是示出从第1面201侧观察时的第3蒸镀掩模20c的俯视图。如图47所示,第3贯通孔25c可以包含:向第2方向d2的一侧从掩模第3基本区域26c延伸出的掩模第3扩张区域27c;和向第2方向d2的另一侧从掩模第3基本区域26c延伸出的掩模第3扩张区域27c。

[0403]

在与掩模第3扩张区域27c从掩模第3基本区域26c延伸出的第2方向d2正交的方向上,掩模第3扩张区域27c的尺寸w32可以小于掩模第3基本区域26c的尺寸w31。尺寸w32与尺寸w31的关系和图24的示例的情况相同,因而省略说明。

[0404]

图48a是示出将图45的第1蒸镀掩模20a、图46的第2蒸镀掩模20b和图47的第3蒸镀掩模20c重叠而得到的层积体21的图。图48b是在更宽的范围示出图48a的层积体21的图。在图43~图48b所示的实施方式中,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b或第3蒸镀掩模20c的第3贯通孔25c也部分重叠。由此,能够将第1层140a与第2层140b或第3层140c电连接,容易稳定地控制第2电极140的电位。另外,第1层140a与第2层140b或第3层140c能够部分重叠。由此,能够降低基板91的面内方向的第2电极140的电阻。

[0405]

对第1蒸镀掩模20a的第1贯通孔25a、第2蒸镀掩模20b的第2贯通孔25b和第3蒸镀

掩模20c的第3贯通孔25c的重叠进行详细说明。如图48a所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第2方向d2上的从掩模第1基本区域26a的一侧延伸出的掩模第1扩张区域27a可以与第2方向d2上的从掩模第2基本区域26b的另一侧延伸出的掩模第2扩张区域27b重叠。由此,第2方向d2上的从电极第1基本区域141a的一侧延伸出的电极第1扩张区域142a能够与第2方向d2上的从电极第2基本区域141b的另一侧延伸出的电极第2扩张区域142b重叠。另外,第2方向d2上的从掩模第1基本区域26a的另一侧延伸出的掩模第1扩张区域27a可以与第2方向d2上的从掩模第3基本区域26c的一侧延伸出的掩模第3扩张区域27c重叠。由此,第2方向d2上的从电极第1基本区域141a的另一侧延伸出的电极第1扩张区域142a能够与第2方向d2上的从电极第3基本区域141c的一侧延伸出的电极第3扩张区域142c重叠。另外,第2方向d2上的从掩模第2基本区域26b的一侧延伸出的掩模第2扩张区域27b可以与第2方向d2上的从掩模第3基本区域26c的另一侧延伸出的掩模第3扩张区域27c重叠。由此,第2方向d2上的从电极第2基本区域141b的一侧延伸出的电极第2扩张区域142b能够与第2方向d2上的从电极第3基本区域141c的另一侧延伸出的电极第3扩张区域142c重叠。

[0406]

接着,参照图49~图54b,对使用蒸镀掩模组形成电子器件100的第2电极140的其他示例进行说明。在图49~图54b所示的实施方式中,对于可与图36~图42b所示的实施方式同样构成的部分,使用与对图36~图42b所示的实施方式中的对应部分使用的符号相同的符号,并省略重复的说明。

[0407]

图49是示出图36所示的在第1通电层130a、第2通电层130b和第3通电层130c上形成有第2电极140的状态的基板91的俯视图。另外,图50是图49的电子器件100的沿在第3方向d3延伸的xxxxx-xxxxx线的截面图。如图49所示,电子器件100包含未设有第2电极140的非电极区域150。

[0408]

如图50所示,第1层140a可以包含在与第1方向d1和第2方向d2交叉的第3方向d3上朝向第2层140b的电极第2基本区域141b从电极第1基本区域141a延伸出的电极第1扩张区域142a。第2层140b可以包含在第3方向d3上朝向第3层140c的电极第3基本区域141c从电极第2基本区域141b延伸出的电极第2扩张区域142b。第3层140c可以包含在第3方向d3上朝向第1层140a的电极第1基本区域141a从电极第3基本区域141c延伸出的电极第3扩张区域142c。第3方向d3可以是与第1方向d1和第2方向d2成45

°

的方向。

[0409]

接着,对为了形成图49和图50所示的第2电极140的第1层140a、第2层140b和第3层140c而使用的第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c进行说明。

[0410]

图51是示出从第1面201侧观察时的第1蒸镀掩模20a的俯视图。如图51所示,第1贯通孔25a可以包含在第3方向d3上从掩模第1基本区域26a延伸出的掩模第1扩张区域27a。在与掩模第1扩张区域27a从掩模第1扩张区域27a延伸出的第3方向d3正交的方向上,掩模第1扩张区域27a的尺寸w12可以小于掩模第1基本区域26a的尺寸w11。尺寸w12与尺寸w11的关系和图22的示例的情况相同,因而省略说明。

[0411]

图52是示出从第1面201侧观察时的第2蒸镀掩模20b的俯视图。如图52所示,第2贯通孔25b可以包含在第3方向d3上从掩模第2基本区域26b延伸出的掩模第2扩张区域27b。在与掩模第2扩张区域27b从掩模第2基本区域26b延伸出的第3方向d3正交的方向上,掩模第2扩张区域27b的尺寸w22可以小于掩模第2基本区域26b的尺寸w21。尺寸w22与尺寸w21的关

系和图23的示例的情况相同,因而省略说明。

[0412]

图53是示出从第1面201侧观察时的第3蒸镀掩模20c的俯视图。如图53所示,第3贯通孔25c可以包含在第3方向d3上从掩模第3基本区域26c延伸出的掩模第3扩张区域27c。在与掩模第3扩张区域27c从掩模第3基本区域26c延伸出的第3方向d3正交的方向上,掩模第3扩张区域27c的尺寸w32可以小于掩模第3基本区域26c的尺寸w31。尺寸w32与尺寸w31的关系和图24的示例的情况相同,因而省略说明。

[0413]

图54a是示出将图51的第1蒸镀掩模20a、图52的第2蒸镀掩模20b和图53的第3蒸镀掩模20c重叠而得到的层积体21的图。图54b是在更宽的范围示出图54a的层积体21的图。在图49~图54b所示的实施方式中,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b或第3蒸镀掩模20c的第3贯通孔25c也部分重叠。由此,能够将第1层140a与第2层140b或第3层140c电连接,容易稳定地控制第2电极140的电位。另外,第1层140a与第2层140b或第3层140c能够部分重叠。由此,能够降低基板91的面内方向的第2电极140的电阻。

[0414]

对第1蒸镀掩模20a的第1贯通孔25a、第2蒸镀掩模20b的第2贯通孔25b和第3蒸镀掩模20c的第3贯通孔25c的重叠进行详细说明。如图54a所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的掩模第1扩张区域27a可以按照与第2蒸镀掩模20b的掩模第2基本区域26b部分重叠的方式从掩模第1基本区域26a在第3方向d3延伸出。由此,第1层140a的电极第1扩张区域142a能够与第2层140b的电极第2基本区域141b部分重叠。另外,第2蒸镀掩模20b的掩模第2扩张区域27b可以按照与第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式从掩模第2基本区域26b在第3方向d3延伸出。由此,第2层140b的电极第2扩张区域142b能够与第3层140c的电极第3基本区域141c部分重叠。另外,第3蒸镀掩模20c的掩模第3扩张区域27c可以按照与第1蒸镀掩模20a的掩模第1基本区域26a部分重叠的方式从掩模第3基本区域26c在第3方向d3延伸出。由此,第3层140c的电极第3扩张区域142c能够与第1层140a的电极第1基本区域141a部分重叠。

[0415]

接着,参照图55~图60,对使用蒸镀掩模组形成电子器件100的第2电极140的其他示例进行说明。在图55~图60所示的实施方式中,对于可与图17~图25所示的实施方式同样构成的部分,使用与对图17~图25所示的实施方式中的对应部分使用的符号相同的符号,并省略重复的说明。

[0416]

图55是将形成有第1通电层130a、第2通电层130b和第3通电层130c的状态的基板91的一部分放大示出的图。在图55所示的例中,第1通电层130a、第2通电层130b和第3通电层130c分别沿第1方向d1和第2方向d2排列。第1通电层130a和第2通电层130b在第2方向d2上交替排列。另外,在第2方向d2上交替排列的第1通电层130a和第2通电层130b的列沿第1方向d1排列。另外,第3通电层130c在第1方向d1上相邻的两个第1通电层130a之间以及第1方向d1上相邻的两个第2通电层130b之间沿第2方向d2排列。第3通电层130c可以按照沿第1方向d1观察时一个通电层130与第1通电层130a和第2通电层130b重叠的方式沿第2方向d2延伸。

[0417]

图56是示出图55所示的在第1通电层130a、第2通电层130b和第3通电层130c上形成有第2电极140的状态的基板91的俯视图。电子器件100包含未设有第2电极140的非电极区域150。

[0418]

接着,对为了形成图56所示的第2电极140的第1层140a、第2层140b和第3层140c而使用的第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c进行说明。

[0419]

图57是示出从第1面201侧观察时的第1蒸镀掩模20a的俯视图。如图57所示,第1蒸镀掩模20a可以包含沿第1方向d1和第2方向d2排列的两个以上的掩模第1基本区域26a和两个以上的掩模第1辅助区域28a。掩模第1辅助区域28a在与掩模第1辅助区域28a延伸的第1方向d1正交的第2方向d2上具有小于掩模第1基本区域26a的尺寸w11的尺寸w13。尺寸w13与尺寸w11的关系和图22的示例的情况相同,因而省略说明。掩模第1辅助区域28a可以不与掩模第1基本区域26a连接。

[0420]

图58是示出从第1面201侧观察时的第2蒸镀掩模20b的俯视图。如图58所示,第2蒸镀掩模20b可以包含沿第1方向d1和第2方向d2排列的两个以上的掩模第2基本区域26b和两个以上的掩模第2辅助区域28b。掩模第2辅助区域28b在与掩模第2辅助区域28b延伸的第1方向d1正交的第2方向d2上具有小于掩模第2基本区域26b的尺寸w21的尺寸w23。尺寸w23与尺寸w21的关系和图23的示例的情况相同,因而省略说明。掩模第2辅助区域28b可以不与掩模第2基本区域26b连接。

[0421]

图59是示出从第1面201侧观察时的第3蒸镀掩模20c的俯视图。如图59所示,第3蒸镀掩模20c可以包含在第1方向d1上排列、并沿第2方向d2延伸的两个以上的第3贯通孔25c。

[0422]

图60是示出将图57的第1蒸镀掩模20a、图58的第2蒸镀掩模20b和图59的第3蒸镀掩模20c重叠而得到的层积体21的图。在图55~图60所示的实施方式中,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b或第3蒸镀掩模20c的第3贯通孔25c也部分重叠。由此,能够将第1层140a与第2层140b或第3层140c电连接,容易稳定地控制第2电极140的电位。另外,第1层140a与第2层140b或第3层140c能够部分重叠。由此,能够降低基板91的面内方向的第2电极140的电阻。

[0423]

对第1蒸镀掩模20a的第1贯通孔25a、第2蒸镀掩模20b的第2贯通孔25b和第3蒸镀掩模20c的第3贯通孔25c的重叠进行详细说明。如图60所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的掩模第1辅助区域28a可以按照与第1方向d1上相邻的两个掩模第2基本区域26b部分重叠的方式在两者之间延伸。由此,第1层140a的电极第1辅助区域143a能够与第1方向d1上相邻的两个电极第2基本区域141b部分重叠。另外,第2蒸镀掩模20b的掩模第2辅助区域28b可以按照与第1方向d1上相邻的两个掩模第1基本区域26a部分重叠的方式在两者之间延伸。由此,第2层140b的电极第2辅助区域143b能够与第1方向d1上相邻的两个电极第1基本区域141a部分重叠。

[0424]

另外,如图60所示,第3蒸镀掩模20c的第3贯通孔25c可以按照与第2方向d2上交替排列的掩模第1辅助区域28a和掩模第2辅助区域28b重叠的方式在第2方向d2上延伸。由此,第3层140c能够与第2方向d2上交替排列的电极第1辅助区域143a和电极第2辅助区域143b重叠。

[0425]

接着,参照图61~图66,对使用蒸镀掩模组形成电子器件100的第2电极140的其他示例进行说明。在图61~图66所示的实施方式中,对于可与图17~图25所示的实施方式同样构成的部分,使用与对图17~图25所示的实施方式中的对应部分使用的符号相同的符号,并省略重复的说明。

[0426]

图61是将形成有第1通电层130a、第2通电层130b和第3通电层130c的状态的基板91的一部分放大示出的图。在图61所示的例中,第1通电层130a、第2通电层130b和第3通电层130c分别沿第1方向d1和第2方向d2排列。第1方向d1上的第1通电层130a的位置相对于第2通电层130b错开第1方向d1上的第1通电层130a的排列周期的一半距离。第2方向d2上的第1通电层130a的位置相对于第2通电层130b错开第2方向d2上的第1通电层130a的排列周期的一半距离。第3通电层130c位于第1方向d1上相邻的两个第1通电层130a之间、第2方向d2上相邻的两个第1通电层130a之间、第1方向d1上相邻的两个第2通电层130b之间以及第2方向d2上相邻的两个第2通电层130b之间。

[0427]

图62是示出图61所示的在第1通电层130a、第2通电层130b和第3通电层130c上形成有第2电极140的状态的基板91的俯视图。电子器件100包含未设有第2电极140的非电极区域150。

[0428]

接着,对为了形成图62所示的第2电极140的第1层140a、第2层140b和第3层140c而使用的第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c进行说明。

[0429]

图63是示出从第1面201侧观察时的第1蒸镀掩模20a的俯视图。如图63所示,第1蒸镀掩模20a包含沿第1方向d1和第2方向d2排列的两个以上的掩模第1基本区域26a。第1蒸镀掩模20a可以包含:向第1方向d1的一侧从掩模第1基本区域26a延伸出的掩模第1扩张区域27a;和向第1方向d1的另一侧从掩模第1基本区域26a延伸出的掩模第1扩张区域27a。另外,第1蒸镀掩模20a可以包含:向第2方向d2的一侧从掩模第1基本区域26a延伸出的掩模第1扩张区域27a;和向第2方向d2的另一侧从掩模第1基本区域26a延伸出的掩模第1扩张区域27a。

[0430]

在与掩模第1扩张区域27a从掩模第1基本区域26a延伸出的第1方向d1或第2方向d2正交的方向上,掩模第1扩张区域27a的尺寸w12可以小于掩模第1基本区域26a的尺寸w11。尺寸w12与尺寸w11的关系和图22的示例的情况相同,因而省略说明。

[0431]

如图63所示,第1蒸镀掩模20a的第1贯通孔25a可以包含未连接有掩模第1扩张区域27a的掩模第1基本区域26a。例如,未连接有掩模第1扩张区域27a的掩模第1基本区域26a与连接有掩模第1扩张区域27a的掩模第1基本区域26a可以在第1方向d1和第2方向d2上交替排列。

[0432]

图64是示出从第1面201侧观察时的第2蒸镀掩模20b的俯视图。如图64所示,第2蒸镀掩模20b包含沿第1方向d1和第2方向d2排列的两个以上的掩模第2基本区域26b。第2蒸镀掩模20b可以包含:向与第1方向d1和第2方向d2交叉的第3方向d3的一侧从掩模第2基本区域26b延伸出的掩模第2扩张区域27b;和向第3方向d3的另一侧从掩模第2基本区域26b延伸出的掩模第2扩张区域27b。第3方向d3可以为与第1方向d1和第2方向d2成45

°

的方向。

[0433]

在与掩模第2扩张区域27b从掩模第2基本区域26b延伸出的第3方向d3正交的方向上,掩模第2扩张区域27b的尺寸w22可以小于掩模第2基本区域26b的尺寸w21_1。尺寸w22与尺寸w21_1的关系和图23的例中的尺寸w22与尺寸w21的关系相同,因而省略说明。

[0434]

如图64所示,第2蒸镀掩模20b的第2贯通孔25b可以包含未连接有掩模第2扩张区域27b的掩模第2基本区域26b。例如,未连接有掩模第2扩张区域27b的掩模第2基本区域26b与连接有掩模第2扩张区域27b的掩模第2基本区域26b可以在第1方向d1和第2方向d2上交替排列。

[0435]

在与掩模第2辅助区域28b延伸的第1方向d1或第2方向d2正交的方向上,掩模第2辅助区域28b的尺寸w23可以小于掩模第2基本区域26b的尺寸w21_2。尺寸w23与尺寸w21_2的关系和图23的例中的尺寸w23与尺寸w21的关系相同,因而省略说明。

[0436]

如图64所示,第2蒸镀掩模20b的第2贯通孔25b可以包含在第1方向d1或第2方向d2上延伸的两个以上的掩模第2辅助区域28b。掩模第2辅助区域28b可以不与掩模第2基本区域26b连接。

[0437]

图65是示出从第1面201侧观察时的第3蒸镀掩模20c的俯视图。如图65所示,第3蒸镀掩模20c包含沿第3方向d3和第4方向d4排列的两个以上的掩模第3基本区域26c。第3蒸镀掩模20c可以包含位于第3方向d3上相邻的两个掩模第3基本区域26c之间、并沿与第3方向d3正交的第4方向d4上延伸的两个以上的掩模第3辅助区域28c。另外,第3蒸镀掩模20c可以包含位于第4方向d4上相邻的两个掩模第3基本区域26c之间、并沿第3方向d3延伸的两个以上的掩模第3辅助区域28c。

[0438]

在与掩模第3辅助区域28c延伸的第3方向d3或第4方向d4正交的方向上,掩模第3辅助区域28c的尺寸w33可以小于掩模第3基本区域26c的尺寸w31。尺寸w33与尺寸w31的关系和图22的例中的尺寸w13与尺寸w11的关系相同,因而省略说明。

[0439]

图66是示出将图63的第1蒸镀掩模20a、图64的第2蒸镀掩模20b和图65的第3蒸镀掩模20c重叠而得到的层积体21的图。在图61~图66所示的实施方式中,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b或第3蒸镀掩模20c的第3贯通孔25c也部分重叠。由此,能够将第1层140a与第2层140b或第3层140c电连接,容易稳定地控制第2电极140的电位。另外,第1层140a与第2层140b或第3层140c能够部分重叠。由此,能够降低基板91的面内方向的第2电极140的电阻。

[0440]

对第1蒸镀掩模20a的第1贯通孔25a、第2蒸镀掩模20b的第2贯通孔25b和第3蒸镀掩模20c的第3贯通孔25c的重叠进行详细说明。如图66所示,在将第1蒸镀掩模20a、第2蒸镀掩模20b和第3蒸镀掩模20c重合时,第1蒸镀掩模20a的掩模第1扩张区域27a可以按照与第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式从掩模第1基本区域26a在第1方向d1或第2方向d2延伸出。由此,第1层140a的电极第1扩张区域142a能够与第3层140c的电极第3基本区域141c部分重叠。

[0441]

另外,如图66所示,第2蒸镀掩模20b的掩模第2扩张区域27b可以按照与第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式从掩模第2基本区域26b在第3方向d3延伸出。由此,第2层140b的电极第2扩张区域142b能够与第3层140c的电极第3基本区域141c部分重叠。另外,第2蒸镀掩模20b的掩模第2辅助区域28b可以按照与第1蒸镀掩模20a的掩模第1基本区域26a和第3蒸镀掩模20c的掩模第3基本区域26c部分重叠的方式在两者之间沿第1方向d1或第2方向d2延伸。由此,第2层140b的电极第2辅助区域143b能够与第1层140a的电极第1基本区域141a和第3层140c的电极第3基本区域141c部分重叠。

[0442]

另外,如图66所示,第3蒸镀掩模20c的掩模第3辅助区域28c可以按照与第1蒸镀掩模20a的掩模第1基本区域26a和第2蒸镀掩模20b的掩模第2基本区域26b部分重叠的方式在两者之间沿第3方向d3或第4方向d4延伸。由此,第3层140c的电极第3辅助区域143c能够与第1层140a的电极第1基本区域141a和第2层140b的电极第2基本区域141b部分重叠。

[0443]

接着,参照图67~图70,对使用蒸镀掩模组形成电子器件100的第2电极140的其他示例进行说明。在图67~图70所示的实施方式中,对于可与图17~图25所示的实施方式同样构成的部分,使用与对图17~图25所示的实施方式中的对应部分使用的符号相同的符号,并省略重复的说明。

[0444]

图67是示出图17所示的在第1通电层130a、第2通电层130b和第3通电层130c上形成有第2电极140的状态的基板91的俯视图。

[0445]

接着,对为了形成图67所示的第2电极140的第1层140a、第2层140b和第3层140c而使用的蒸镀掩模组进行说明。在图17~图25所示的实施方式中,对使用三个蒸镀掩模的示例进行了说明。本方式中,对使用两个蒸镀掩模的示例进行说明。本方式的蒸镀掩模组包含第1蒸镀掩模20a和第2蒸镀掩模20b。

[0446]

图68是示出从第1面201侧观察时的第1蒸镀掩模20a的俯视图。如图68所示,第1蒸镀掩模20a可以包含沿第1方向d1和第2方向d2排列的两个以上的掩模第1基本区域26a和两个以上的掩模第1辅助区域28a。在与掩模第1辅助区域28a延伸的第1方向d1正交的方向上,掩模第1辅助区域28a的尺寸w13可以小于掩模第1基本区域26a的尺寸w11。尺寸w13与尺寸w11的关系和图22的示例的情况相同,因而省略说明。掩模第1辅助区域28a可以不与掩模第1基本区域26a连接。

[0447]

如图68所示,在第2方向d2上相邻的两个掩模第1基本区域26a之间,两个掩模第1辅助区域28a可以排列于第1方向d1。如图67和图68所示,与掩模第1基本区域26a对应形成的电极第1基本区域141a可以与第1方向d1上相邻的第1通电层130a和第2通电层130b两者重叠。

[0448]

图69是示出从第1面201侧观察时的第2蒸镀掩模20b的俯视图。如图69所示,第2蒸镀掩模20b可以包含沿第1方向d1和第2方向d2排列的两个以上的掩模第2基本区域26b。如图67和图69所示,与掩模第2基本区域26b对应形成的电极第2基本区域141b可以与第3通电层130c重叠。

[0449]

如图69所示,第2蒸镀掩模20b可以包含:向第2方向d2的一侧从掩模第2基本区域26b延伸出的掩模第2扩张区域27b;和向第2方向d2的另一侧从掩模第2基本区域26b延伸出的掩模第2扩张区域27b。在与掩模第2扩张区域27b从掩模第2基本区域26b延伸出的第2方向d2正交的方向上,掩模第2扩张区域27b的尺寸w22可以小于掩模第2基本区域26b的尺寸w21_1。尺寸w22与尺寸w21_1的关系和图23的例中的尺寸w22与尺寸w21的关系相同,因而省略说明。

[0450]

如图69所示,第2蒸镀掩模20b可以包含沿第1方向d1和第2方向d2排列的两个以上的掩模第3基本区域26c。在与掩模第2辅助区域28b延伸的第1方向d1正交的方向上,掩模第2辅助区域28b的尺寸w23可以小于掩模第2基本区域26b的尺寸w21_2。尺寸w23与尺寸w21_2的关系和图23的例中的尺寸w23与尺寸w21的关系相同,因而省略说明。掩模第2辅助区域28b可以不与掩模第1辅助区域28a连接。

[0451]

图70是示出将图68的第1蒸镀掩模20a和图69的第2蒸镀掩模20b重叠而得到的层积体21的图。在图67~图70所示的实施方式中,在将第1蒸镀掩模20a和第2蒸镀掩模20b重合时,第1蒸镀掩模20a的第1贯通孔25a与第2蒸镀掩模20b的第2贯通孔25b也部分重叠。由此,能够将第1层140a与第2层140b电连接,容易稳定地控制第2电极140的电位。另外,第1层

140a与第2层140b能够部分重叠。由此,能够降低基板91的面内方向的第2电极140的电阻。

[0452]

对第1蒸镀掩模20a的第1贯通孔25a和第2蒸镀掩模20b的第2贯通孔25b的重叠进行详细说明。如图70所示,在将第1蒸镀掩模20a和第2蒸镀掩模20b重合时,第1蒸镀掩模20a的掩模第1辅助区域28a可以按照与第1方向d1上相邻的两个掩模第2基本区域26b部分重叠的方式沿第1方向d1延伸。由此,与掩模第1辅助区域28a对应形成的第1层140a的电极第1辅助区域143a能够与第2层140b的电极第2基本区域141b部分重叠。

[0453]

如图70所示,第2蒸镀掩模20b的掩模第2扩张区域27b可以按照与第1面201的掩模第1基本区域26a部分重叠的方式从掩模第2基本区域26b在第2方向d2延伸出。由此,第2层140b的电极第2扩张区域142b能够与第1层140a的电极第1基本区域141a部分重叠。另外,第2蒸镀掩模20b的掩模第2辅助区域28b可以按照与第1方向d1上相邻的两个掩模第1基本区域26a部分重叠的方式沿第1方向d1延伸。由此,电极第2辅助区域143b能够与第1方向d1上相邻的两个电极第1基本区域141a部分重叠。

[0454]

参照图71,对第1蒸镀掩模20a的第1贯通孔25a的形状的一例进行说明。图71所示的第1贯通孔25a除了角部的形状外与图13所示的第1贯通孔25a相同。

[0455]

如图71所示,第1贯通孔25a的掩模第1基本区域26a的角可以包含弯曲的轮廓。角是指构成第1贯通孔25a的轮廓的两条直线相交的部分。虽未图示,但上述各方式的第1贯通孔25a的掩模第1基本区域26a的角也可以包含弯曲的轮廓。另外,虽未图示,但上述各方式的掩模第1扩张区域27a、掩模第1辅助区域28a等其他区域的角也可以包含弯曲的轮廓。另外,虽未图示,但上述各方式的第2蒸镀掩模20b的第2贯通孔25b的区域的角和第3蒸镀掩模20c的第3贯通孔25c的区域的角也可以包含弯曲的轮廓。

[0456]

接着,参照图72,对电子器件100的构成的一例进行说明。电子器件100为有机el显示装置的情况下,元件110作为像素发挥功能。电子器件100包括:包含作为像素发挥功能的元件110的显示区域105。显示区域105可以包含第1显示区域106和第2显示区域107。

[0457]

第1显示区域106的面积可以小于第2显示区域107的面积。第1显示区域106可以包含未设有第2电极140的非电极区域150。由此,与在第1显示区域106的整个区域形成有第2电极140的情况相比,能够提高电子器件100中的光的透射率。通过使用上述的蒸镀掩模组,能够形成第1显示区域106的第2电极140。

[0458]

与第1显示区域106同样地,第2显示区域107可以包含未设有第2电极140的非电极区域150。这种情况下,通过使用上述的蒸镀掩模组,能够形成第2显示区域107的第2电极140。用于形成第2显示区域107的第2电极140的蒸镀掩模20的贯通孔25的形状和排列可以与用于形成第1显示区域106的第2电极140的蒸镀掩模20的贯通孔25的形状和排列相同,也可以不同。

[0459]

一片蒸镀掩模20可以包含:用于形成第1显示区域106的第2电极140的贯通孔25、以及用于形成第2显示区域107的第2电极140的贯通孔25。

[0460]

第2显示区域107可以不包含未设有第2电极140的非电极区域150。换言之,可以在第2显示区域107的整个区域形成有第2电极140。这样,在电子器件100形成非电极区域150而提高光透射率的技术可以应用于电子器件100的一部分区域而非整体。

[0461]

参照图73,对电子器件100的构成的一例进行说明。

[0462]

图72中,在俯视图中,示出了第1显示区域106与第2显示区域107之间的边界由直

线构成的示例。但是,不限定于此,也可以如图73所示那样,在俯视图中,第1显示区域106与第2显示区域107之间的边界可以包含曲线。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1