用于制造包括两个半导体管芯的器件的方法及其器件与流程

本公开的实施例涉及一种用于制造包括两个半导体管芯的器件的方法以及由此获得的器件。此外,本公开的实施例涉及芯片级封装(csp)器件,其包括微机电系统(mems)管芯(例如mems传感器)和集成电子组件的半导体管芯(例如专用集成电路(asic))。

背景技术:

1、众所周知,集成mems器件的管芯在一侧(通常是顶侧)由通常由另一管芯制成的帽保护。此外,它们通常与包含用于控制和/或预处理由mems器件(例如asic)提供的信号和数据的电子电路的管芯相关联,以便形成mems器件。因此,在下文中,将参考由mems管芯及其asic形成的系统,而不失一般性。

2、在这里描述的mems器件中,mems管芯及其帽与asic集成管芯堆叠,并且由具有焊盘栅格阵列(lga)外部耦合的有机衬底承载。

3、例如,堆叠布置允许减小系统的面积并且允许其在便携式和可佩戴的电子器件和系统中使用。

4、在具有小尺寸的电子系统和设备中(例如,在智能手表,耳机等中)使用更多mems器件的期望要求mems器件在面积和厚度方面具有更小尺寸。

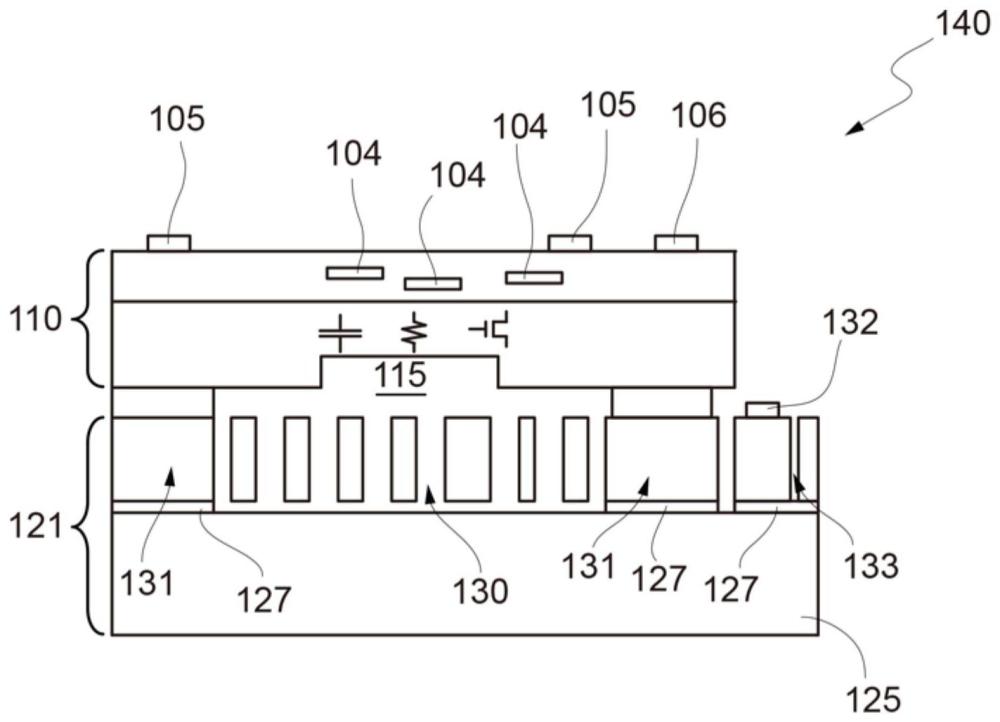

5、例如,文献it102013902204294(对应于美国专利9,327,964)描述了一种用于制造管芯组件的方法,该方法使用集成asic的管芯作为mems管芯的帽,从而节省管芯。

6、其他专利(例如美国专利9,527,727)教导了其他解决方案,其教导了使用贯通开口将mems管芯堆叠在帽上和asic管芯上。

7、然而,使用贯通开口是昂贵的,并且这些解决方案不允许将系统的所有部件集成在同一封装中,例如在csp器件中。

技术实现思路

1、用于制造微机电设备的工艺可以被概括为包括:将半导体的第一晶片结合到第二晶片,所述第一晶片集成电子元件;减薄第一晶片;将所述第一晶片结合到第三晶片,所述第三晶片包括图案化结构;减薄所述第三晶片;去除所述第二晶片以获得具有由所述第一晶片形成的主表面的复合晶片;通过内部电耦合结构电耦合所述第一晶片和所述第三晶片;在所述主表面上形成外部连接区域;以及形成封装件,所述封装件封装所述第一晶片,所述第三晶片和所述内部电耦合结构并且部分地围绕所述外部连接区域,所述外部连接区域部分地从所述封装件突出。

2、第一晶片可以是asic晶片,第三晶片可以是mems晶片。第二晶片可以是半导体或玻璃。第二晶片可以是玻璃的,并且去除第二晶片包括通过施加激光来分离第二晶片。该工艺还可以包括:在将第一晶片结合到第二晶片之前,在第二晶片中形成第一凹部和所述第二凹部,并在第一晶片的主表面上形成接触区域,并且将第一晶片结合到第二晶片包括:在第一凹部和所述第二凹部处形成具有第一结合层开口的结合层,并将第二晶片的第一凹部和所述第二凹部以及第一结合层开口布置在第一晶片的接触区域处;去除第二晶片包括减薄第二晶片直至到达第一凹部和所述第二凹部,从而形成贯通凹部;以及形成外部连接区域包括在第一结合层开口中形成凸块。

3、该工艺可以进一步包括,在将第一晶片结合到第二晶片之前,在第二晶片中形成第三凹部;以及将所述第一晶片结合到所述第二晶片还包括在所述第三凹部处形成第二结合层开口;在去除所述第二晶片的步骤之后,去除所述第三凹部下方的所述本体的一部分,从而在所述本体中形成贯通开口;以及电耦合所述第一晶片和所述第三晶片包括形成耦合线,所述耦合线在所述第一晶片的所述主表面上的接触区域与在所述第三晶片上在所述贯通开口下方延伸的接触区域之间延伸。

4、外部连接区域可以是凸块并且可以形成lga接口。内部电耦合结构可以是在形成于第一晶片的主表面上的外部接触焊盘和形成于第三晶片上的另外的接触焊盘之间延伸的结合线。

5、该工艺还可以包括在将第一晶片结合到第三晶片之前在第一晶片中形成腔体。第三晶片可以包括面对第一晶片的第三接触焊盘,该工艺进一步包括,在去除第二晶片的步骤之后,选择性地去除第三接触焊盘上方的主体的一部分,其中电耦合第一晶片和第三晶片包括形成穿过主体的被去除部分的耦合线。

6、该工艺可以包括在电耦合第一和第三晶片,形成外部连接区域和形成封装的步骤之前或之后分割复合晶片。

7、一个器件可以概括为包括:半导体集成电子元件的第一管芯;半导体的第二管芯,其结合到所述第一管芯并形成图案化结构,所述第一管芯具有主表面;内部电耦合结构,其将所述第一管芯的所述主表面电耦合到所述第二管芯;所述第一管芯的主表面上的外部连接区域;以及封装件,其封装所述第一管芯、所述第二管芯和所述内部电耦合结构并且部分地围绕所述外部连接区域,所述外部连接区域从所述封装件部分地突出。

8、封装件可以覆盖第一管芯的主表面并且可以与第一管芯的主表面接触。该器件还可以包括叠加在第一管芯的主表面上的结合层,使得封装覆盖结合层并与结合层接触。结合层可以具有贯通开口,并且外部连接区域可以穿过贯通开口。

技术特征:

1.一种用于制造微机电设备的方法,包括:

2.根据权利要求1所述的方法,其中所述第一晶片是专用集成电路晶片,并且所述第三晶片是微机电系统晶片。

3.根据权利要求1所述的方法,其中所述第二晶片由半导体材料或玻璃制成。

4.根据权利要求1所述的方法,其中所述第二晶片是玻璃的,并且去除所述第二晶片包括通过施加激光来分离所述第二晶片。

5.根据权利要求1所述的方法,进一步包括,在将所述第一晶片结合到所述第二晶片之前,在所述第二晶片中形成第一凹部和第二凹部,并且在所述第一晶片的所述主表面上形成接触区域,其中:

6.根据权利要求1所述的方法,还包括在将所述第一晶片结合到所述第二晶片之前,在所述第二晶片中形成第三凹部,其中:

7.根据权利要求1所述的方法,其中所述外部连接区域是凸块并且形成焊盘栅格阵列接口。

8.根据权利要求1所述的方法,其中所述内部电耦合结构是在形成于所述第一晶片的所述主表面上的外部接触焊盘与形成于所述第三晶片上的其它接触焊盘之间延伸的结合线。

9.根据权利要求1所述的方法,还包括在将所述第一晶片结合到所述第三晶片之前在所述第一晶片中形成腔体。

10.根据权利要求1所述的方法,其中所述第三晶片包括面对所述第一晶片的第三接触焊盘,所述方法还包括在去除所述第二晶片的步骤之后,选择性地去除所述第三接触焊盘上方的所述主体的一部分,其中电耦合所述第一晶片和所述第三晶片包括形成穿过所述主体的所去除部分的耦合线。

11.根据权利要求1所述的方法,还包括在电耦合所述第一晶片和第三晶片、形成外部连接区域和形成封装的步骤之前或之后分割复合晶片。

12.一种器件,包括:

13.根据权利要求12所述的器件,其中所述封装件覆盖所述第一管芯的所述主表面并且与所述第一管芯的所述主表面接触。

14.根据权利要求12所述的器件,还包括叠加在所述第一管芯的所述主表面上的结合层,其中所述封装件覆盖所述结合层并且与所述结合层接触。

15.根据权利要求14所述的器件,其中所述结合层具有贯通开口,并且所述外部连接区域穿过所述贯通开口。

16.一种mems器件,包括:

17.根据权利要求16所述的mems器件,进一步包括第一凹部、第二凹部和第三凹部。

18.根据权利要求17所述的mems器件,进一步包括并入所述第三凹部的一部分的贯通开口。

19.根据权利要求16所述的mems器件,其中所述钝化层包括嵌入式金属化。

20.根据权利要求16所述的mems器件,进一步包括所述第一接触焊盘上的外部连接区域,所述外部连接区域从所述器件部分地突出。

技术总结

一种用于制造包括两个半导体管芯的器件的器件和方法。该器件由第一管芯和第二管芯形成。第一管芯由半导体材料制成并集成电子元件。第二管芯具有主表面,形成图案化结构,并结合到第一管芯。内部电耦合结构将第一管芯的主表面电耦合到第二管芯。外部连接区域在第一管芯的主表面上延伸。封装件封装第一管芯、第二管芯和内部电耦合结构并且部分地围绕外部连接区域,外部连接区域部分地从封装件突出。

技术研发人员:M·A·肖,L·科索,M·加拉瓦利亚,G·阿勒加托

受保护的技术使用者:意法半导体股份有限公司

技术研发日:

技术公布日:2024/5/6

- 还没有人留言评论。精彩留言会获得点赞!