具有嵌入式存储器模块的集成电路的制作方法

1.本公开涉及一种用于在集成电路中的多个嵌入式存储器上的扫描移位操作期间保持稳定性的系统和方法。

背景技术:

2.集成电路(ic)可以包括嵌入式存储器。在一些情况下,具体地在需要较大存储器容量的情况下,存储器可以分成分布在整个ic上的多个较小存储器模块。这可以使功耗降低。然而,使用多个存储器模块确实需要针对每一存储器地址使用更多边界逻辑,例如测试多路复用器。在扫描移位操作中,ic的正常工作模式被暂停,并且ic中的多个触发器作为长移位寄存器连接。这使得能使用单个输入引脚将串行输入测试模式加载到由触发器形成的扫描链。将结果从扫描链移出并将其与预期结果进行比较,以验证ic是否正常工作。当在具有多个存储器模块的ic中执行此扫描移位操作时,与正常工作模式相比,较大量的边界逻辑可能会使切换速率更高。这可能会导致较大的ir降并且可能在扫描移位操作期间产生不正确的结果,除非扫描移位操作减速以防止发生这一情况。可以使用各种技术来减少这一ir降效应。可以使用可替换测试模式来减少在扫描移位操作期间触发器同时切换的次数。可以通过在扫描移位操作期间关断触发器输出来修改ic的设计,以使由触发器输出驱动的电路元件不会发生任何变化。扫描链中的触发器可以被设计成具有用于功能和扫描连接的单独输出引脚。然而,此类解决方案可能需要额外硬件或可能降低ic的性能且可能影响扫描测试定时路径的功能。

技术实现要素:

3.本公开大体上涉及一种集成电路,其包括多个存储器模块和内建自测(bist)控制器,其中所述bist控制器和存储器模块被布置和配置成减少在扫描移位操作期间所述存储器模块中单元的切换。

4.根据第一方面,提供一种集成电路,包括多个存储器模块和内建自测(bist)控制器,

5.所述bist控制器包括:

6.多个bist多路复用器,其可由bist控制输入和扫描启用输入在多个bist输入中的对应一个与逻辑零之间选择,使得当所述bist控制输入启用而所述扫描启用输入未启用时,所述多个bist多路复用器中的每一个输出对应bist输入的值,否则输出所述逻辑零;以及

7.逻辑电路,其被布置成在bist模式输入启用而所述扫描启用输入未启用时启用第一bist模式输出,并且在所述bist模式输入启用或所述扫描启用输入启用时启用第二bist模式输出,

8.每一存储器模块包括:

9.存储器;

10.第一多路复用器,其具有可由所述第二bist模式输出选择的第一输入和第二输入,使得当所述第二bist模式输出启用时,第一多路复用器将在所述第一输入处接收到的所述多个bist多路复用器中的对应一个的输出传递到所述存储器,否则将功能输入传递到所述存储器;以及

11.第二多路复用器,其具有可由所述第一bist模式输出选择的第一输入和第二输入,使得当所述第一bist模式输出启用时,所述第二多路复用器将在所述第二输入处接收到的所述存储器的输出传递到bist输出,否则将逻辑零从所述第一输入传递到所述bist输出。

12.使用存储器bist控制器能防止存储器边界逻辑在扫描移位操作期间切换,进而可以减少或避免由ir电压降引起的功率问题。在预烧扫描测试期间,可以停用所述扫描启用输入以允许存储器逻辑尽可能多地切换。

13.bist控制器布置的优点在于:由于组件数量的少量增加,扫描移位操作期间的切换次数减少了,这可能会给整个ic增加最少的成本或不增加其成本。

14.所述集成电路可以包括反相器和第一“与”门,所述反相器具有连接到所述扫描启用输入的输入,并且所述第一“与”门具有连接到所述反相器的输出的第一输入和连接到所述bist控制输入的第二输入,所述第一“与”门的输出连接到所述多个bist多路复用器中的每一个的选择输入。

15.所述逻辑电路可以包括第二“与”门,其中所述bist模式输入和所述反相器的所述输出连接到所述第二“与”门的输入,所述“与”门的输出提供所述第一bist模式输出。

16.所述逻辑电路可以包括“或”门,所述扫描启用输入和所述bist模式输入连接到所述“或”门的输入,所述“或”门的输出提供所述第二bist模式输出。

17.根据第二方面,提供一种根据第一方面操作集成电路的方法,所述方法包括通过以下方式对所述存储器模块执行扫描移位操作:

18.启用所述扫描启用输入、所述bist控制输入和所述bist模式输入;

19.向所述bist输入提供输入信号;并且

20.从每一存储器模块的所述bist输出接收输出信号。

21.与所述第一方面有关的其它特征也可以根据所述第二方面应用于所述集成电路。

22.本发明的这些以及其它方面将通过下文所描述的实施例显而易见,并且将参考下文所描述的实施例阐明本发明的这些以及其它方面。

附图说明

23.将参考图式仅借助于例子描述实施例,在附图中:

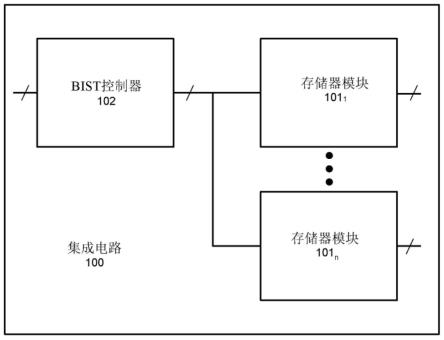

24.图1是具有bist控制器和多个存储器模块的集成电路的示意图;

25.图2是示例bist控制器的示意图;

26.图3是示例存储器模块的示意图;

27.图4是在常规扫描移位操作期间的存储器边界的一系列波形的曲线图;

28.图5是使用示例bist控制器的在扫描移位周期内的存储器边界的一系列波形的曲线图;

29.图6是常规多存储器ic的随装置电压而变的ir降的实例数的曲线图;

30.图7是结合示例bist控制器的多存储器ic的随装置电压而变的ir降的实例数的曲线图;并且

31.图8是示出操作本文所公开的示例ic的示例方法的示意流程图。

32.应注意,图是图解说明且未按比例绘制。为在图式中清楚和方便起见,这些图的各部分的相对尺寸和比例已通过在大小上放大或缩小而示出。相同的附图标记一般用于指代修改的和不同的实施例中的相应或类似特征。

具体实施方式

33.图1示出具有多个存储器模块101

1-n

的示例集成电路(ic)100。为清楚起见而未在图1中示出的其它组件也可以存在于ic 100中。存储器模块101

1-n

中的每一个在内建自测操作期间的操作由bist控制器102控制,所述bist控制器102向每一存储器模块101

1-n

提供信号以停用正常操作且实际上使其在bist控制器102的控制下操作。

34.图2示出示例bist控制器102的另外细节。bist控制器102包括:用于启用扫描移位操作的扫描启用输入106;用于启用bist操作的bist控制输入105;用于确定待采用的bist模式的bist模式输入109;以及用于n个多路复用器103

1-n

中的每一个的bist输入104

1-n

。每一多路复用器103

1-n

包括一对输入,可通过选择输入115

1-n

在多个bist输入104

1-n

中的对应一个与逻辑零之间选择所述一对输入。选择哪一输入通过输出116

1-n

是由关于bist控制输入105和扫描启用输入106的值的组合确定的。向反相器111提供扫描启用输入106,向第一“与”门112提供所述反相器111的输出。向bist多路复用器103

1-n

的选择输入115

1-n

中的每一个提供第一“与”门的输出。如果启用了bist控制输入105而没有启用扫描启用输入106,则进而控制每一多路复用器103

1-n

被控制以使对应bist输入104

1-n

通过。否则多路复用器103

1-n

输出逻辑零。因此,启用扫描启用输入106用以禁止bist输入104

1-n

通过多路复用器103

1-n

。

35.向逻辑电路107提供扫描启用输入106和bist模式输入109,所述逻辑电路107输出第一bist模式输出108和第二bist模式输出110。逻辑电路107包括第二“与”门113和“或”门114。将bist模式输入109和由反相器111提供的反相后扫描启用输入106输入到第二“与”门113中,所述第二“与”门113的输出提供第一bist模式输出108。向“或”门114提供扫描启用输入106和bist模式输入109,所述“或”门114的输出提供第二bist模式输出110。

36.当需要进行预烧扫描测试时,停用扫描启用输入106以使存储器模块尽可能多地切换,从而在较高温度和高电压条件下加速ic的预烧。bist控制器102可以因此另外包括逻辑(图2中未示出),所述逻辑将预烧扫描测试模式与扫描启用输入组合起来,使得仅在预烧模式不起作用时才启用扫描启用输入106处的输入。

37.图3示出示例存储器模块101

x

,其表示图1所示的n个存储器模块101

1-n

中的任一个,即其中x是1到n的任何数字。存储器模块包括具有输入211和输出210的存储器201。第一多路复用器202具有第一输入203和第二输入204。第一输入203由bist多路复用器103

1-n

的输出116

1-n

中的一个提供。第二输入204是功能输入,其用于在正常操作下(即当不执行bist操作时)向存储器201提供输入。第一多路复用器202在第二bist模式输出110的控制下操作。如果被启用,则第二bist模式输出110会使第一多路复用器202选择bist输入203,否则第一多路复用器202选择功能输入204。

38.存储器模块另外包括同样具有第一输入207和第二输入208的第二多路复用器206。第二多路复用器206的输入207、208由第一bist模式输出108选择。如果被启用,则第一bist模式输出108会使第二多路复用器206选择存储器输出210以提供到存储器模块101

x

的bist输出211

x

。否则,第二多路复用器206将选择第二输入208并将逻辑零提供到bist输出211x。存储器模块101x包括功能输出212x,其在正常操作期间(即当不执行bist操作时)提供来自存储器201的输出。

39.图4示出具有多个存储器模块的常规ic的,当存储器模块处于扫描模式时,移位周期期间的存储器边界的各种波形。可以看出,在移位周期401、402期间,芯片选择、写入启用、地址输入、数据输入和位掩码都进行了多次切换,这可能会导致不利的ir降。

40.图5示出在扫描移位操作期间结合如本文所述的bist控制器和存储器模块的集成电路的类似的一系列波形。在移位周期501、502中的每一个中,芯片选择、写入启用、地址输入、数据输入和位掩码都保持稳定,从而导致ir降减少。

41.图6和7示出本文所公开的类型的bist控制器和存储器模块的效应,示出电压降的实例数的曲线图,即当电压下降时装置中的单元数随电压降值而变。在每一情况下,曲线图示出为两个区。在第一区601、701中,单元满足工作电压降的限制要求,即在这些例子中所述电压降高达100mv。在第二区602、702中,电压降超出所述限制,这可能会导致单元不能正常工作或在错误状态下工作。对于常规ic(图6),最高电压降为约200mv。对于具有如本文所公开的bist控制器和存储器模块的ic,最高ir降实际上为约128mv,减少了70mv以上,只对在bist控制器和存储器模块中使用的电路系统进行了微小改动。

42.图8示出操作本文中所描述的ic的示例方法,其中对存储器模块执行扫描移位操作。在第一步骤801,启用扫描启用输入、bist控制输入和bist模式输入。在第二步骤802,向bist输入提供输入信号。在第三步骤803,从每一存储器模块的bist输出接收输出信号。可以同时进行这些步骤中的每一个,且不一定要按图8所给出的特定次序。

43.通过阅读本公开,技术人员将明白其它变化和修改。此类变化和修改可以涉及在存储器系统的领域中已知的并且可以代替或附加于本文所描述的特征而使用的等效物和其它特征。

44.尽管所附权利要求书是针对特定特征组合的,但是应理解,本发明的公开内容的范围还包括本文中明确地或隐含地公开的任何新颖特征或任何新颖特征组合或所述新颖特征的任何概括,而不管所述新颖特征是否涉及与当前在任何权利要求中要求保护的本发明相同的发明或所述新颖特征是否缓和与本发明所缓和的技术问题相同的任一或全部技术问题。

45.在单独的实施例的上下文中描述的特征也可以在单个实施例中以组合形式提供。相反,为了简洁起见,在单个实施例的上下文中描述的各种特征也可以单独地或以任何合适的子组合形式提供。申请人特此提醒,在审查本技术或由此衍生的任何另外的申请期间,可以针对此类特征和/或此类特征的组合而制定新的权利要求。

46.为完整性起见,还规定术语“包括”不排除其它元件或步骤,术语“一”或“一个”不排除多个,单个处理器或其它单元可以满足在权利要求中所述的若干构件的功能,并且权利要求中的附图标记不应解释为限制权利要求的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1