小间距集成刀刃临时结合微结构的制作方法

小间距集成刀刃临时结合微结构

1.【相关申请的交叉引用】

2.本技术要求2019年8月29日提交且标题为“small pitch integrated knife edge temporary bonding microstructures”的美国临时专利申请号62/893,650的权益,此处据此以引用的方式将该申请的公开并入。

3.【关于政府赞助的研究或开发的声明】

4.无

【技术领域】

5.本公开涉及一种新颖的方法,该方法允许对具有例如大量(>1000,甚至>20000)的非常细间距(通常≤10μm)互连焊盘的ic晶片(wafers)、芯片(chips)和/或小芯片(chiplets)进行已知良好小芯片(known good chiplet/kgc)测试。

背景技术:

6.ic芯片的探针测试(probe testing)在工业中是公知的,但是限于互连焊盘间距(pitches)相当大(例如,约50μm或更大)的芯片。如本文所公开的,微电子件的临时对齐的“粘性”结合(“tack”bonding)在本领域中是未知的。“粘性”结合是一种临时的结合,其具有被分离或成为永久的可能性。虽然金属表面的低温(摩擦结合、咬合、冷焊)固态结合已经很好地建立并且在文献中已有50多年的报道(甚至在极冷温度下),但是允许检查和返工的在室温下具有精细对齐(约微米尺度)能力的微制造工艺(如果需要)是不存在的。参见,例如,a.coucoulas和b.h.cranston,“compliant bonding-anew technique for joining microelectronic components”,ieee transactions on electron devices,第15卷,第9期,1968年9月和o.l.anderson,h.christensen以及p.andreatch,“technique for connecting electrical leads to semiconductors”journal of applied physics 28,923(1957年)。

7.本文中称为tech i、tech ii、tech iii和tech iv的现有技术可能涉及以下内容(并且不一定以这个顺序):级联微技术(参见www.cascademicrotech.com/files/pyrprobe_app.pdf);技术探针:(参见www.technoprobe.com/soluzione/tpeg-mems-t4-power-your-device);形状因子:(参见www.formfactor.com/product/probe-cards/foundry-logic/vx-mp);以及mjc悬臂(参见www.mjc.co.jp/en/products/semiconductor/probe_card.html)

8.在该文献中,公开了新颖的刀刃微结构触点,这些触点使得能够施加高的局部压力,这些压力形成在室温下建立的弱临时结合或形成更强的结合(如果使用更高的压力和温度)。附图所示的这些微结构可以使用标准微制造工艺来制造,并且容易集成到cmos或其它器件技术布局格式中。

9.如上所述,探针测试在工业中是公知的,但是在此提出的小间距集成刀刃(spike)方法在设计和实现方面与传统的探针或面积阵列(例如,金字塔探针(pyramid probe))技

术显著不同。该方法不是探针测试技术或热压结合技术的明显扩展。

10.关于2d和3d集成制造在集成之前是否需要已知良好裸片测试,或者未经筛选(未经测试)裸片的成品率是否足够高以及与集成工艺相关联的退出是否足够低以至于集成多裸片模块成品率是否足够,技术界人士之间一直存在一些争论。有人提出这个问题也就不足为奇了,因为在当今的商业工业中的许多情况下,未经筛选的裸片被封装,并且仅在封装之后进行筛选。然而,我们坚持认为,对于常规制造和先进的2d和3d集成制造,当总的集成裸片/小芯片面积超过约10cm2时,成品率和关联成本将驱动裸片/小芯片筛选的必要性(实际上,差成品率的经济影响是为什么诸如赛灵思、英特尔和英伟达的商业公司生产当今使用中介层技术集成的多芯片处理器的一个原因)。这一点在图1中例示并在下面详细讨论。

11.尽管可以开发在每个掩模步骤并入工艺细节和关联成品率限制的异常复杂且详细的集成电路成品率模型,但是用于半导体工艺的简单的常用成品率模型是墨菲(murphy)模型(参见图1中的等式),该模型仅取决于与所有掩模步骤(d)相关联的合计缺陷密度(aggregated defect density)和总裸片面积(total die area)(a)。墨菲模型考虑了缺陷之间的一定程度的空间相关性,因此预测比独立缺陷(泊松(poisson))模型稍高的成品率。假设从小芯片到小芯片的缺陷是独立的,具有未经筛选小芯片的完整模块组件的成品率简单地是所有单独小芯片的成品率乘以所有小芯片的集成成品率的乘积(在此,假设成功地集成各个单独小芯片的概率相同(图1的图例示出),使得总集成成品率是单个小芯片成品率与小芯片总数的次方之比)。成本乘数(即,生产单个全功能模块的成本除以生产单个未经测试模块的成本,或等同地,为了平均生产一个功能模块必须组装的模块的总数)仅仅是该总成品率乘积的倒数。对于所示的曲线图,假设最大小芯片尺寸为1cm2,但是曲线非常弱地依赖于该选择(因为更小的小芯片尺寸导致更高的成品率,但是对应地需要更多的小芯片来实现总的期望小芯片面积,使得总成品率大致不变)。

技术实现要素:

12.该文献公开了一种用于产生到微电子部件(例如半导体裸片)的临时电连接的方法,该微电子部件具有非常细间距的互连(例如,≤10μm的互连间距)。这种技术的一个重要使用情况是用非常细间距的互连(≤10μm间距)对半导体裸片或其它微电子部件进行电筛选,以便建立“已知良好裸片”(kgd)半导体模块或裸片的库存。如果期望,则本文所公开的技术可与具有间隔更宽的互连的半导体裸片或其它微电子部件一起使用。

13.本文公开的技术的另一用途涉及将多个裸片临时组装成集成组件,执行集成组件的测试或使用,然后替换可能已被确定为已失效或降级的一个或多个裸片。在一个实施方式中,所公开的方法通过使用具有成形尖端的小间距集成刀刃(spike)探针“凸块”的微制造以允许细间距探测或临时附着,来将常规晶片探测技术与裸片结合技术结合。所公开的技术克服了通常仅支持大得多的互连间距(约50μm或更大)的常规晶片探测方法的限制。对于裸片筛选/探针使用实施方式,优选地使用商业精密裸片结合器(或其适度的改进)将具有带微制造的尖锐spike探针凸块的探针头的测试夹具与被测裸片对齐,该结合器使得探针凸块能够着陆在接触焊盘上,并在spike凸块与被测小芯片的互连凸块之间产生低电阻(对于5

×

5μm2焊盘为≤1欧姆)接触。着陆工艺优选地不形成强冶金结合,由此可见,spike和小芯片凸块可以在测试之后容易地分离。在临时组件使用实施方式中,spike探针形成小

面积弱冶金结合,该结合不需要持续的压力(与裸片筛选情况相同),但是可以根据需要从触点分离,以便通过裸片更换来返工集成组件,或者可以用更大的力结合,以便形成更永久的传统冶金结合。

14.为了形成这种弱冶金结合,优选地,探针尖端由如ti(钛)或w(钨)或者甚至au(金)或al(铝)的金属形成,只要为探针尖端选择的金属至少比接触焊盘的金属稍微硬即可,接触焊盘可以由例如in(铟)、al、cu(铜)或au形成。因此,当在探针与焊盘之间施加压缩压力时,它们变得物理连接...,所发生的结合(称为弱冶金结合)实际上不是化学结合,而是更像物理约束的某种结合,这提供了优秀的欧姆接触,然而物理约束或弱冶金结合可以被破坏以允许集成组件的返工。

15.本文所公开的技术的一种用途是在包括裸片到裸片(die-to-die)、裸片到晶片(die-to-wafe)和晶片到晶片(wafer-to-wafer)配置的堆叠的部件对之间形成临时结合,以允许在永久倒装芯片结合之前进行对齐和质量检查(以及可能还有电测试),和/或允许表征临时组件。本文公开的技术可用于电子封装和集成应用,尤其是当前缺乏临时结合技术以允许在最终附着之前进行对齐检查以及如果需要的话进行修理的那些应用,诸如3d和2.5d集成、不同半导体的异质集成以及混合工艺。本文公开的临时结合技术可在室温(例如,23

°±

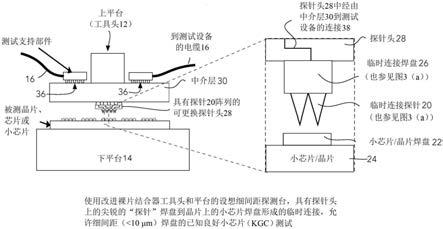

10℃,并且如果在气候受控环境中,则更好地为23

°±

3℃)下进行。

16.临时室温粘性结合的优点包括以下优点:

17.·

对于大的多芯片模块(>40cm2)能够实现>100倍的成本降低。

18.·

与sota商业探测技术相比,能够使探针间距《10μm减小》5倍。

19.·

小间距集成刀刃(spike)探针尖端在大凸块阵列(>20000)上提供均匀的低接触电阻,并且为了本公开的目的,低接触电阻小于1欧姆。但是即使接触电阻稍微大于1欧姆,这仍然优于其它技术。

20.在一个方面,本公开技术提供了一种用于在晶片、芯片或小芯片的测试期间形成到晶片、芯片或小芯片上的连接焊盘的临时结合的设备,设备包括:探针头,该探针头关联有多个探针,多个探针各自具有朝向至少一个点、脊和/或其他接触区域汇聚或到达其的倾斜侧壁,探针头在使用中用作用于在晶片、芯片或小芯片的测试期间探测所述晶片、芯片或小芯片的探针装置,各个晶片、芯片或小芯片包括表面,该表面上具有多个连接焊盘,各个连接焊盘在所述测试期间与多个探针的点、脊或其他接触区域中与探针头相关联的对应的一个或多个相配合;以及挤压设备,该挤压设备用于在要用探针头的一个或更多个探针测试的晶片、芯片或小芯片上的多个连接焊盘之间施加压力,从而在多个连接焊盘中的每一个与多个探针的点、脊或其他接触区域中的对应的一个或多个之间形成临时结合连接。

21.在另一方面,本公开技术提供了一种用于在测试夹具与晶片、芯片或小芯片之间形成可去除或临时连接的结合设备,晶片、芯片或小芯片具有耦合到晶片、芯片或小芯片中的待测试电路的多个扁平金属焊盘,临时结合设备包括:多个刀刃构件,该多个刀刃构件布置在所述测试夹具上,指向与测试夹具的长轴正交的方向;以及挤压设备,该挤压设备用于在刀刃构件与多个扁平晶片焊盘之间施加压缩力,从而在使用中在(i)待测试的晶片、芯片或小芯片上的多个扁平晶片焊盘与(ii)多个刀刃构件之间形成临时电连接结合。

22.在上述结合设备中,在晶片、芯片或小芯片的电路已经被测试并且确定为良好之后,挤压设备在刀刃构件与多个扁平晶片焊盘之间施加比最初使用的更大的压缩力,从而

在使用中在(i)晶片、芯片或小芯片上的多个扁平晶片焊盘与(ii)多个刀刃构件之间形成高性能电连接结合,高性能电连接结合具有比临时电连接结合更大的结合强度。

23.在又一方面,本公开技术提供了一种使用临时结合连接测试晶片、芯片或小芯片的方法,包括:形成测试设备,该测试设备包括具有倾斜侧壁的多个构件,这些构件指向与测试设备的长轴垂直的方向;在测试设备的具有倾斜侧壁的构件和与被测晶片、芯片或小芯片相关联的焊盘之间施加压缩力,以在测试设备的具有倾斜侧壁的构件和与被测晶片、芯片或小芯片相关联的焊盘之间形成临时电连接;以及进行对被测晶片、芯片或小芯片中的电路的测试,所述测试包括经由所述临时电连接向所述被测晶片、芯片或小芯片施加电信号和/或感测所述被测晶片、芯片或小芯片中的电信号。

【附图说明】

24.图1呈现了演示假设用于小芯片制造成品率的墨菲(簇缺陷)模型和用于小芯片集成成品率的泊松(独立缺陷)模型的集成模块成本乘数对总小芯片面积的曲线图。

25.图2提供了优选地使用稍微改进的裸片结合器的细间距探测台的示意图,该裸片结合器具有上平台(附着有探针头的工具头)和下平台(附着有被测晶片或小芯片),使得可以在探针头上的尖锐的(尖的)“探针”焊盘与晶片、芯片或小芯片上的焊盘之间形成临时连接,允许细间距(<10μm)的焊盘已知良好小芯片(kgc)测试。对现有技术裸片结合器的修改优选地包括硬件和配方(软件)改变。硬件的改变是图2所示的在上平台与下平台之间的那些改变,并且优选地改变用于结合器的配方,使得在探测之后,探针头保持在上平台上。结合器将把结合的芯片留在配合件上(通过释放真空)。

26.图3(a)至图3(c)描绘了具有三个蒸镀金的尖锐的或钉状的触点的金焊盘(参见图3(a));由具有交叉钉触点的焊盘的低温结合阵列形成的十微米间距的菊花链(daisy chain)(参见图3(b));以及基于图3(c)所示的四个测试结果的四个150

×

150阵列的测量串联电阻对链长度的曲线图(参见图3(c)),其指示100%的成品率和130mohm(0.13欧姆每触点)的基本上均匀的接触电阻。

27.图4描绘了晶片、芯片或小芯片探针布置的实施方式,其可以在探测台处用于已知良好芯片或小芯片(kgc)工艺。

28.图4a描绘了晶片、芯片或小芯片探针布置的另一个实施方式,其可以在探测台处用于已知良好芯片或小芯片(kgc)工艺。

29.图5(a)至图5(d)描绘了用于制造本文所公开的探针结构的工艺的实施方式,该工艺利用标准微制造工艺;刀刃探针微结构的高度由抗蚀图案开口控制;通常,这可以变化以产生高度范围从《1μm到》10μm的探针。

30.图6(a)和图6(b)各自以剖视图描绘了具有相对较软内芯与相对较硬外表面的单个探针(参见图6(a))或具有相对较软和相对较硬材料的交替层的探针(参见图6(b))。

【具体实施方式】

31.以下描述被提出为使得本领域普通技术人员能够进行并使用本发明,并且将本发明并入在特定应用的语境中。各种修改以及在不同应用中的各种用途将对本领域技术人员容易地清晰,并且这里所定义的一般原理可以应用于宽范围的实施方式。由此,本发明不旨

在限于所提出的实施方式,而是符合与这里所公开的原理和新型特征一致的最宽范围。

32.在以下详细描述中,为了提供本发明的更彻底理解,阐述了大量具体细节。然而,将对本领域技术人员显而易见的是,本发明可以在不必限于这些具体细节的情况下实践。在其他情况下,为了避免使本发明模糊,以框图形式而不是详细地示出公知结构和装置。

33.读者的注意力被引导到(i)与本说明书同时提交的所有文件和文献,文件和文献与本说明书一起对公众审查开放(此处以引证的方式将所有这种文件和文献的内容并入)和(ii)此处以引证的方式另外并入的(但不是在物理上与本说明书一起提交的)所有文件和文献。

34.在本说明书中公开的所有特征(包括任意所附权利要求、摘要以及附图)可由用于相同、等效或类似目的的另选特征来替换,除非另外明确陈述。由此,除非另外明确陈述,否则所公开的每个特征仅是通用的一系列等效或类似特征的一个示例。

35.此外,未明确陈述用于执行指定功能的“装置”或用于执行具体功能的“步骤”的权利要求中的任意元素不被解释为如在35u.s.c第112节第6段落中指定的“装置”或“步骤”条款。具体地,这里权利要求中“的步骤”或“的动作”的使用不旨在调用35u.s.c第112节第6段落中的规定。

36.在本文件的上下文中,spike概念主要被描述为用于对“小芯片”或具有非常小、细间距焊盘的裸片执行已知良好裸片测试的手段。我们设想相同的结构和大致相同的结合方法可以用于临时组装用途的实施方式。

37.本文公开了一种用于对具有大量(>1000,甚至>20000)的非常细间距(≤10μm)互连焊盘的小芯片执行已知良好小芯片(kgc)测试的新颖方法,该方法降低了包括例如大的合计小芯片面积的集成电路(ic)或芯片模块的成本(以10x到100x的因数)。所公开的方法利用了我们已经开发的用于在该目标间距(以及以下)的焊盘上制造小间距集成刀刃(spike)均匀尖锐凸块的技术,来开发新颖的细间距探测技术,表示对现有技术的显著改进(参见表i)。

38.表i(下面)演示了,与现有技术(tech i-tech iv)相比,本文公开的hrl探针技术(有时称为spike)为面积阵列探测提供了焊盘间距的》5倍的减小,同时还支持大量的触点和低的接触电阻。

[0039][0040]

考虑到上述表,本文公开的hrl spike技术(hrl探针20)满足<25欧姆-μm2的目标比接触电阻,这与图3(c)中阐述的数据一致。图3(c)是四个150

×

150阵列的测量串联电阻对链长度的曲线图,其指示100%的成品率和130mohm(0.13欧姆每触点)的基本上均匀的接触电阻。由于对于5

×

5μm2的焊盘,<25欧姆-μm2的目标等于<1欧姆每触点,所以获得0.13欧姆每触点的接触电阻意味着该技术已经超过该目标。

[0041]

如上所述,关于2d或3d集成制造系统在集成之前是否需要已知良好裸片测试,或者未经筛选裸片的成品率是否足够高以及与集成工艺相关联的退出是否足够低以至于2d或3d集成制造系统模块成品率是否足够,技术界人士之间一直存在一些争论。

[0042]

我们相信,对于常规制造和2d或3d集成制造系统,当总集成裸片/小芯片面积超过约10cm2时,成品率和关联成本将驱动裸片/小芯片筛选的必要性。这一点在图1中例示并在下面更详细讨论。

[0043]

尽管可以开发在每个掩模步骤并入工艺细节和关联成品率限制的异常复杂且详细的集成电路成品率模型,但是用于半导体工艺的简单的常用成品率模型是墨菲模型(参见图1中的等式),该模型仅取决于与所有掩模步骤(d)相关联的合计缺陷密度和总裸片面积(a)。墨菲模型考虑了缺陷之间的一定程度的空间相关性,因此预测比独立缺陷(泊松)模型稍高的成品率。假设从小芯片到小芯片的缺陷是独立的,具有未经筛选小芯片的完整模块组件的成品率简单地是所有单独小芯片的成品率乘以所有小芯片的集成成品率的乘积(在此,假设成功地集成各个单独小芯片的概率相同(图1的图例示出),使得总集成成品率是单个小芯片成品率与小芯片总数的次方之比)。成本乘数(即,生产单个全功能模块的成本除以生产单个未经测试模块的成本,或等同地,为了平均生产一个功能模块必须组装的模块的总数)仅仅是该总成品率乘积的倒数。对于所示的曲线图,假设最大小芯片尺寸为1cm2,但是曲线非常弱地依赖于该选择(因为更小的小芯片尺寸导致更高的成品率,但是对应地需要更多的小芯片来实现总的期望小芯片面积,使得总成品率大致不变)。

[0044]

对于先进半导体(例如cmos)工艺的典型的或甚至非常激进的缺陷密度(0.1-0.3/cm2),一旦裸片面积超过1cm2,单个裸片的成品率开始显著下降(75%到90%)。结果,即使对于适度的总小芯片面积,没有裸片筛选的成本乘数也变得难以接受(例如,10倍的成本由具

有0.3/cm2缺陷密度的7.8cm2总小芯片面积或具有0.1/cm2缺陷密度的23.4cm2总小芯片面积造成)。相比之下,即使是相对适度的每小芯片集成成品率(99%至99.9%)产生的成本乘数也对应地非常低。因此,一旦总的小芯片面积超过大约10cm2,已知良好小芯片(kgc)筛选(测试)就变得重要,以便通过确保半导体晶片/芯片/小芯片在将晶片/芯片/小芯片并入到制造中的一些设备之前实际上是良好的(kgc)来管理成本。实际上,从图1中可以看出,即使执行kgc筛选的成本将变成生产单个集成模块的成本的几倍,在足够大的总小芯片面积下,与利用有缺陷的晶片/芯片/小芯片相关联的成本考虑仍然会使kgc筛选具有成本效益。

[0045]

对于常规的半导体裸片(芯片),目前存在许多探测技术,包括用于周边触点的各种形式的dc和微波“楔形”探针以及诸如用于面积阵列探测的级联微技术的金字塔探针卡(其使用柔性衬底上的微成型探针尖端)的产品。然而,这些技术通常限于相当大的间距(≥50μm)的互连焊盘,并且一些技术还限于相对少量的连接(约100至200)。参见例如级联微技术的“pyramid probe cards”(可在www.cascademicrotech.com/files/pyrprobe_app.pdf获得);技术探针的“tpeg

tm mems t4_power your device”(可在www.technoprobe.com/soluzione/tpeg-mems-t4-power-your-device/获得);形状因子的“vx-mp”(可在www.formfactor.com/product/probe-cards/foundry-logic/vx-mp/获得);以及mjc micronics日本有限公司的“probe card”(可在www.mjc.co.jp/en/products/semiconductor/probe_card.html获得)。

[0046]

从长远观点来看,为了大量生产,设想kgc探测解决方案(参见图2),其将探针卡技术的最佳特征与常规裸片结合器的许多特征(例如,精确的放置准确度和匹配力的施加)相组合,并且利用成形(尖锐的)的细间距凸块作为探针尖端20,以与被测晶片/芯片/小芯片24上的细间距小芯片焊盘22临时配合。探针20具有锥形边缘,其可以形成为点或者可以采取形成为脊(ridge)的楔形,如图3(a)所示。探针20上的锥形边缘或斜面可以使用本领域公知的技术形成。对于使用图像反转技术形成具有锥形侧壁的尖锐的、钉状或刀刃形构件的一种方法的讨论,参见例如“image reversal resists and their processing”(作为附录a附上的副本)。如果附录a中图107所示的金属沉积继续进行,则所得探针20可具有尖的刀状远边或尖端,这与附录a中所示的较钝的边或尖端相反。实施本技术的人可以选择使用本文公开的尖锐的、钉状或刀刃形的探针20,但应该理解,探针20可以另选地稍微钝一些,从而具有与本文描绘的探针20相比不那么尖锐或刀状的接触区域。

[0047]

接触和测试小芯片裸片和/或晶片上的细间距(≤10μm)焊盘的成功方法应当满足多个准则:

[0048]

1.必须以相对低的电阻(优选地,对于每个单独的小芯片焊盘<1欧姆)可靠地进行被测晶片/芯片/小芯片上的焊盘的整个阵列与探针焊盘之间的电连接。

[0049]

2.必须可以合理地容易地将探针焊盘从被测晶片/芯片/小芯片上的焊盘分离。

[0050]

3.在探测之后,被测晶片/芯片/小芯片上的焊盘必须仍然支持可靠的永久封装-对小芯片焊盘的任何损坏必须不妨碍随后的永久集成(例如,到中介层上的凸块结合)。

[0051]

4.在需要更换探针焊盘之前,探针焊盘必须经受与被测晶片/芯片/小芯片上的不同组焊盘的相对大量的配合(例如,>100个配合,并且优选地,更多的配合)。

[0052]

5.必须有一种方法,该方法将细间距(≤10μm)的探针焊盘对齐和操纵为与被测晶片/芯片/小芯片上的对应焊盘接触,同时维持焊盘在整个晶片/芯片/小芯片面积上对准。

[0053]

使用蒸发金属沉积(通常为ti、au或al)和剥离光刻(例如,参见附录a),我们已经演示了在十微米间距的凸块或探针20阵列上制造高(几微米高)尖端的非常均匀的阵列的能力。为了使探针20的尖端更坚固,我们推荐向探针20添加钨或镍层的涂层(参见图6)。被测晶片/芯片/小芯片24使用优选具有扁平表面轮廓的常规au或au-sn焊盘22。当通过结合设备施加压缩压力时,我们预期上面提出的较硬的探针尖端(具有钨或镍的层或涂层)稍微进入焊盘22,由此在测试期间在探针20与焊盘22之间形成电接触,但是优选地不在两者之间形成冶金结合(如常规的凸块结合),并且不排除在测试完成之后被测晶片/芯片/小芯片24的分离或者随后将被测(且良好)晶片/芯片/小芯片24永久结合到利用其的一些设备中。

[0054]

多个探针20可以形成在基座或焊盘26上,因此经由基座或焊盘26和导体38共同电连接到测试设备。图3(a)的多个探针20的尺寸被设置为与待测试的晶片/芯片/小芯片上的单个焊盘22临时配合。晶片的直径通常为几英寸,并且许多芯片(或小芯片)由单个晶片形成。术语“芯片(chip)”是指单个集成电路或ic。术语“小芯片(chiplet)”是指可以与其他小芯片封装或组合以形成单个集成电路或ic的集成电路或ic。可以在逐个晶片的基础上或者逐个芯片的基础上或者逐个小芯片的基础上进行这里公开的测试。如果在逐个晶片的基础上进行,那么可以同时测试晶片中具体实施的所有芯片,或者可以在某个时刻测试其子集。如果在逐个芯片的基础上或者在逐个小芯片的基础上进行,则优选的是,芯片或者小芯片在晶片中保持彼此附着,以便减少裸片结合器的设置工作量。当然,如果同时测试晶片上的所有芯片或小芯片,则探针头28的尺寸应设置为使得多个探针阵列20可以与对应的多个焊盘阵列22接触,每个这样的阵列通常与晶片中的单个芯片或小芯片相关联。

[0055]

可以在探针头28上制造探针焊盘20的阵列,该探针头优选地被构造为附着到中介层30的可替换单元(临时测试夹具),可以使用本文公开的设备和工艺将被测晶片/芯片/小芯片24临时附着到该中介层。使用例如由法国圣约里尔的智能设备技术公司(set公司sa)制造的fc300裸片结合器,在压缩下将探针20与细间距小芯片焊盘22图案配合,以在其上头(或工具头12)与其下平台14之间施加压缩力,从而在晶片/芯片/小芯片24的测试期间在探针20和与它们配合的焊盘22之间施加压缩力。裸片结合器用作挤压设备,当然,可以使用其他设备来代替在探针阵列20与细间距晶片/芯片/小芯片24焊盘22的对应图案(或阵列)22之间施加压缩力。中介层30可以将电连接从细间距小芯片焊盘22的图案或阵列经由探针20和探针头28分布到常规探针焊盘36的布置,该布置优选地布置在中介层30的周边(参见图2)。在一些实施方式中,常规探针焊盘36的布置可位于别处,诸如在探针头28的周边处(参见图4)。与在被测晶片/芯片/小芯片24上使用的细间距焊盘图案相比,常规的探针焊盘36通常以大得多的(相对粗的,常规的)间距布置,从而允许使用常规探针和探针台硬件的小芯片测试与常规的粗间距探针焊盘图案36接合,并且进行对晶片/芯片/小芯片24期望的任何测试,以确保在差不多永久固定到利用晶片/芯片/小芯片24构造的一些设备之前是kgc。

[0056]

图4在许多方面与图2的实施方式类似,但是在图4的实施方式中,焊盘36布置在探针头28上。示出了焊盘36(用于测试设备)与探针20(用于被测晶片/芯片/小芯片24)之间的示例性连接38,并且在该实施方式中,在中介层(interposer)30内或上不需要连接。而且,在图4中,省略了在中介层30与被测晶片或小芯片24之间施加压力的裸片结合器的元件(上平台12和下平台14),从而允许图4更好地描绘探针20。

[0057]

图4a呈现了探针20、相关联的焊盘26、探针头28和中介层30的又一实施方式,但是

在该实施方式中,探针20不仅用于与被测晶片/芯片/小芯片24上的焊盘22接触,而且还用于(i)在(在该实施方式中可替换的)探针头28与中介层30之间形成导电接触,而且(ii)在中介层30与读出ic之间形成导电接触,在该实施方式中使用该读出ic代替图4的实施方式中的焊盘36。读出ic执行上述测试设备的功能。而且,与图4中相同,省略了在中介层30与被测晶片或小芯片24之间施加压力的裸片结合器的元件(上平台12和下平台14),从而允许图4a更好地描绘探针20及其额外用途。

[0058]

本领域技术人员现在应当认识到,探针20可以以多种不同的方式使用,并且用于测试晶片/芯片/小芯片24的设备可以采取若干不同的形式,并且现在本领域技术人员将想到除图2、4和4a所描绘的那些形式之外的另外的形式。

[0059]

图5(a)至图5(d)中示出了用于制造探针20的工艺流程的一个实施方式。探针20优选地具体实施为刀刃微结构。但是探针20不必以尖锐或刀刃端部结束,而是如果期望可以稍微更钝。控制刀刃探针结构的重要因素是凹入光刻胶40(参见图5(b))轮廓(使用图像反转光刻)和探针20沉积期间蒸发源或溅射源的几何扩展。对于图像反转光刻的讨论,参见附录a。根据抗蚀剂40中的线宽开口g的尺寸,可以在宽范围(例如<lμm-l0μm)上设计刀刃探针微结构的高度(参见5(b))。通过减少在探针形成期间沉积的材料(参见图5(c)中的金属42)的量,可以使探针20更钝并且更不象刀刃。

[0060]

探针制造工艺采用标准半导体制造工艺,从诸如衬底281或301的衬底开始,该衬底具有布置或形成在其上的诸如电介质层282或302的电介质层。由于探针20可与探针头28和/或中介层30中的任一个或两者一起使用,因此在此描述了两种可能性,因为相同的工艺流程可根据期望与任一个或两者一起使用。参见图5(a)。衬底281或301优选由硅形成,因为其机械强度高并且还由于其低成本。衬底281或301以及电介质层282或302形成探针头28(参见图2、4和4a的实施方式)或中介层30(参见图4a的实施方式)。

[0061]

使用图案化的抗蚀剂(未示出)沉积金属(通常为ti、au或al)接触层并将其形成为探针焊盘26的阵列,或者另选地,可以首先沉积抗蚀剂,然后图案化,然后沉积金属接触层,然后通过剥离工艺形成探针焊盘26。图5(a)中未示出的是优选地在形成探针焊盘26的同时形成的额外金属,该额外金属形成例如粗间距探针焊盘图案36(如果利用的话)以及可能还形成提供焊盘36(如果使用的话,用于测试设备)与探针20(用于被测晶片/芯片/小芯片24以及一些实施方式中的其他地方)之间的连接的导体38的全部或一部分,因为这些导体容易使用标准半导体制造工艺形成。同样未示出的是埋设导体38或用于导体38的竖直硅通孔或也用于先前图中描绘的导体38的再分布层,其也可以使用标准半导体制造工艺容易地形成。这些细节在图5(a)至图5(d)中没有示出,因为这些图旨在示教制造刀刃探针20的方法。

[0062]

在如图5(a)所示形成探针焊盘26之后,在电介质层282或302上形成凹入抗蚀剂层40(参见图5(b)),并图案化为具有倾斜侧壁(由于抗蚀剂40的底切),在抗蚀剂40层的顶部处的每个探针焊盘26上方留下通向其中的开口或间隙g。如上所述,开口或间隙g的尺寸(线宽)将影响即将沉积的探针20的高度。在图5(c)中,每个焊盘26被描绘为具有单个探针20。该实施方式可以容易地修改(通过使探针焊盘26更宽),使得单个探针焊盘26可以容纳多个探针20,如图2和4所示。

[0063]

转到图5(c),然后优选地通过蒸发在图5(b)所示的结构上沉积金属42(通常为ti、au、pd或al)。大量沉积的金属42终止于抗蚀剂40上,但是一些金属42通过抗蚀剂40中的开

口或间隙g,从而形成具有倾斜侧壁的金属探针20。金属探针20由在经由抗蚀剂40中的开口或间隙g暴露的每个探针焊盘26上的金属42形成。

[0064]

金属42可以从如上所述的au或al开始,但是在沉积过程结束时变为钨或镍,使得探针以其上的钨或镍薄层结束,以使它们如上所述更坚固。图6(a)以剖视图描绘了具有相对较软的内芯20i(例如由au或al制成)和相对较硬的外表面20o(例如由ti或w制成)的单个探针20。这些材料可以颠倒,内芯20i由相对较硬的材料制成,外表面20o由相对较软的材料制成。

[0065]

另选地,探针20可由相对较硬材料20h的层(例如参见图6(b)的实施方式)的堆叠形成,例如与相对较软材料20s的层交替。因此探针20的堆叠实施方式可以包括不同材料层,诸如ti/au/ti/au。此外,图6(b)的堆叠实施方式可以用作如图6(a)所描绘的探针20的内芯20i,在这种情况下,图6(b)的材料堆叠被外表面20o覆盖,与图6(a)的实施方式的情况相同。外表面20o可以类似地限定为类似于图6(b)所示的材料的堆叠。因此,存在具有不同硬度(弹性模量)的许多不同材料可以产生具有期望弹性模量的探针20的许多方式。弹性模量支配探针20的接触特性。通常,是被测晶片/芯片/小芯片24的金属接触焊盘22确定探针20期望使用什么材料。而且,人们通常期望足够硬的探针20,使得它使接触焊盘22塑性变形。我们发现,分层金属结构(参见图6(b)具有交替的硬金属20h和软金属20s,使得由例如ti或ni形成的探针20的尖端或尖锐端部21最初在接触焊盘22上形成凹痕,然后当裸片结合器(die bonder)施加压缩力时,探针20的由例如al或au形成的较软主体部分20s将展开。

[0066]

再次转到图5(c),例如,如图5(d)所示,通过在剥离工艺中溶解抗蚀剂40,暴露探针20,来去除抗蚀剂40上的金属42以及抗蚀剂40。

[0067]

现在已经根据专利法规的要求描述了本技术,本领域技术人员将理解如何对本发明进行改变和修改以满足其特定要求或条件。这种改变和修改可以在不脱离如本文公开的本发明的范围和精神的情况下进行。

[0068]

为了例示和公开,根据法律的要求,呈现了示例性和优选实施方式的前述详细描述。不旨在穷尽也不将本发明限于所述的精确形式,而是仅使得本领域其他技术人员能够理解本发明如何适合于特定的用途或实施方案。修改例和变型例的可能性对于本领域技术人员将是明显的。示例性实施方式的描述不旨在限制,这些实施方式可以已包括公差、特征尺寸、特定操作条件、工程规范等,并且可以在实施方案之间变化或随着现有技术的变化而变化,并且不应从其暗示任何限制。申请人已经关于当前技术水平做出了本公开,但是还预期进展,并且未来的改编可以考虑这些进展,即根据当时的当前技术水平。如果适用,则预期本发明的范围由书面权利要求以及等同物来限定。对单数形式的权利要求元件的参照不旨在意指“一个且仅一个”,除非明确这样陈述。而且,不管本公开中的元件、部件、方法或工艺步骤是否在权利要求中明确列举,该元件、部件或步骤都不旨在专用于公众。本文中没有权利要求元素被解释为在35美国第112节第6段的规定下,因为它存在于提交本技术的日期,除非元件使用短语“用于

……

的装置”明确叙述,并且本文的方法或工艺步骤均不在这些规定下进行解释,除非步骤使用短语“包括步骤

……”

明确叙述。

[0069]

可以在不偏离本发明的范围的情况下对此处描述的系统、设备以及方法进行修改、添加或省略。系统和设备的部件可以集成或分离。而且,系统和设备的操作可以由更多、更少或其他部件来执行。方法可以包括更多、更少或其他步骤。另外,步骤可以以任意合适

的顺序来执行。如本文献中使用的,“每个”是指集合的每个成员或集合的子集的每个成员。

[0070]

本发明的概念包括:

[0071]

概念1.一种用于在晶片、芯片或小芯片的测试期间形成到晶片、芯片或小芯片上的连接焊盘的临时结合的设备,设备包括:

[0072]

探针头,该探针头关联有多个探针,多个探针各自具有朝向至少一个点、脊和/或其他接触区域汇聚或到达其的倾斜侧壁,探针头在使用中用作用于在晶片、芯片或小芯片的测试期间探测所述晶片、芯片或小芯片的探针装置,各个晶片、芯片或小芯片包括表面,该表面上具有多个连接焊盘,各个连接焊盘在所述测试期间与多个探针的点、脊或其他接触区域中与探针头相关联的对应的一个或多个相配合;以及

[0073]

挤压设备,该挤压设备用于在要用探针头的一个或更多个探针测试的晶片、芯片或小芯片上的多个连接焊盘之间施加压力,从而在多个连接焊盘中的每一个与多个探针的点、脊或其他接触区域中的对应的一个或多个之间形成临时结合连接。

[0074]

概念2.概念1的设备,其中,挤压设备包括用于在晶片、芯片或小芯片的测试期间施加压力以维持临时结合连接或在多个连接焊盘与多个探针的点、脊或其它接触区域中的对应一个或多个之间形成临时冶金结合的装置。

[0075]

概念3.概念1或2的设备,其中,具有倾斜侧壁的探针由刀刃微结构限定,这些刀刃微结构在使用中在垂直于主平面的方向上突出,该主平面由待测试的晶片、芯片或小芯片上的连接焊盘中的至少一个限定。

[0076]

概念4.概念3的设备,其中,刀刃微结构具有相对软的导电材料的内芯和布置在所述内芯上的相对硬的导电材料的外涂层或层。

[0077]

概念5.概念3的设备,其中,刀刃微结构具有相对软的导电材料的主体和布置在所述主体上的相对硬的导电材料的尖端。

[0078]

概念6.概念4的设备,其中,临时结合连接具有小于一欧姆的欧姆电阻。

[0079]

概念7.概念1至6中任一项的设备,其中,挤压设备是常规的裸片结合器。

[0080]

概念8.概念1至7中任一项的设备,其中,探针头具有第一主表面和第二主表面,并且其中,多个探针布置在探针头的第一主表面上。

[0081]

概念9.一种用于在测试夹具与晶片、芯片或小芯片之间形成可去除和/或临时连接的结合设备,晶片、芯片或小芯片具有耦合到晶片、芯片或小芯片中的待测试电路的多个扁平金属焊盘,临时结合设备包括:

[0082]

多个刀刃构件,该多个刀刃构件布置在所述测试夹具上,指向与测试夹具的长轴正交的方向;以及

[0083]

挤压设备,该挤压设备用于在刀刃构件与多个扁平晶片焊盘之间施加压缩力,从而在使用中在(i)待测试的晶片、芯片或小芯片上的多个扁平晶片焊盘与(ii)多个刀刃构件之间形成临时电连接结合。

[0084]

概念10.根据概念9的结合设备,其中,刀刃构件的数量大于扁平晶片焊盘的数量。

[0085]

概念11.根据概念9或10的结合设备,其中,临时电连接结合是具有不大于1欧姆的电阻的临时粘性结合。

[0086]

概念12.根据概念9至11中任一项的结合设备,其中,刀刃构件包括相对软的金属材料的内芯和布置在相对软的金属材料上的相对较硬的金属材料的外层。

[0087]

概念13.根据概念9至12中任一项的结合设备,其中,临时电连接结合为临时冶金结合,该临时冶金结合可被克服而不会损坏晶片、芯片或小芯片中的电路。

[0088]

概念14.根据概念13的结合设备,其中,在晶片、芯片或小芯片的电路已经被测试并且确定为良好之后,挤压设备在刀刃构件与多个扁平晶片焊盘之间施加比最初使用的更大的压缩力,从而在使用中在(i)晶片、芯片或小芯片上的多个扁平晶片焊盘与(ii)多个刀刃构件之间形成高性能电连接结合,高性能电连接结合具有比临时电连接结合更大的结合强度。

[0089]

概念15.根据概念9至14中任一项的临时结合设备,其中,临时电连接结合为接触(非冶金)结合。

[0090]

概念16.一种使用临时结合连接测试晶片、芯片或小芯片的方法,包括:

[0091]

a.形成测试设备,该测试设备包括具有倾斜侧壁的多个构件,这些构件指向与测试设备的长轴垂直的方向;

[0092]

b.在测试设备的具有倾斜侧壁的构件和与被测晶片、芯片或小芯片相关联的焊盘之间施加压缩力,以在测试设备的具有倾斜侧壁的构件和与被测晶片、芯片或小芯片相关联的焊盘之间形成临时电连接;以及

[0093]

c.进行对被测晶片、芯片或小芯片中的电路的测试,所述测试包括经由所述临时电连接向所述被测晶片、芯片或小芯片施加电信号和/或感测所述被测晶片、芯片或小芯片中的电信号。

[0094]

概念17.概念16的方法,其中,具有倾斜侧壁的构件限定刀刃微结构。

[0095]

概念18.概念17的方法,其中,所述刀刃微结构包括相对软的金属材料的主体和布置在相对软的金属材料上的相对较硬的金属材料的尖端。

[0096]

概念19.概念17或18的方法,其中,刀刃微结构的数量大于与被测晶片、芯片或小芯片相关联的焊盘的数量。

[0097]

概念20.概念17至19中任一项的方法,其中,刀刃微结构的多个尖端接触与被测晶片、芯片或小芯片相关联的焊盘中的至少一个。

[0098]

概念21.概念17至20中任一项的方法,其中,刀刃微结构的多个尖端接触与被测晶片、芯片或小芯片相关联的焊盘中的对应焊盘。

[0099]

概念22.概念16至21中任一项的方法,其中,测试设备包括探针头,该探针头具有多个构件,该多个构件上布置有倾斜侧壁,多个构件指向与探针头的长轴垂直的方向。

[0100]

概念23.概念22的方法,其中,测试设备还包括布置在探针头与裸片结合器的一部分之间的中介层,裸片结合器在测试设备的具有倾斜侧壁的构件和与被测晶片、芯片或小芯片相关联的焊盘之间施加压缩力。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1