一种组网检测方法及系统与流程

[0001]

本申请涉及电子设计自动化技术领域,尤其涉及一种组网检测方法及系统。

背景技术:

[0002]

随着芯片行业的发展,芯片集成度越来越高,逻辑门规模也越来越大,对逻辑设计的验证也提出了挑战,在基于可编程逻辑阵列(fpga)的原型验证中,经常会遇见fpga资源不能满足需要的情况,这时候需要采用多个fpga,并通过输入\输出(io)端口组网互联来组成更大的逻辑资源,以满足设计需要。由于不同的逻辑设计对组网的拓扑需求不同,例如有些采用星型拓扑,有些采用矩阵拓扑,有些采用队列拓扑。因此现有技术中是把每个fpga的所有io端口资源,按照某固定数字(常见32-160)分组,连接到线缆(cable)插座上,再通过插座之间连接线缆,以实现灵活的拓扑。

[0003]

在实际连接线缆的操作流程中,通常有两种方式:第一种方式是根据设计拓扑需要,给出不同fpga之间的连接线缆关系和数量,分配特定的插座,并查询插座包含的io端口对应的fpga io pin位置(pin location),并把它分配到fpga管脚约束文件(design constraint,xdc)中,并根据约束文件要求生成对应的比特流编程下载fpga。然后把这些插座用线缆连接起来即可工作。但在实际应用中存在如下风险:当线缆连接错误时,存在io输出多驱动的风险,这会导致损坏fpga芯片,因此,在实际fpga逻辑工作之前,需要对线缆互联关系做检测,以确保互联正确。

[0004]

第二种方式是根据大致的拓扑关系,先连接好线缆,然后检测线缆互联关系,生成互联网表,并查询插座包含的io端口对应的fpga io pin位置(pin location),并把它分配到fpga管脚约束文件(design constraint,xdc)中,并根据约束文件要求生成对应的比特流编程下载fpga。同样的,为了避免互联错误风险,在实际逻辑工作前,需要检测线缆关系并确保无误。上述两种过程,都需要识别每一根信号线的位置,连线关系,并生成约束文件,对于采用设计分割如rtl分割、网表分割等情况,还需要生成硬件系统描述语言(hdl)顶层互联关系文件,以用于后续的动态仿真(simulation),现有手段均是采用手动识别输入,不仅过程麻烦,而且出错概率高。

[0005]

另一方面,fpga互联系统中,经常需要检测互联线缆的可靠性,检测线缆是否存在断路,短路等情况。对于线缆互联的检测,一般采用外表直观检测和万用表测量检测两种方法。外表直观检测用来检测连接器之间是否有线缆互联、引线断裂等现象。万用表检测是用万用表的欧姆档对线缆相连的连接器的两端进行测量,其连通电阻值应小于0.5ω。外表直观检测操作虽然简单,但是精确度无法保证。万用表检测精确度高,但是需要手动测量,而且对于集成度高采用底部贴片方式的连接器,引脚没有全部暴露在外面,万用表的表针量取信号的操作难度大。

技术实现要素:

[0006]

有鉴于此,本申请实施例提供一种组网检测方法及系统,至少部分解决现有技术

中存在的问题。

[0007]

上述技术方案具体包括:一种组网检测方法,应用于基于可编程逻辑阵列的原型验证系统,其中,所述原型验证系统包括多个系统单板和一上位机,所述上位机分别与所述系统单板通信连接;所述系统单板包括一控制器和与所述控制器连接的多个可编程逻辑阵列,每个所述可编程逻辑阵列包括多个连接器,每个所述连接器中包括多个信号通道,所述连接器之间通过排线将所述信号通道对应连接,所述信号通道用于接收和发送信号;还包括以下步骤:步骤s1,所述上位机为每个所述系统单板、所述可编程逻辑阵列以及所述信号通道分配标识信息,并将所述标识信息载入对应的所述控制器;其中,所述信号通道的标识信息中包括所述系统单板的标识信息和所述可编程逻辑阵列的标识信息;步骤s2,将所述信号通道统一设置为接收信号模式;步骤s3,检测所述信号通道是否接收到一数据包:若是,则切换至下一所述信号通道并返回步骤s3;若否,则转向步骤s4;步骤s4,将当前所述信号通道切换为发送信号模式,并通过该信号通道发送所述数据包,随后切换至下一所述信号通道并返回步骤s3,其中所述数据包中包括所述信号通道的标识信息和校验码;步骤s5,重复步骤s3至步骤s4,直至所有的所述信号通道均检测完毕后转向步骤s6;步骤s6,所述控制器采集每个所述信号通道的标识信息和对应信号通道接收的所述数据包以生成一互联数据,并将所述互联数据发送至所述上位机;步骤s7,所述上位机根据所述互联数据处理得到互联信息;步骤s8,根据所述互联信息和硬件系统描述语言模板自动生成用于描述组网连接的硬件系统描述语言文件。

[0008]

优选地,其中,所述步骤s7进一步包括:步骤s70,依次读取所述互联数据,并判断所述互联数据中是否存在所述数据包:若不存在,则将所述互联数据对应的所述信号通道确认为没有线缆连接,并记录入一矩阵表格中;若存在,则转向步骤s71;步骤s71,读取所述数据包中的所述信号通道的标识信息,将所述互联数据对应的所述信号通道确认为与所述数据包中标识信息对应的信号通道通过线缆相连接,并记录入所述矩阵表格中;步骤s72,读取所述数据包中所述校验码,并于所述校验码出现错误时确认为线缆短路或连接质量不佳,并记录入所述矩阵表格中;步骤s73,重复步骤s70至步骤s72,直至所有所述互联数据均处理完毕后转向步骤s74;步骤s74,将生成的所述矩阵表格输出为所述互联信息。

[0009]

优选地,其中,对每个所述连接器中仅选取其中一个所述信号通道进行所述步骤s3至步骤s4的检测,生成对应于每个连接器的所述互联数据;

判断所述互联数据中是否存在所述数据包:若不存在,则将所述互联数据对应的所述连接器确认为没有线缆连接,并记录入所述矩阵表格中;若存在,则读取所述数据包中的所述信号通道的标识信息,将所述互联数据对应的所述连接器确认为与所述数据包中标识信息对应的连接器通过线缆相连接,并记录入所述矩阵表格中。

[0010]

优选地,其中,所述控制器通过一控制接口和一配置接口同时与所述可编程逻辑阵列相连接。

[0011]

优选地,其中,所述数据包中还包括包头和计数器,所述计数器用以表征组网的稳定性。

[0012]

一种组网检测系统,应用于基于可编程逻辑阵列的原型验证系统,其中,包括多个系统单板和一上位机,所述上位机分别与所述系统单板通信连接;所述系统单板包括一控制器和与所述控制器连接的多个可编程逻辑阵列,每个所述可编程逻辑阵列包括多个连接器,每个所述连接器中包括多个信号通道,所述连接器之间通过排线将所述信号通道对应连接,所述信号通道用于接收和发送信号;所述上位机还包括:分配单元,用于为每个所述系统单板、所述可编程逻辑阵列以及所述信号通道分配标识信息,其中,所述信号通道的标识信息中包括所述系统单板的标识信息和所述可编程逻辑阵列的标识信息;发送单元,连接所述分配单元,用于将所述标识信息发送给对应的所述控制器;所述控制器还包括:设置单元,用于将所述信号通道统一设置为接收信号模式;检测单元,用于依次检测所述信号通道是否接收到一数据包;切换单元,连接所述检测单元,将未接收到所述数据包的所述信号通道切换为发送信号模式,并通过该信号通道发送所述数据包,其中所述数据包中包括所述信号通道的标识信息和校验码;采集单元,用于采集每个所述信号通道的标识信息和对应信号通道接收的所述数据包以生成一互联数据,并将所述互联数据发送至所述上位机;所述上位机还包括处理单元,用于根据所述互联数据处理得到互联信息,生成单元,连接所述处理单元,用于根据所述互联信息和硬件系统描述语言模板自动生成用于描述组网连接的硬件系统描述语言文件。

[0013]

优选地,其中,所述处理单元进一步包括:读取模块,用于依次读取所述互联数据;判断模块,连接所述读取模块,用于判断所述互联数据中是否存在所述数据包,并输出一判断结果;记录模块,连接所述判断模块和所述读取模块,于所述判决结果表示不存在时,将所述互联数据对应的所述信号通道确认为没有线缆连接,并记录入一矩阵表格中,于所述判决结果表示存在时,读取所述数据包中的所述信号通道的标识信息,将所述互联数据对应的所述信号通道确认为与所述数据包中标识信息对应的信号通道通过线缆相连接,并记录入

所述矩阵表格中;校验模块,连接所述记录模块和所述读取模块,读取所述数据包中所述校验码,并于所述校验码出现错误时确认为线缆短路或连接质量不佳,并记录入所述矩阵表格中。

[0014]

优选地,其中,对每个所述连接器中仅选取其中一个所述信号通道进行检测,生成对应于每个连接器的所述互联数据;判断所述互联数据中是否存在所述数据包:若不存在,则将所述互联数据对应的所述连接器确认为没有线缆连接,并记录入所述矩阵表格中;若存在,则读取所述数据包中的所述信号通道的标识信息,将所述互联数据对应的所述连接器确认为与所述数据包中标识信息对应的连接器通过线缆相连接,并记录入所述矩阵表格中。

[0015]

优选地,其中,所述控制器通过一控制接口和一配置接口同时与所述可编程逻辑阵列相连接。

[0016]

优选地,其中,所述数据包中还包括包头和计数器,所述计数器用以表征组网的稳定性。

[0017]

上述技术方案的有益效果在于:提供一种组网检测方法及系统,以实现各连接器及信号通道之间的互联检测,并自动生成硬件系统描述语言文件,无需人工手动测量和输入,不受开发板安装环境的限制,生成速度快且精度高。同时,互联检测的过程中同时可以精确判断线缆是否存在短路或连接质量不佳等问题,并对出现故障的线缆进行精确定位。

附图说明

[0018]

为了更清楚地说明本申请实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

[0019]

图1为本发明的较佳实施例中,一种组网检测系统的结构示意图;图2为本发明的较佳实施例中,一种组网检测方法的步骤流程示意图;图3为本发明的较佳实施例中,于图2的基础上,步骤s7的分步骤流程示意图;图4为本发明的较佳实施例中,上位机的内部结构示意图;图5为本发明的较佳实施例中,控制器的内部结构示意图;图6为本发明的较佳实施例中,处理单元的内部结构示意图。

具体实施方式

[0020]

下面结合附图对本申请实施例进行详细描述。

[0021]

以下通过特定的具体实例说明本申请的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本申请的其他优点与功效。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。本申请还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本申请的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可

以相互组合。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

[0022]

要说明的是,下文描述在所附权利要求书的范围内的实施例的各种方面。应显而易见,本文中所描述的方面可体现于广泛多种形式中,且本文中所描述的任何特定结构及/或功能仅为说明性的。基于本申请,所属领域的技术人员应了解,本文中所描述的一个方面可与任何其它方面独立地实施,且可以各种方式组合这些方面中的两者或两者以上。举例来说,可使用本文中所阐述的任何数目个方面来实施设备及/或实践方法。另外,可使用除了本文中所阐述的方面中的一或多者之外的其它结构及/或功能性实施此设备及/或实践此方法。

[0023]

还需要说明的是,以下实施例中所提供的图示仅以示意方式说明本申请的基本构想,图式中仅显示与本申请中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

[0024]

另外,在以下描述中,提供具体细节是为了便于透彻理解实例。然而,所属领域的技术人员将理解,可在没有这些特定细节的情况下实践所述方面。

[0025]

本申请所公开的内容适合采用lvds/sstl/lv lvcmos/ttl等各种数字io互联的fpga组网检测,包含单端或者差分方式。

[0026]

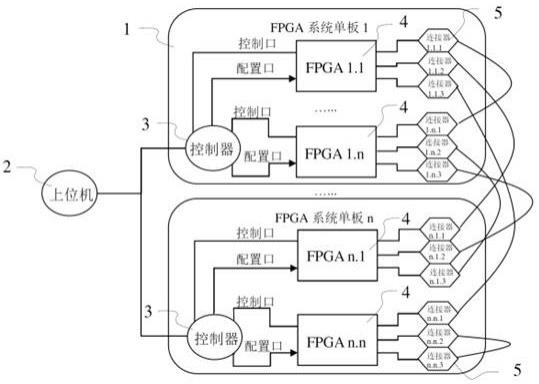

一种组网检测方法,应用于基于可编程逻辑阵列4的原型验证系统,如图1所示,其中原型验证系统包括多个系统单板1和一上位机2,上位机2分别与系统单板1通信连接;系统单板1包括一控制器3和与控制器3连接的多个可编程逻辑阵列4,每个可编程逻辑阵列4包括多个连接器5,每个连接器5中包括多个信号通道,连接器5之间通过排线将信号通道对应连接,信号通道用于接收和发送信号;具体的,原型验证系统包含上位机2,fpga系统单板1,可编程逻辑阵列4,连接器5,以及连接器5上的信号通道共5个层次。每个信号通道均具备输入和输出两种模式,且可以在控制器3的控制下在两种模式间自由的切换。输入模式用于接收信号,输出模式则用于向外发送信号。

[0027]

在本发明的一个具体实施例中,每个连接器5内包括多个信号通道,即io通道,所有连接器5包括的信号通道的数量相同,排列顺序也都一样,在通过排线将两个连接器5互相连接时,各信号通道之间也是对应的连接。每个可编程逻辑阵列4上又包括多个连接器5,每个系统单板1上设置有多个可编程逻辑阵列4。上位机2可以采用计算机、服务器、工控机或者mcu来实现。

[0028]

如图2所示,本申请所公开的组网检测方法还包括以下步骤:步骤s1,上位机2为每个系统单板1、可编程逻辑阵列4以及信号通道分配标识信息,并将标识信息载入对应的控制器3;其中,信号通道的标识信息中包括系统单板1的标识信息和可编程逻辑阵列4的标识信息;在本发明的一个具体实施例中,设计一个检测专用的程序文件,并将该逻辑程序文件通过上位机2、控制器3下载到各可编程逻辑阵列4中,以实现独立控制每个信号通道收发数据的功能。随后,上位机2依次对系统中的组件进行编号,首先对系统单板1进行编号,再以

系统单板1的编号为依据对单板内的可编程逻辑阵列4进行编号,最后对每个连接器5以及连接器中的信号通道进行编号。因此每个信号通道的编号就包括了:系统单板1编号+fpga编号+连接器5编号+信号通道编号,从而组成唯一的标识信息,且信号通道的标识信息中可以获取该信号通道所属的系统单板1、可编程逻辑阵列4及连接器5的信息。

[0029]

步骤s2,将信号通道统一设置为接收信号模式;步骤s3,检测信号通道是否接收到一数据包:若是,则切换至下一信号通道并返回步骤s3;若否,则转向步骤s4;步骤s4,将当前信号通道切换为发送信号模式,并通过该信号通道发送数据包,随后切换至下一信号通道并返回步骤s3,其中数据包中包括信号通道的标识信息和校验码;步骤s5,重复步骤s3至步骤s4,直至所有的信号通道均检测完毕后转向步骤s6;在本发明的一个具体实施例中,每个信号通道还包括一寄存器、一接收器和一发送器,控制器3从上位机2下载到信号通道的标识信息即编号后,将编号对应存储到相应的信号通道寄存器中,随后,控制器3统一将所有的信号通道配置为输入模式,使得接收器准备接收信号,并对接收器进行复位,清楚所有数据。

[0030]

进入检测程序以后,上位机2发送相关的指令,控制器3通过可编程逻辑阵列4内在控制逻辑实现如下功能。首先检测一信号通道的接收器中是否接收到数据包,如果接收器中已经存在了数据包,可以认为该信号通道已经通过线缆接收到了来自其他信号通道发送的数据包,进而可以认为该信号通道与发送数据包的信号通道是连通的。则跳过该信号通道的检测,进行下一信号通道的检测。如果没有接收到,说明该通道无法确定是否通过线缆与其他信号通道连接,此时,控制器3将该信号通道由接收模式转换为发送模式,此时发送器构建一包含信号通道标识信息和校验码在内的数据包,并将该数据包进行发送。由于此时其他信号通道均处于接收信号状态,因此,如果该信号通道通过线缆与其他信号通道存在连接,则与之相连的信号通道的接收器便会收到该数据包。根据上述方法依次对所有的信号通道进行检测,直到所有的信号通道均检测结束后,进入下一步。

[0031]

步骤s6,控制器3采集每个信号通道的标识信息和对应信号通道接收的数据包以生成一互联数据,并将互联数据发送至上位机2;具体的,在本实施例中,全部信号通道检测完毕后,上位机2发指令,控制器3通过可编程逻辑阵列4内的控制逻辑把每个连接器5中的信号通道的接收信息进行收集打包成互联数据,发送至上位机2进行处理分析。

[0032]

步骤s7,上位机2根据互联数据处理得到互联信息;步骤s8,根据互联信息和硬件系统描述语言模板自动生成用于描述组网连接的硬件系统描述语言文件。

[0033]

具体的,在本实施例中,根据收集到的互联数据生成互联信息,并将互联信息填充进入硬件描述语言模板中,以自动生成硬件描述语言文件,其中,连接器5体现为总线信号类型。上位机2软件在获取该硬件描述语言文件后可以快速调用,进行后续设计和仿真,大大提高了开发效率。

[0034]

在本发明的较佳实施例中,如图3所示,步骤s7进一步包括:步骤s70,依次读取互联数据,并判断互联数据中是否存在数据包:

若不存在,则将互联数据对应的信号通道确认为没有线缆连接,并记录入一矩阵表格中;若存在,则转向步骤s71;步骤s71,读取数据包中的信号通道的标识信息,将互联数据对应的信号通道确认为与数据包中标识信息对应的信号通道通过线缆相连接,并记录入矩阵表格中;步骤s72,读取数据包中校验码,并于校验码出现错误时确认为线缆短路或连接质量不佳,并记录入矩阵表格中;步骤s73,重复步骤s70至步骤s72,直至所有互联数据均处理完毕后转向步骤s74;步骤s74,将生成的矩阵表格输出为互联信息。

[0035]

具体的,在本实施例中,对每个信号通道对应的互联数据依次进行处理,并将处理结果填入矩阵表格中,其中矩阵表格为以每个信号通道编号作为横、纵坐标的表格,在两个信号通道编号交汇的空格中填入连接信息以及信号质量信息,从而记录各信号通道之间的互联关系,以及连接的质量。

[0036]

数据包中包含一校验码,上位机2会对接收到的数据包中的校验码进行校验,如果校验码出错,则认为两个通过线缆连接的信号通道可能存在断路或者信号质量不佳的情况,用户可以根据该校验信息直接定位到具体的线缆进行物理检查与修正,实现了对故障线缆精确定位的功能。

[0037]

在本发明的较佳实施例中,对每个连接器5中仅选取其中一个信号通道进行步骤s3至步骤s4的检测,生成对应于每个连接器5的互联数据;判断互联数据中是否存在数据包:若不存在,则将互联数据对应的连接器5确认为没有线缆连接,并记录入矩阵表格中;若存在,则读取数据包中的信号通道的标识信息,将互联数据对应的连接器5确认为与数据包中标识信息对应的连接器5通过线缆相连接,并记录入矩阵表格中。

[0038]

具体的,在本实施例中,由于连接器5之间是通过排线的方式整体连接,因此,在无需判断连接器5内每个信号通道之间线缆连接好坏的情况下,可以仅仅以连接器5中一个信号通道作为代表进行检测,如果该信号通道与另一信号通道连通,则认为该信号通道所在的连接器5与另一信号通道所在的连接器5相连接。在此实施例中,以连接器5作为最小连接单位,而管脚的约束文件可以根据连接器5和电路板的信息,得到其他信号通道的管脚约束。本实施例可以提升检测速度。

[0039]

在本发明的较佳实施例中,控制器3通过一控制接口和一配置接口同时与可编程逻辑阵列4相连接。

[0040]

具体的,在本实施例中,控制器3和每个可编程逻辑阵列4均有两组连接,第一组连接为下载配置用的专用连接端口,第二组连接为控制用的双向端口,控制器3还通过一上行端口与上位机2连接,该上行端口可以是以太网端口、rs-485端口或者usb端口中的一种。

[0041]

在本发明的较佳实施例中,数据包中还包括包头和计数器,所述计数器用以表征组网的稳定性。

[0042]

具体的,在本实施例中,数据包由包头、标识信息、计数器和校验码四块组成,数据具有自同步功能,使得包头很容易被识别出来,数据自同步的方法为现有技术,在此不再赘述。在每发送一个数据,计数器都会加一,接收端如果检测到前后接收的包计数器不连续,

则认为发生了一次数据传递错误,最后根据错误数总和与所有发的数据包的总和来计算得到误码率,进而来表征组网的稳定性。

[0043]

一种组网检测系统,应用于基于可编程逻辑阵列4的原型验证系统,如图1所示,其中包括多个系统单板1和一上位机2,上位机2分别与系统单板1通信连接;系统单板1包括一控制器3和与控制器3连接的多个可编程逻辑阵列4,每个可编程逻辑阵列4包括多个连接器5,每个连接器5中包括多个信号通道,连接器5之间通过排线将信号通道对应连接,信号通道用于接收和发送信号;如图4所示,上位机2还包括:分配单元20,用于为每个系统单板1、可编程逻辑阵列4以及信号通道分配标识信息,其中,信号通道的标识信息中包括系统单板1的标识信息和可编程逻辑阵列4的标识信息;发送单元21,连接分配单元20,用于将标识信息发送给对应的控制器3;如图5所示,控制器3还包括:设置单元30,用于将信号通道统一设置为接收信号模式;检测单元31,用于依次检测信号通道是否接收到一数据包;切换单元32,连接检测单元31,将未接收到数据包的信号通道切换为发送信号模式,并通过该信号通道发送数据包,其中数据包中包括信号通道的标识信息和校验码;采集单元33,用于采集每个信号通道的标识信息和对应信号通道接收的数据包以生成一互联数据,并将互联数据发送至上位机2;上位机2还包括处理单元22,用于根据互联数据处理得到互联信息,生成单元23,连接处理单元22,用于根据互联信息和硬件系统描述语言模板自动生成用于描述组网连接的硬件系统描述语言文件。

[0044]

作为优选的实施方式,每个可编程逻辑阵列中都有一个对应的硬件描述文件,例如:module fpga(

ꢀꢀꢀꢀ

inout[63:0] connector1;

ꢀꢀꢀꢀꢀ

inout[63:0] connector2)一个顶层硬件描述文件,例如:module system_top()fpga fpga1(connector1(con1_1),connector2(con1_2));fpga fpga2(connector1(con2_1),connector2(con2_2));

……

fpga fpgan(connector1(conn_1),connector2(conn_2));根据检测的互联矩阵,做连线,实现输出到输入的连接,例如:assign con1_1 = con2_2。

[0045]

在本发明的较佳实施例中,如图6所示,处理单元22进一步包括:读取模块220,用于依次读取互联数据;判断模块221,连接读取模块220,用于判断互联数据中是否存在数据包,并输出一判断结果;

记录模块222,连接判断模块221和读取模块220,于判决结果表示不存在时,将互联数据对应的信号通道确认为没有线缆连接,并记录入一矩阵表格中,于判决结果表示存在时,读取数据包中的信号通道的标识信息,将互联数据对应的信号通道确认为与数据包中标识信息对应的信号通道通过线缆相连接,并记录入矩阵表格中;校验模块223,连接记录模块222和读取模块220,读取数据包中校验码,并于校验码出现错误时确认为线缆短路或连接质量不佳,并记录入矩阵表格中。

[0046]

在本发明的较佳实施例中,对每个连接器5中仅选取其中一个信号通道进行检测,生成对应于每个连接器5的互联数据;判断互联数据中是否存在数据包:若不存在,则将互联数据对应的连接器5确认为没有线缆连接,并记录入矩阵表格中;若存在,则读取数据包中的信号通道的标识信息,将互联数据对应的连接器5确认为与数据包中标识信息对应的连接器5通过线缆相连接,并记录入矩阵表格中。

[0047]

在本发明的较佳实施例中,控制器3通过一控制接口和一配置接口同时与可编程逻辑阵列4相连接。

[0048]

在本发明的较佳实施例中,数据包中还包括包头和计数器,所述计数器用以表征组网的稳定性。

[0049]

上述技术方案的有益效果在于:提供一种组网检测方法及系统,以实现各连接器及信号通道之间的互联检测,并自动生成硬件系统描述语言文件,无需人工手动测量和输入,不受开发板安装环境的限制,生成速度快且精度高。互联检测的过程中同时可以精确判断线缆是否存在短路或连接质量不佳等问题。

[0050]

以上所述,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1