一种单芯片全差分结构的LVDT转换电路与方法与流程

为va+ vb,电压信号va与“和值”的比值代表位移量行程k的大小,当lvdt传感器在机械零位,即va=vb=(va+ vb)/2时位移行程量k为0.5;电压信号va、vb输入差分结构的线性分段电路、差分r_2r dac电路后与计数电路中代表lvdt数字位移行程量k,合成一个差分误差信号(1

‑

k)

×

va

‑

k

×

vb,误差信号经过相敏解调电路、差分到单端转换电路、内置参数积分电路、压控振荡电路和计数电路,最后数字位移量k在线性分段电路、差分r_2r dac电路中与模拟位移量k比较组成的一个闭环回路,寻找误差信号(1

‑

k)

×

va

‑

k

×

vb的零点,当这一过程完成时,数字控制电路的数字量k等于信号输入k,最后输出数字k;数字位移量k由二进制码bit1~bit16表示,其中最高位bit1和次高位bit2用于传感器位移满量程溢出数字量标志,当bit1、bit2为01时为上限溢出,为11时是下限溢出;bit3~bit16是二进制码的lvdt数字位移行程量k,其中bit3代表1/2行程的权值,bit4代表1/4行程(k/4)的权值,依次类推,bit16代表1/214行程的权值;即,当lvdt为负满行程时, bit3~bit16为全0,当lvdt为正满行程时, bit3~bit16为全1。

8.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的单芯片全差分结构的lvdt转换方法,该方法高位采用线性分段电路、低位采用r_2r dac电路,进行信号的粗分、细分处理;lvdt转换电路与r/d转换器的固态控制变压器不同,在r/d转换器的固态控制变压器中对粗分电路修调,即在45

°

,22.5

°

,11.25

°

、5.625

°

修调,细分角度成线性关系,在0

°

~ 360

°

范围内逼近正余弦曲线;而lvdt转换器中粗分电路采用线性分段,在对应位移行程量的1/2,即对应电压信号为va/(va+vb)=1/2、va/(va+vb)=1/4、va/(va+vb)=1/8、电压信号为va/(va+vb)=1/16的特殊点进行线性等比分压;通过等值的差分结构的两组电阻,对输入的交流信号进行分压,最终将位移行程量范围由0~1粗分到0~1/16,细分电路由r_2r dac电路对0~1/16位移行程量进行比较,实现lvdt转换。

9.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的单芯片全差分结构的lvdt转换方法,lvdt转换在高位线性分段后,采用全差分增益补偿方法:在粗分电路中信号经过一级分压后,信号的幅值缩小为原来的1/2,采用差分结构放大补偿,在电压信号的va/(va+vb)=1/4分段点,将分压电压放大2倍,全差分结构由两个相同的运放大器、两个反馈电阻rf及一个共用的放大电阻ra组成差分放大电路,放大关系为au=1+2rf/ra,通过将反馈电阻rf设置为r,共用的放大电阻ra设置为2r,即通过整数比实现2倍放大关系,同时反馈电阻、放大电阻之间没有引入地线上的阻抗。

10.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的单芯片全差分结构的lvdt转换方法,由两路完全相同的r_2r dac电路实现全差分结构的r_2r dac电路,进行细分处理,其中,一路r

‑

2r dac的输入端接粗分电路输出的差分信号的两个正端、一路r

‑

2r dac的输入端接粗分电路的差分信号的两个负端;全差分信号经过相敏解调,经过差分转单端电路变为单端信号,经过积分器连接压控振荡器电路,压控振荡器采用复位式电路结构,由运算放大器与电阻、电容组成,运算放大器的输出高于3.25v或低于1.25v时,输出高电平,通过单稳态电路输出时钟信号,控制复位开关闭合,使压控振荡器复位,积分器主电路与压控振荡器组成ⅱ型闭环伺服回路,由

于ⅱ型闭环伺服回路易产生不稳定,即有一个lsb的误差电压量值在零位上下变化,通过将压控振荡器的输出按比例反馈到积分器的输入端,设置积分器的阈值区间,使之在1lsb范围内保留误差值,而使积分电路的输出为零,直至输入误差超过了1lsb对应值,才有1lsb的变化,实现1个lsb的迟滞。

11.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的单芯片全差分结构的lvdt转换方法,通过bit信号消除180

°

假零位现象,可逆计数器电路组成ⅱ型闭环系统,计数器的输出连接到粗分电路及r

‑

2r dac电路,lvdt的激磁是正弦信号,采用内部检测信号bit电路,检测参考和信号的相移,当相移超过45

°

时,bit信号为低电平,在正常情况下为高电平;bit信号与计数器的第9位bit9进行异或后,接差分r

‑

2r dac电路的第4位,当bit信号为0时,r

‑

2r dac电路的第4位由计数器的第9位bit9控制,转换电路正常工作;当bit信号为1时,r

‑

2r dac电路的第4位是计数器的第9位bit9取反,造成转换电路中的误差增大,转换电路的压控振荡器产生振荡信号,转换电路重新跟踪外部信号,直到消除180

°

假零位。

12.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的单芯片全差分结构的lvdt转换方法,通过计时方法计算内参考与外参考的相位差,当相位差大于45

°

时,输出bit信号;外参考rh、rl通过比较器,产生外参考方波信号re,信号va、vb通过选择器再经过比较器产生内参考方波信号ri,选择器的选择信号为计数器的bit3,外参考方波信号re与内参考方波信号ri异或实现相位差eφ检测;在外参考方波信号re的中点处,通过中点产生电路采样外参考方波信号re与内参考方波信号ri相位差eφ,产生bit信号。

13.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的单芯片全差分结构的lvdt转换方法,计数器输出的并行数据bit1~bit16,连接到数据选择器及d触发器组成的移位寄存器电路,通过禁止信号实现移位寄存器的置数功能,将16位并行数字量转换为串行spi信号;移位寄存器的时钟cp为串行接口时钟,禁止信号inh为高电平时,d触发器清零,串行接口时钟cp经过延时后,接d触发器的时钟端cd触发器的输出q作为数据选择器的选择信号sel;当禁止信号inh为低电平时,d触发器输出零,数据选择器置入选择数据bit1~bit16,在串行接口时钟cp的第1个时钟,d触发器输出高电平,数据选择器选择移位数据,实现移位功能。

14.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的单芯片全差分结构的lvdt转换方法,可编程激磁源电路包括积分式分频电路、正弦rom查找表、d/a转换电路和运放电路,实现1k~10khz的可编程频率,由内部产生1mhz时钟信号,同时设定置频率控制信号fs5~fs0,作为分频电路的分频数值对1mhz时钟进行分频;积分式分频电路的计数数据位为8位,rom的地址信号为7位,与分频电路的计数数据位的低7位连接,rom表数据的位宽为7位,数据为0

°

~180

°

内的正弦数据,通过r_2r dac电路、运算放大电路转换为正弦波模拟信号,运算放大电路由分频电路的计数数据位的第8位控制进行同相或反相放大,实现0

°

~360

°

内变化的正弦信号。

15.与现有技术相比,本发明能有效地消除了转换电路中的抖码问题,并且具有外围

电路简单、抗干扰能力强等优点。

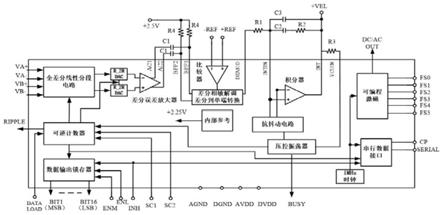

附图说明

16.图1为本发明的转换原理图;图2为本发明的全差分线性分段电路图;图3为本发明的全差分增益补偿电路图;图4为本发明的差分r

‑

2r dac电路图;图5为本发明的差分转单端电路图;图6为本发明的压控振荡器电路图;图7为本发明的积分器及抗1lsb抖动电路图;图8为本发明的防止180

°

假零位电路图;图9为本发明的内外参考相位求差电路电路图;图10为本发明的脉冲中点产生电路图;图11为本发明的串行接口电路图;图12为本发明的可编程激磁源电路图。

具体实施方式

17.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

18.参照图1,一种单芯片全差分结构的轴角转换电路,具有频率可编程内置激磁电路,采用二阶伺服闭环控制回路,自动跟踪输入模拟位置量,并输出并行及串行数字量。该电路包括全差分电路结构的线性分段电路,线性分段电路依次与全差分电路结构的r_2r dac电路、误差放大电路、相敏解调电路、差分到单端转换电路连接,再通过积分器与压控振荡电路和计数电路连接,计数器输出代表lvdt的位置的数字量,计数电路与串行spi输出接口电路连接,将16位并行数字量转换为串行信号输出,同时计数电路则分别与固态控制变压器、r_2r dac电路连接,实现闭环跟踪;该电路还包括满量程数字量溢出标志,数字输出量bit1~bit16的最高位bit1和次高位bit2用于传感器位移满量程溢出数字量标志,当bit1、bit2为01时为上限溢出,为11时是下限溢出;该电路还包括积分式分频电路,产生频率可编程激磁信号;该电路还包括bit电路,通过检测参考与信号的相位差,防止转换电路出现180

°

假零位;该电路还包括抗抖动电路,通过将压控振荡电路的输出电压信号按比例反馈到积分器电路,实现1个lsb的迟滞,提高电路的稳定性;下面进行具体阐述:1、全差分线性比值分段电路如图2所示,全差分线性全差分线性比值分段电路由模拟开关、电阻、运算放大器

组成;在交流信号激励下,外部的线性差动式位移传感器lvdt产生一个位移行程量k,位移量k分为va和vb两组差分交流电压信号(va+和vb +,va

‑

和vb

ꢀ‑

)。其中电压信号有效值的“和值”(va+ vb)是固定值,电压信号va与“和值”(va+ vb)的比值代表位移量行程k的大小;lvdt传感器的电压信号va+和vb +,va

‑

和vb

ꢀ‑

两组信号,通过开关g1~g10控制,采用线性分段,在对应位移行程量的1/2(a/(a+b)=1/2)、1/4(a/b=1/3)、1/8(a/b=1/7)、1/16(a/b=1/15)的特殊点进行线性等比分压;最终形成ac+和ac

‑

两组差分信号,其中输出out1是va,out2是(va+vb)/16

‑

va;out1+、out1

‑

和out1+、out1

‑

,再输入后端的r_2r dac中进行比较;2、全差分增益补偿电路在粗分电路中信号经过一级分压后,信号的幅值缩小为原来的1/2;为了提高电路的灵敏度,并满足转换电路的开环增益,需要补偿信号的幅值。如图3所示,采用差分结构放大补偿,在k=1/4分段点,将分压电压放大2倍;全差分结构由两个相同的运放大器、两个反馈电阻rf及一个共用的放大电阻ra组成差分放大电路,放大关系为au=(1+2rf/ra);通过将反馈电阻rf设置为r,共用的放大电阻ra设置为2r。即通过整数比实现2倍放大关系,同时反馈电阻、放大电阻之间没有引入地线上的阻抗,提高了放大精度;3、差分r

‑

2r dac电路差分r

‑

2r dac如图4所示;在图2中,最终的输出是两路差分信号out1+、out1

‑

和out2+、out2

‑

,需要采用差分的r

‑

2r dac进行细分线性处理;其中r

‑

2r dac1的v1、v2分别接全差分粗分电路输出的out2+、out1+,其中r

‑

2r dac2的v1、v2分别接全差分粗分电路输出的out2

‑

、out1

‑

;输出信号为iout+和iout

‑

;4、差分转单端电路全差分信号经过相敏解调,经过差分转单端电路变为单端信号。差分转单端电路如图5所示,由运算放大器及电阻r1、r2、r3、r4组成,电阻r1=r3,r2=r4,电阻r4的一端接共模电位2.25v;in+、in

‑

是输入的差分信号,经过差分转单端电路后,输出变为单端信号,输出的电压为out=(in+)

‑

(in

‑

);5、压控振荡器电路压控振荡器采用复位式电路结构,如图6所示,由运算放大器a1、比较器a2和a3、电阻r1、电容c1、开关1及单稳态电路和门电路组成;运算放大器a1与电阻r1、电容c1组成积分电路。比较器a2的负端接3.25v,a3的正端接1.25v;因此,当运算放大器a1的输出高于3.25v或低于1.25v时,门电路输出高电平,单稳态电路输出脉冲信号clk,信号clk控制开关k1闭合,使运算放大器a1组成的积分电路复位;当运算放大器a1的输出vco_out低于3.25v并高于1.25v时,门电路输出低电平,单稳态电路输出为低电平;比较器a4输出方向信号,实现可逆计数器的加/减控制;6、积分器及抗1lsb抖动电路积分器主电路是个可校正的普通积分器;由于二阶无差度伺服回路易产生静不稳定,即有一个lsb(最低有效位)的量值在零位上下变化误差电压的符号;通过将压控振荡器的输出按比例反馈到积分器的输入端,设置积分器的的阈值区间,使之在1lsb范围内保留误差值,而使积分器输出为零,直至输入误差超过了1lsb对应值,才有1lsb的变化;电路图如图7所示;运算放大器a2、a3与电阻r1~r5组成抗1lsb抖动电路;输入信号

为图6中的压控振荡器输出vco_out,通过电阻r5,产生抗1lsb的电流信号;运算放大器a3与电阻r6、r7、c1、c2组成积分电路,其中电阻r7与电容c1组成带宽选择电路;7、防止180

°

假零位电路由于lvdt的激磁是正弦信号,为了防止转换电路的出现180

°

假零位,采用内部检测信号bit(build_in test)信号电路,检测参考和信号的相移,当相移超过45

°

时,bit信号为低电平,在正常情况下为高电平;如图8所示,bit信号与计数器的第9位bit9进行异或后,接差分r

‑

2r dac电路的第4位;当bit信号为0时,r

‑

2r dac电路的第4位由计数器的第9位bit9控制,转换电路正常工作。当bit信号为1时,r

‑

2r dac电路的第4位是计数器的第9位bit9取反,造成转换电路中的误差增大,转换电路的压控振荡器产生振荡信号,转换电路重新跟踪外部信号,直到消除180

°

假零位;8、内部检测信号bit(build_in test)信号电路相位求差电路如图9所示,通过计时方法计算内参考与外参考的相位差,当相位差大于45

°

时,输出bit信号;外参考rh、rl通过比较器,产生外参考方波信号re。信号va、vb通过选择器再经过比较器产生内参考方波信号ri,选择器的选择信号为计数器的bit3;外参考方波信号re与内参考方波信号ri异或实现相位差eφ检测;在外参考方波信号re的中点处,通过中点产生电路采样外参考方波信号re与内参考方波信号ri相位差eφ,产生bit信号;由于外参考方波信号re的频率是固定值,通过边沿检测电路产生的脉冲频率相等,采用计数器采样前2个脉冲的时间,在之后的时间中点上产生一个脉冲;具体实现电路框图如图10所示;其中时钟信号频率为1mhz,计数器由14个d触发器组成,满足激磁频率为1khz到10khz的频率要求;将中点产生电路产生的中点脉冲来做bit信号的检测时钟,可保证在相位差大于45

°

,参考最大值时检测bit信号,从而提高了bit信号的准确性;9、串行接口电路计数器输出的并行数据bit1~bit16,连接到数据选择器及d触发器组成的移位寄存器电路。通过禁止信号(inh)实现移位寄存器的置数功能,将16位并行数字量转换为串行spi信号;如图11所示,移位寄存器的时钟cp为串行接口时钟,禁止信号inh为高电平时,d触发器清零,串行接口时钟cp经过延时后,接d触发器的时钟端cd触发器的输出q作为数据选择器的选择信号sel;当禁止信号inh为低电平时,d触发器输出零,数据选择器置入选择数据bit1~bit16,在串行接口时钟cp的第1个时钟,d触发器输出高电平,数据选择器选择移位数据,实现移位功能;10、可编程激磁源电路如图12所示,激磁电源由积分式分频电路、正弦rom查找表、d/a转换电路、运放电路组成,实现1k~10khz的可编程频率。由内部产生1mhz时钟信号,同时设定置频率控制信号fs5~fs0,作为积分式分频电路的分频数值对1mhz时钟进行分频,分频电路的计数数据位为

8位,rom的地址信号为7位,与分频电路的计数数据位的低7位连接。rom表产生正弦数据位宽为7位,数据为0

°

~180

°

内的正弦数据,通过r_2r dac电路、运算放大电路转换为正弦波模拟信号;其中运算放大电路由分频电路的计数数据位的第8位控制同相或反相放大,实现0

°

~360

°

内变化的正弦信号。

19.参考图1

‑

12,一种单芯片全差分结构的lvdt转换方法,在交流信号激励下,外部的线性差动式位移传感器lvdt产生一个位移行程量k,位移量k分为va和vb两组差分交流电压信号(va+和vb +,va

‑

和vb

ꢀ‑

);其中电压信号有效值的“和值”(va+ vb)是固定值,电压信号va与“和值”(va+ vb)的比值代表位移量行程k的大小;电压信号va、vb输入差分结构的线性分段电路、r_2r dac电路后与计数电路中代表lvdt数字位移行程量k,合成一个差分误差信号(1

‑

k)

×

va

‑

k

×

vb,误差信号经过相敏解调电路、差分到单端转换、内置参数积分电路、压控振荡电路和计数电路;最后数字位移量k在线性分段电路、r_2r dac电路中与模拟位移量k比较组成的一个闭环回路,寻找误差信号(1

‑

k)

×

va

‑

k

×

vb的零点;当这一过程完成时,数字控制电路的数字量k等于信号输入k,最后输出数字k;数字位移量k由二进制码bit1~bit16表示,其中最高位bit1和次高位bit2用于传感器位移满量程溢出数字量标志,当bit1、bit2为01时为上限溢出,为11时是下限溢出;bit3~bit16是二进制码的lvdt数字位移行程量k,其中bit3代表1/2行程的权值,bit4代表1/4行程(k/4)的权值

…

,bit16代表1/214行程的权值;即,当lvdt为负满行程时, bit3~bit16为全0,当lvdt为正满行程时, bit3~bit16为全1;在lvdt转换器中粗分电路采用线性分段,在对应位移行程量的1/2(a/(a+b)=1/2)、1/4、1/8、1/16的特殊点进行线性等比分压;通过等值的差分结构的两组电阻,对输入的交流信号进行分压;最终将位移行程量范围由(0~1)粗分到(0~1/16);细分电路由r_2r dac电路对(0~1/16)位移行程量进行比较,实现lvdt转换;在粗分电路中信号经过一级分压后,信号的幅值缩小为原来的1/2;为了提高电路的灵敏度,并满足转换电路的开环增益,需要补偿信号的幅值;采用差分结构放大补偿,在1/4分段点,将分压电压放大2倍;全差分结构由两个相同的运放大器、两个反馈电阻rf及一个共用的放大电阻ra组成差分放大电路,放大关系为au=(1+2rf/ra);通过将反馈电阻rf设置为r,共用的放大电阻ra设置为2r;即通过整数比实现2倍放大关系,同时反馈电阻、放大电阻之间没有引入地线上的阻抗,提高了放大精度;在该方法中,由两路完全相同的r_2r dac实现全差分结构的r_2r dac电路,进行细分处理,其中,一路r

‑

2r dac的输入端接粗分电路输出的差分信号的两个正端、一路r

‑

2r dac的输入端接粗分电路的差分信号的两个负端;全差分信号经过相敏解调,经过差分转单端电路变为单端信号;差分转单端电路如图5所示,由运算放大器及电阻r1、r2、r3、r4组成,电阻r1=r3,r2=r4,电阻r4的一端接共模电位2.25v。in+、in

‑

是输入的差分信号,经过差分转单端电路后,输出变为单端信号,输出的电压为out=(in+)

‑

(in

‑

);压控振荡器采用复位式电路结构,如图6所示,由运算放大器a1、比较器a2和a3、电阻r1、电容c1、开关1及单稳态电路和门电路组成;运算放大器a1与电阻r1、电容c1组成积分电路。比较器a2的负端接3.25v,a3的正端接1.25v;因此,当运算放大器a1的输出高于3.25v

或低于1.25v时,门电路输出高电平,单稳态电路输出脉冲信号clk,信号clk控制开关k1闭合,使运算放大器a1组成的积分电路复位;当运算放大器a1的输出vco_out低于3.25v并高于1.25v时,门电路输出低电平,单稳态电路输出为低电平;比较器a4输出方向信号,实现可逆计数器的加/减控制;由于ⅱ型闭环伺服回路易产生不稳定,即有一个lsb(最低有效位)的误差电压量值在零位上下变化;如图7所示,通过将压控振荡器的输出按比例反馈到积分器的输入端,设置积分器的阈值区间,使之在1lsb范围内保留误差值,而使积分电路的输出为零,直至输入误差超过了1lsb对应值,才有1lsb的变化。实现1个lsb的迟滞,提高了电路的稳定;lvdt传感器的激磁是正弦信号,为了防止转换电路的出现180

°

假零位,采用内部检测信号bit(build_in test)信号电路,检测参考和信号的相移,当相移超过45

°

时,bit信号为低电平,在正常情况下为高电平;bit信号与计数器的第9位bit9进行异或后,接差分r

‑

2r dac电路的第4位,当bit信号为0时,r

‑

2r dac电路的第4位由计数器的第9位bit9控制,转换电路正常工作;当bit信号为1时,r

‑

2r dac电路的第4位是计数器的第9位bit9取反,造成转换电路中的误差增大,转换电路的压控振荡器产生振荡信号,转换电路重新跟踪外部信号,直到消除180

°

假零位;内部检测信号bit(build_in test)信号电路通过计时方法计算内参考与外参考的相位差,当相位差大于45

°

时,输出bit信号;外参考rh、rl通过比较器,产生外参考方波信号re;信号va、vb通过选择器再经过比较器产生内参考方波信号ri,选择器的选择信号为计数器的bit3;外参考方波信号re与内参考方波信号ri异或实现相位差eφ检测;通过中点产生电路采样外参考方波信号re与内参考方波信号ri相位差eφ,产生bit信号;通过边沿检测电路产生的脉冲频率相等,采用计数器记得前2个脉冲的时间,在之后的时间中点上产生一个中点脉冲,具体实现电路框图如图10;其中时钟信号频率为1mhz,计数器由14个d触发器组成,满足激磁频率为1khz到10khz的频率要求;将中点脉冲来做bit信号的检测时钟,可保证在相位差大于45

°

,参考最大值时检测bit信号,从而提高了bit信号的准确性;计数器输出的并行数据bit1~bit16,连接到数据选择器及d触发器组成的移位寄存器电路;通过禁止信号(inh)实现移位寄存器的置数功能,将16位并行数字量转换为串行spi信号;移位寄存器的时钟cp为串行接口时钟,清零clr为禁止信号inh的反相;当禁止信号inh为高电平时,d触发器清零,串行接口时钟cp经过延时后,接d触发器的时钟端cd,触发器的输出q作为数据选择器的选择信号sel;当禁止信号inh为低电平时,d触发器输出零,数据选择器置入选择数据bit1~bit16,在串行接口时钟cp的第1个时钟,d触发器输出高电平,数据选择器选择移位数据,实现移位功能;内置可编程激磁电路由积分式分频电路、正弦rom查找表、d/a转换电路、运放电路组成,实现1k~10khz的可编程频率;全加器与d触发器组成积分式分频电路,clk是内部产生的1mhz时钟信号,积分式分频电路的输入(fs5~fs0),当(fs5~fs0)00001~11111时,积分式分频电路的输出频率变化为1khz~10khz;

积分式分频电路输出的低7位连接正弦数据rom表,数据为0

°

~180

°

内的正弦数据,输出的7位正弦数据d[6:0]接dac;分频电路输出的最高位接开关k1,当θ为0~180

°

时,运放a1为跟随状态,否则,运放a2为反相放大状态,实现θ为0~360

°

范围内的正弦信号。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1