测试电路结构及其形成方法和测试方法与流程

本发明涉及半导体制造领域,尤其涉及测试电路结构及其形成方法和测试方法。

背景技术:

1、在半导体工艺制程中,后段工艺通常用来连接单元内部各个晶体管以及单元之间的布局布线,包括金属和导电插塞等。后段工艺的缺陷对电路的影响主要有两种,一种是设计中断开的结构短路了,其原因包括原本不相连的金属因为缺陷联结起来。另一种是设计中是连接的结构断开了,其原因包括金属在加工中缺失、导电插塞与金属没有接触。因此,了解后段工艺的质量在半导体工艺中十分重要,减少制程中的缺陷可以有效提高良率,降低成本。

2、通过后段测试可以了解后段工艺的质量。后段测试需要检查的是后段金属和导电插塞,检查内容包括开路和短路。

3、在现有技术中,后段测试的测试电路为一个待测样品通过金属布线分别连接到两个衬垫上。在连接着同一样品的两个衬垫上扎入探针并施加电压,测试通过样品的电流,可以获知待测样品是开路或者短路。当所述待测样品的数量大于一个,所述待测样品的一端公用一个衬垫。

4、然而,在上述方法中,后段测试面积使用率低,在有限的探针数量的情况下,每扎入一次探针进行测试的待测样品的数量少,需要通过多次扎入探针完成所有待测样品的测试。而探针插拔次数增加会导致探针的消耗增加和探针的寿命降低。并且,每次探针移动也需要消耗时间,探针移动次数变多也会导致总测试时间增加。

技术实现思路

1、本发明解决的技术问题是提供测试电路结构及其形成方法和测试方法,在有限的探针数量的情况下提高每次测试待测样品的数量,提高后段测试面积使用率。并且,本发明减少了测试中探针插拔次数,减少了探针损耗,延长了探针寿命,减少总测试时间。

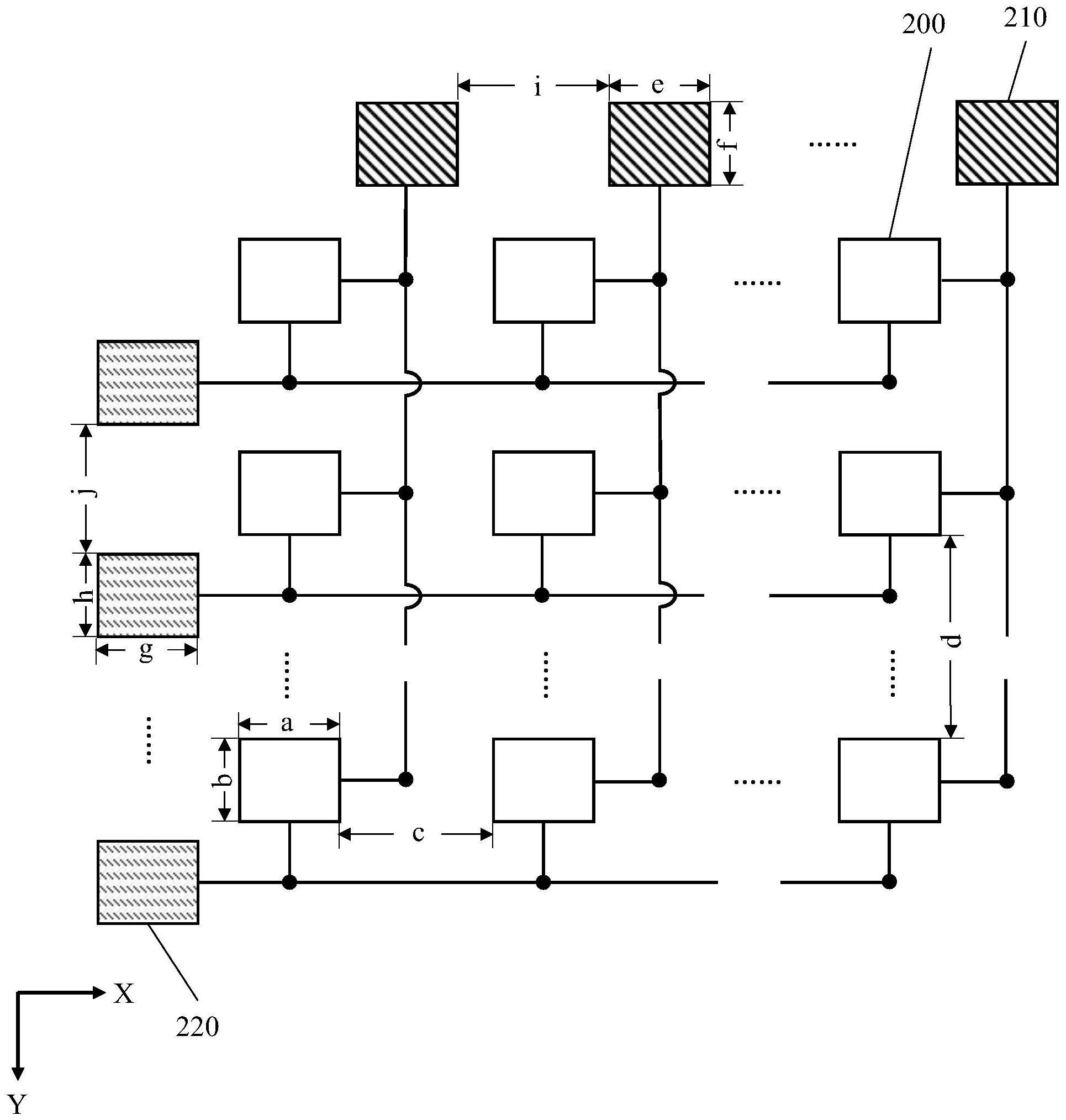

2、为解决上述技术问题,本发明的技术方案提供一种测试电路结构,包括:衬底;位于所述衬底上的若干待测样品,所述若干待测样品沿第一方向和第二方向呈阵列排布,所述第一方向和所述第二方向不同;位于所述衬底上的若干第一衬垫层,各所述第一衬垫层与沿所述第二方向的同一列待测样品电连接;位于所述衬底上的若干第二衬垫层,各所述第二衬垫层与沿所述第一方向的同一行待测样品电连接。

3、可选的,每次探针测试使用的所述第一衬垫层和所述第二衬垫层数量总和的范围包括:1个至128个。

4、可选的,所述待测样品的数量范围包括:1个至100000个。

5、可选的,各所述第一衬垫层与沿所述第二方向的同一列待测样品并联;各所述第二衬垫层与沿所述第一方向的同一行待测样品并联。

6、可选的,所述待测样品在所述第一方向上的间距为:45微米至55微米;所述待测样品在所述第二方向上的间距为:45微米至55微米。

7、可选的,所述待测样品的宽度为:35微米至45微米;所述待测样品的长度为:45微米至55微米。

8、可选的,所述第一衬垫层沿所述第一方向排布;所述第二衬垫层沿所述第二方向排布。

9、可选的,所述待测样品的结构包括:一层金属层;或者,所述待测样品的结构包括:至少两层金属层,且相邻两层金属层间具有导电插塞。

10、可选的,所述金属层的宽度为:20纳米至500纳米,所述金属层的长度为:20纳米至500纳米,所述金属层的厚度为:1纳米至500纳米;所述导电插塞的宽度为:20纳米至500纳米,所述导电插塞的长度为:20纳米至500 纳米,所述导电插塞的厚度为:1纳米至500纳米。

11、可选的,各所述第一衬垫层的宽度为:35微米至45微米;各所述第一衬垫层的长度为:45微米至55微米;各所述第二衬垫层的宽度为:35微米至 45微米;各所述第二衬垫层的长度为:45微米至55微米;所述第一衬垫层的间距为:45微米至55微米;所述第二衬垫层的间距为:55微米至65微米。

12、相应的,本发明的技术方案提供一种测试电路结构的形成方法,包括:提供衬底;在所述衬底上形成若干待测样品,所述若干待测样品沿第一方向和第二方向呈阵列排布,所述第一方向和所述第二方向不同;在所述衬底上形成若干第一衬垫层,各所述第一衬垫层与沿所述第二方向的同一列待测样品电连接;在所述衬底上形成若干第二衬垫层,各所述第二衬垫层与沿所述第一方向的同一行待测样品电连接。

13、相应的,本发明的技术方案提供一种测试电路的测试方法,包括:提供测试电路,所述测试电路包括:衬底;位于所述衬底上的若干待测样品,所述若干待测样品沿第一方向和第二方向呈阵列排布,所述第一方向和所述第二方向不同;位于所述衬底上的若干第一衬垫层,各所述第一衬垫层与沿所述第二方向的同一列待测样品电连接;位于所述衬底上的若干第二衬垫层,各所述第二衬垫层与沿所述第一方向的同一行待测样品电连接;在所述若干待测样品中获取若干实测样品,所述若干实测样品沿所述第二方向排列,且所述实测样品与若干所述第一衬垫层中的实测第一衬垫层电连接;对所述测试电路进行探针测试,所述探针测试的方法包括:在所述若干第二衬垫层上施加第一电压,在所述实测第一衬垫层上施加第二电压,所述第二电压大于所述第一电压,在所述实测第一衬垫层以外的若干第一衬垫层上施加第三电压,所述第三电压小于所述第一电压,所述第三电压的绝对值小于所述第二电压的绝对值;在所述若干第二衬垫层上施加第一电压、在所述实测第一衬垫层上施加第二电压、并在所述实测第一衬垫层以外的若干第一衬垫层上施加第三电压之后,在所述若干第二衬垫层上获取电学参数。

14、可选的,所述电学参数包括:电流。

15、可选的,所述第一电压的值为:0伏特。

16、可选的,所述第二电压值为:0.1伏特至10伏特。

17、可选的,所述第三电压值为:负0.1伏特至0伏特。

18、与现有技术相比,本发明的技术方案具有以下有益效果:

19、本发明技术方案提供的一种测试电路结构中,若干待测样品沿第一方向和第二方向呈阵列排布,各第一衬垫层与沿所述第二方向的同一列所述待测样品电连接,各第二衬垫层与沿所述第一方向的同一行待测样品电连接。因此所述第一衬垫层的数量为所述阵列的列数,所述第二衬垫层的数量为所述阵列的行数,所述待测样品的数量为所述阵列的列数与行数的乘积。在使用所述测试电路进行测试时,采用探针扎在所述衬垫层上获取电学参数。由于探针和衬垫层一一对应,因此,探针的数量就是第一衬垫层数量与第二衬垫层数量总和的上限,也就是所述阵列行数与列数总和的最大值为探针的数量。根据固定数量的探针,可以获取所述阵列的列数与行数的总和的最大值。根据所述阵列的列数与行数的总和的最大值,可以获取所述阵列的列数与行数的乘积的最大值,也就是获取所述待测器件数量的最大值。因此,在探针数量固定的情况下,可以最大化待测器件的数量。另外,每进行一次测试需要在所述衬垫层上扎入一次探针,由于本方案能够在所述探针的数量为固定时测试最大数量的待测样品,因此可以减少探针的插拔次数,进而减少移针时间和总测试时间,减少探针的消耗,延长探针的寿命。此外,对于相同的测量时间本方案可以测试更多的待测器件,因此测试获取缺陷的概率也会增大,测试更多缺陷的概率能够更有效地帮助工艺制程全面了解缺陷。综上,在探针数量固定的情况下,本方案提供的一种测试电路结构使每次测试的待测样品的数量达到最大化,从而获取更多缺陷的概率也相应提升,同时也减少了探针插拔的次数,延长探针的寿命。

20、相应的,本发明技术方案提供的一种测试电路的测试方法中,在所述实测样品所在列或行电连接的实测第一衬垫层上施加第二电压,所述第二电压的值大于0伏特;在所述实测第一衬垫层以外的第一衬垫层上施加第三电压,所述第三电压的值小于0伏特。由于在所述实测样品以外的待测样品上施加了一个负的第三电压,确保了所述实测样品以外的待测样品上的电压都低于所述实测样品的电压,在测试所述实测样品的电学参数时,所述实测样品的电学信号只来自于正的所述第二电压,并不会被所述实测样品以外的待测样品的信号所干扰。

- 还没有人留言评论。精彩留言会获得点赞!