一种数字信号处理电路辐照测试系统和辐照测试方法与流程

1.本发明属于元器件测试技术领域,特别涉及一种数字信号处理电路辐照测试系统和辐照测试方法。

背景技术:

2.随着航天事业的快速发展,人类生活已经越来越依赖航天技术。许多国家向近地环境中发射了大规模数量的航天器,各种不同用途的人造卫星为军事打击、农业、气候观测、导航、通信等领域提供了极大便捷;空间站为科学家们提供了理想的微重力实验室和宇宙研究平台;探月工程、火星探测以及遨游在太阳系边缘的各种深空探测器,让我们有机会窥探地球以外星球的奥秘,为天文学和宇宙物理学提供了大量数据支持。我国航天事业起步较晚,但发展迅速,并且后来居上。自从1970年第一颗人造卫星发射成功以来,经过40多年的技术创新和沉淀,我国目前已经逐一实现了载人航天、航天员出舱行走、长时间太空逗留等重大成就。空间探索方面,于2007年开始的嫦娥系列工程实现了绕月测绘、月球车着陆,为后续的载人登月积累了大量宝贵数据和经验。

3.数字信号处理器(digital signal processor,dsp),对比mcu、arm、fpga 等,dsp的优势在于其强大的数据处理能力和较高的运行速率。由于dsp具有小型化、能耗低、以及处理速度快、数据量大、精度高等特点,近年来,其应用已经深入到工业化的各个领域。同时,dsp在航天领域也逐渐取代传统的单片机,扮演着越来越重要的角色,其主要存在于航天器的电子系统中,在数据处理、运算、图像处理、控制等方面占据着核心地位。dsp的另一个优点是其开发通过汇编语言或者c语言实现,开发过程灵活。

4.然而,包括dsp在内的数字信号处理电路的空间应用还面临着诸多问题。航天器工作在复杂的空间环境下,即使有外壳的屏蔽,数字信号处理电路仍然承受着多种高能粒子的轰击和极端温度的考验。随着微电子技术的发展,数字信号处理电路的集成度不断变高、器件尺寸相继减小、电路复杂程度不断增大,空间应用下受空间环境影响的问题也越来越突出。辐射环境是造成半导体器件退化甚至失效的主要因素。现有的数字信号处理电路辐照测试一次只能测试一片dsp芯片,存在测试效率低下、测试精度低等问题。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种数字信号处理电路辐照测试系统和辐照测试方法,解决了现有数字信号处理电路辐照测试效率低、测试精度低的技术问题。

6.本发明采用的技术方案如下:

7.本发明提供了一种数字信号处理电路辐照测试系统,所述数字信号处理电路辐照测试系统包括fpga母板电路、dsp子板电路、上位机和电源模块,所述数字信号处理电路辐照测试系统置于辐照室中进行辐照测试;

8.所述上位机通过网口与fpga母板电路连接,上位机通过控制fpga母板电路来控制

dsp子板电路的偏置状态;

9.所述电源模块对fpga母板电路和dsp子板电路进行供电,所述电源模块采用tps54310芯片,输入电压为5v,输出电压在0.9v-3.3v之间调节;

10.所述dsp子板电路包括dsp芯片、连接器、复位电路、jtag接口、flash 以及时钟电路;所述dsp子板电路通过连接器与fpga母板电路连接;所述复位电路与dsp子板电源连接,用于监控dsp子板电源电压;flash与dsp 芯片连接,用于存储dsp芯片的初始化程序;dsp子板电路通过jtag接口与上位机连接,通过上位机将dsp芯片的初始化程序烧写到flash中;所述时钟电路与dsp芯片的时钟信号输入端连接,用于产生dsp芯片工作需要的时钟频率;

11.所述dsp子板电源包括dsp内核电源和dsp i/o电源,所述dsp内核电源为1.8v,所述dsp i/o电源为3.3v,在dsp内核电源和dsp i/o电源之间串联二极管,其中二极管阳极接dsp i/o电源,阴极接内核电源,通过二极管在正向导通时产生的管压降保证dsp内核电源的上电时间不晚于dspi/o电源。

12.进一步地,所述时钟电路包括晶体振荡器,电容和电感组成的电源滤波电路,所述电源滤波电路用于为晶体振荡器提供稳定的工作电压;晶体振荡器产生的时钟信号再经过一个33欧姆的电阻传送给dsp芯片的时钟信号输入端。

13.进一步地,所述复位电路采用max708t芯片,max708t的电源输入端与dsp i/o电源连接;当复位电路监测到dsp i/o电源低于域值电压或者 max708t芯片引脚保持低电平时,max708t芯片引脚会输出低电平,对复位电路进行复位。

14.进一步地,所述dsp芯片的信号线与fpga母板电路的连接器连接, fpga母板电路对dsp子板电路状态进行监测、静态配置和动态配置,接收 dsp子板电路的测试数据。

15.进一步地,所述fpga母板电路包括以太网接口、物理层芯片和fpga 芯片;fpga母板电路通过以太网接口与上位机连接进行通信;fpga芯片采用内部集成的mac的ip核,通过物理层芯片与以太网接口连接。

16.进一步地,所述fpga芯片外部配置有sram存储器,用于存储fpga 接收dsp子板电路的测试数据。

17.进一步地,所述sram存储器电路结构如下:

18.sr锁存器,包括晶体管t1~t4构成,用来记忆1位二进制数据;

19.门控管t5和t6,用来控制锁存器的q、q'和位线b、b'间的联系;门控管t5和t6的开关状态由字线xi的状态决定;xi=1时,门控管t5和t6导通,锁存器的q和q'端与位线b、b'接通,sram存储器输出所保存的值或接收新的赋值;xi=0时,门控管t5和t6截止,sram存储器起存储功能;

20.门控管t7和t8,配合缓冲放大器a1~a3,用于控制读/写功能,它们的状态由列地址yj来控制,yj=1时导通,yj=0时截止。

21.本发明还提供了一种数字信号处理电路辐照测试方法,所述数字信号处理电路辐照测试方法包括静态偏置总剂量测试,具体包括以下步骤:

22.步骤s11,上位机启动,fpga母板电路上电,与上位机相连接;

23.步骤s12,fpga母板电路进行初始化:

24.将编写好的代码通过烧写到fpga母板电路中,fpga母板电路对dsp 子板电路的模

式进行配置;

25.步骤s13,dsp子板电路上电,并进行初始化,将编写好的程序烧写在 dsp子板电路的flash中,dsp上电从flash中读取程序进行工作,对dsp 进行配置;

26.步骤s14,dsp子板电路进入pd3模式:

27.dsp配置结束后锁定dsp的静态偏置状态,dsp进入pd3模式,dsp 的pll的输入时钟停止产生时钟信号,所有寄存器和内部ram的内容被保留,dsp所有的功能i/o冻结为最后的状态。

28.步骤s15,dsp输入管脚的配置:

29.dsp子板电路进入pd3状态后,其内核电路的状态、输出及三态管脚的状态被锁定,上位机发送指令,使fpga按照要求,对dsp输入信号的管脚进行静态偏置,并将fpga连接器中未用的管脚设置为高阻态;

30.步骤s16,进行辐照测试:

31.dsp的静态偏置状态完成之后,将数字信号处理电路辐照测试系统放入辐照室中进行辐辐照测试,其中除dsp芯片之外的所有器件均使用铅砖进行遮挡;

32.步骤s17,上位机实时记录dsp芯片的实时状态和电流电压值,测试过程中对dsp的i/o电源和内核电源进行实时监测,将电流电压值通过上位机进行显示,并绘制成曲线。

33.进一步地,所述数字信号处理电路辐照测试方法还包括动态偏置总剂量测试,具体包括以下步骤:

34.步骤s21,上位机的启动,fpga母板电路上电;

35.步骤s22,配置fpga母板电路,定义fpga的初始功能。

36.步骤s23,fpga母板电路初始化:

37.对fpga母板电路中与dsp子板电路相连接的接口模块进行配置,以便 fpga母板电路中与dsp子板电路的各个单元信号都能进行数据交换;将动态程序提前保存fpga母板电路上的sram中,同时sram还存储dsp子板电路返回给fpga母板电路的数据;

38.步骤s24,dsp子板电路上电,并执行初始化程序:

39.初始化程序提前烧写到dsp子板电路的flash中,使dsp子板电路进入初始工作状态;

40.步骤s25,dsp子板电路执行功能程序:

41.dsp子板电路从fpga母板电路接收数据并发送到fpga,dsp芯片进行1024点fft运算,每个计算结果存储在片上数据存储区,当计算结束通过 dma把1024个计算结果搬运到外部存储区;

42.步骤s26,进行辐照测试,辐照测试期间dsp芯片一直执行动态程序, fpga母板电路将接收到的运算结果和正确的结果进行对比,将错误的数据发给上位机进行保存;

43.步骤s27,上位机记录dsp芯片实时电流电压值,并显示dsp错误的运算结果和时间。

44.本发明还提供了一种抗电磁脉冲数字信号处理电路,所述抗电磁脉冲数字信号处理电路包括所述dsp子板电路,还包括外接的抗电磁脉冲电路,所述抗电磁脉冲电路包括:第一输入端、第二输入端、第一输出端、第二输出端、第一压敏电阻、第二压敏电阻、第一气体放电管、第二气体放电管、第一电感、第二电感;

45.第一气体放电管和第二气体放电管分别串联连接在第一输入端和第二输入端之间,其连接点接地;第一压敏电阻和第二压敏电阻串联连接在第一输出端和第二输出端之间,其连接点接地;第一电感连接在第一输入端和第一输出端之间,第二电感连接在第二输入端和第二输出端之间。

46.与现有技术相比,本发明的有益效果在于,采用全自动测试,无需人员全程实时监控,减少了人员成本,提高了测试的效率和资源利用率。dsp+ fpga+上位机的分离式结构,有效地实现了dsp芯片运行状态的片外比对分析方法,排除了其他部件受到辐照影响对结果造成的干扰,实现了在测试结束后对辐照损伤部件的可拆卸替换,节约了成本。

附图说明

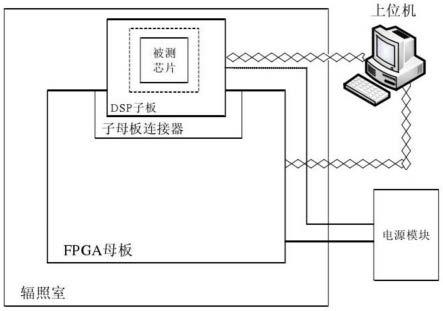

47.图1为本发明数字信号处理电路辐照测试系统结构框图;

48.图2为本发明辐照测试系统电源模块电路;

49.图3为本发明dsp电源上电顺序电路;

50.图4为本发明数字信号处理电路辐照测试系统电路框图;

51.图5为fpga网口通信示意图;

52.图6为本发明sram电路结构图;

53.图7为本发明dsp子板电路结构框图;

54.图8为flash与dsp的连接关系图;

55.图9为dsp的jtag接口关系图;

56.图10为dsp时钟发生电路图;

57.图11为dsp子板电路复位电路图;

58.图12为静态偏置总剂量测试流程图;

59.图13为动态偏置总剂量测试流程图;

60.图14为抗电磁脉冲数字信号处理电路原理图。

具体实施方式

61.以下结合说明书附图和具体实施例对本发明的具体实施方式进行进一步阐述。

62.实施例一:

63.本发明提供了一种数字信号处理电路辐照测试系统,采用子母板结构。如图1所示。fpga通过网口与上位机进行指令与数据的收发,通过连接器与 dsp连接以控制dsp的偏置状态与数据的交互。辐照测试系统的电源模块需要对fpga和dsp进行供电,dsp辐照测试过程中要对dsp的i/o电流电压进行实时监测,dsp子板电源包括dsp内核电源和dsp i/o电源,所述dsp 内核电源为1.8v,所述dsp i/o电源为3.3v。

64.电源模块采用tps54310芯片,tps54310是德州仪器生产的一款开关电源调节芯片,它能够实现低电压输入和高电流输出(输入电压范围为3v-6v,输出电压根据需要可以在0.9v-3.3v之间调节,输出电流为3a)。内部有电压误差放大器,能够提高瞬态响应条件下的工作性能。可以分别从内部或外部设置慢启动方式。其良好的电压输出特性可用于处理器/逻辑复位、故障信号检测和连续电源。

65.在辐照测试系统的电源模块中,解耦电容c1、c3电容一端并联接地,另一端与

tps54310芯片vin口连接;电阻r1一端与tps54310芯片rt口连接,另一端接地,用于设置模块的开关转换频率;电感l1一端与tps54310 芯片ph口连接,另一端与电容c2连接后接地,用于对输出电压进行滤波;电容c4一端与tps54310芯片vbias口连接,另一端接地;电容c6一端与 tps54310芯片ss/ena口连接,另一端接地;电容c5接在tps54310芯片 ph口和boot口之间;电阻r2、r3、r5,电容c7、c8、c9组成环路补偿电路,其中电容c8与电阻r5、电容c9并联,接在tps54310芯片vsense 口和comp口之间,电阻r2与电容c7、电阻r3并联,接在tps54310芯片 vsense口和ph口之间;电阻r4和电阻r2作为分压电阻,控制电源模块的输出电压,具体如下:

[0066][0067]

其中v

out

为输出电压。

[0068]

输入电压的典型值是5v,r4取3.7kω,r5取3.7kω,计算得出dsp 的i/o电源为3.3v。dsp的内核电源也可以通过这样的方式计算得出。

[0069]

tps54310芯片转换频率可以被设定为固定的350khz或550khz内部振荡器频率,也可以被设定为可调的280khz-700khz。振荡器的设定由sync(同步输入)和rt(频率设置寄存器输入)引脚共同决定,当sync引脚与rt引脚悬空时,转换频率为350khz。当sync引脚悬空,而rt引脚与地之间接入 68k到180k的电阻r1时,转换频率则变化为可调的280khz-700khz。转换频率的计算公式为:

[0070][0071]

式中:f

sw

为转换频率,r1为连接在rt引脚与地之间的电阻值。将r1 的电阻值设置为71.5k欧姆,则可以计算得到电源开关转换频率为700khz。

[0072]

dsp需要两种电源,一种是内核电源(1.8v),另一种是i/o电源(3.3v)。由于电源电路设计不仅要考虑电压精度、稳定度和外围电路的复杂度等问题,还要考虑低功耗问题。另外,根据设计要求,为了保证芯片正常工作,在系统上电作时,对这两种电源的上电顺序还有一定的要求,如果违反该要求,可能降低器件的性能或永久损坏器件。内核电源要比i/o电源早上电,至少不能晚于i/o电源上电。在电路设计中,通过采用在两个电源之间串联二极管的方法来解决系统上电顺序的问题,电路设计如图3所示。

[0073]

二极管在正向导通时会有一个管压降,在本系统中选用的是肖特基 murs120t3二极管,它的管压降是0.4v。这样,假如是i/o电源(vcc3.3) 先上电,它通过四个二极管降压后得到1.7v的电压,使得内核电源的输出引脚也能达到1.7v,这样至少可以保证内核电源和i/o电源同时上电。

[0074]

如图4为发明辐照测试系统的电路框图。该电路可以同时对两块dsp进行配置,提高了辐射实验的效率,并且能够进行动态偏置和静态偏置两种偏置实验。电路的pcb由母板电路和子板电路组成。其中母板主要包含fpga 及其相应的配套电路组成,子板主要是放置在辐射下的被测dsp器件。

[0075]

1)上位机

[0076]

上位机采用labview编写,通过网口与fpga相连接,主要功能是控制 fpag分别来

配置dsp的配置状态;实时对比dsp运算的结果并显示错误数据及发生时间;实时显示试验过程中dsp的电流电压值。

[0077]

2)fpga母板电路

[0078]

母板是辐照测试系统的一个平台,母板上主要包含以fpga为核心的电路系统,以及与子板的相连接的高速连接器。设计之所以采用子母板的结构,是为了提高硬件系统的兼容性。设计完成后,可以通过更改子板上的被测器件或电路,以进行其他器件的总剂量测试。同时可以更改相应的fpga软件,以进行相关器件单粒子实验。为了完全控制dsp的状态并与dsp进行数据通信,两个被测dsp的信号管脚(除电源以外的io管脚)全部与fpga相连。而这些连接关系通过母板上两个连接器插槽管脚的连接来实现。

[0079]

母板上的电源采用两种电源芯片:lt1764aeq和pth04t230w。 lt1764aeq的输出电压分别是1.8v、3.3v、2.5v,pth04t230w的输出电压为1.2v。而且每路输出电压都有较高的电流,能够为母板上所有的芯片提供所需要的工作电压。

[0080]

fpga整个系统的核心部分,在具体实施例中采用xilinx的virtex4系列产品中的xc4vlx60-ff668c。该fpga具有640个用户可配置的io,内部逻辑单元达60万个,具有丰富的逻辑和内部ram存储空间。

[0081]

fpga母板实现对被测dsp状态的监测,测试数据的接收,给dsp提供时钟,对dsp进行静态、动态偏置以及与上位机通信等功能。fpga母板与上位机通过以太网接口进行通信,如图5所示为网口通信示意图。母板包含了以太网接口和物理层芯片,代码采用ise内部集成的mac的ip核,将物理层芯片配置为千兆位介质独立接口(gmii)。代码实现了基于用户数据报协议(udp)的以太网接口通信功能,最高可达1gbps的高速通信。

[0082]

代码中包括数据链路层(link layer),网络层(ip layer),传输层(udp),其中数据链路层采用地址解析协议(arp)实现ip地址到mac地址的动态映射,把32位ip地址转换为48位mac地址,而且为ip模块接收和发送ip数据报。网络层为udp模块发送和接收udp数据报,进行ip包的数据校验。传输层负责将用户数据进行打包并以udp形式发送,解析接收到的udp数据报中的用户数据,得到上位机发送的操作指令。该网口通信模块以125m时钟频率进行数据处理,各个模块间以流水线方式进行工作,可以实现高效实时的数据传输。

[0083]

fpga母板与dsp子板的通信依靠连接器完成,动态偏置试验中可通过双端口ram实现数据通信,fpga采用ping-pong结构进行数据接收,根据dsp中emif模块的时序图,数据的写入是低电平触发的,触发的信号满足w=ce+awe,只有当片选信号ce和写信号awe同时为低时才使得触发信号w有效。双端口ram在w为低时进行数据采样,完成数据的传输。

[0084]

fpga芯片外部还配置有sram存储器,用于存储fpga接收dsp子板电路的测试数据,也可以直接配置为dsp的外部存储器,存储dsp的程序或数据结果,sram的所有信号都与fpga相连。因此有必要测试sram存储器对辐照的敏感程度。

[0085]

图6是本发明cmos静态存储单元(sram)的电路结构。t1~t4构成sr 锁存器,用来记忆1位二进制数据。t5和t6是门控管,起到了开关的作用,以控制锁存器的q、q'和位线b、b'间的联系。t5、t6的开关状态由字线xi的状态决定。xi=1时t5、t6导通,锁存器的q和q'端与位线b、b'接通,存储器可以输出所保存的值或接收新的赋值;xi=0时,这种联系中断,电路起存储功能。t7和t8是两个门控管,配合缓冲放大器a1~a3,用于控制读/ 写功能,它们的状态由列地址yj来控制,yj=1时导通,yj=0时截止。

[0086]

当选定某个存储单元以后,xi=1、yj=1,t5、t6、t7、t8均导通,q和 q'与b、b'接通。如果这时cs'=0、r/w'=1,则a1导通、a2、a3截止,端的逻辑值经过a1传送至i/o端,即执行“读”功能。若此时cs

′

=0、 r/w'=0则a1截止、a2和a3接通,可以实现数据写入。

[0087]

3)dsp子板电路

[0088]

dsp子板电路是被测器件的平台,核心为两片被测dsp芯片,所述dsp 芯片为ti公司的tms320c6701 dsp。dsp子板电路要满足最小系统的要求,结构框图如图7所示,主要包括25m的晶振、jtag电路、flash芯片、连接器、复位电路,为方便硬件调试还增加了必要的测试端口和配置端口。

[0089]

子板上每个dsp分别外接一个外部flash存储器和一个jtag接口。flash 与dsp的连接关系如图8所示,jtag与dsp的连接方式如图9所示。flash 的作用是存储常用的dsp初始化程序;jtag将dsp与上位机上的ccs软件相连,通过ccs软件将dsp的初始化程序烧写到flash中。

[0090]

两片dsp的i/o电源与内核电源四路电源需要专门使用独立的数字电源供电,以便可以实时观测器件的电流。

[0091]

dsp的内部时钟由一个来自clkin引脚的时钟源产生。该时钟源由外部的时钟电路提供。外部输入时钟经过片内pll倍频之后,可以产生cpu的工作时钟和各种外设所需要的时钟信号。

[0092]

系统时钟发生电路的基准时钟是由一个外部时钟发生电路来提供的,一般的时钟晶振频率在20-50mhz之间。在具体实施例中的时钟发生电路图如图 10所示。从图10中可以看出,在时钟发生电路中,电容和电感组成电源滤波电路为晶体振荡器提供稳定的工作电压。晶体振荡器产生的时钟信号再经过一个33欧姆的电阻传送给dsp芯片的时钟信号输入端。在进行pcb布局时,该电阻应尽可能地靠近dsp芯片时钟信号输入引脚,以减少外部信号的干扰。在本系统中的晶体振荡器采用的是50mhz的有源贴片晶体振荡器。

[0093]

系统使用50mhz的振荡器来产生输入时钟,此外dsp还有一个内部pll 来倍频输入时钟以产生内部时钟。输入时钟绕过pll或者乘以一个系数 (clkin频率乘法器),从而产生输出时钟(clkout1)。该输出时钟可以用作 dsp的内部时钟,然后输出时钟clkout1就用来产生外部时钟。

[0094]

为了能够得到良好的上电复位,同时可以对系统的电压进行有效的监控,在具体实施例中选用了maxim公司生产的max708t芯片来达到上述要求。

[0095]

max708t是一种微处理器电源监控芯片,用它来监控电压时可以降低电路的复杂程度。max708t可以显著提高系统的可靠性和精确度。在复位时它可以输出高电平有效和低电平有效的复位信号。max708t的域值电压是3.08 v。系统复位监控电路如图11所示。

[0096]

从图11中可知,max708t的vcc(电源输入)脚接的是3.3v电压,因此,该系统监控的电压是3.3v。当系统监测到vcc低于域值电压或引脚保持低电平时,引脚就会输出低电平,对系统进行复位。在复位条件结束后,信号会继续保持200ms。

[0097]

dsp的管脚除了电源地和模拟管脚之外所有信号线都与fpga母板的连接器相连。fpga母板实现对被测dsp状态的监测,测试数据的接收,给dsp 提供时钟,对dsp进行静态、动态偏置以及与上位机通信等功能。

[0098]

实施例二:

[0099]

本发明还提供了一种数字信号处理电路静态偏置总剂量测试方法,如图12所示,包括以下步骤:

[0100]

步骤s11,上位机启动,fpga上电,与上位机相连接。

[0101]

步骤s12,fpga进行初始化。将编写好的verilog代码通过impact烧写母板上面的bpi flash中,以后fpga每次上电后都可以从flash中读取程序直接运行。fpga首先配置dsp的模式选择状态,包括bootmode[0:4]、 pllfreq[0:2]、clkmode[0:1]、lenian等。

[0102]

步骤s13,dsp子板电路上电,并进行初始化,将编写好的c语言程序烧写在dsp子板上的flash中,dsp上电从flash中读取程序进行工作。dsp 的配置主要包括:

[0103]

a)dsp使能各个外设模块,并对外设相关的输出及三态管脚的缓冲寄存器进行赋值,使之偏置为预期的固定电平;

[0104]

b)dsp对片上sram进行棋盘阵列的配置;

[0105]

c)dsp对内部的32个通用寄存器进行赋值。

[0106]

步骤s14,dsp进入pd3模式(节电模式)。dsp配置结束后要锁定dsp 的静态偏置状态,这时dsp进入pd3模式,pll的输入时钟停止产生时钟信号,所有寄存器和内部ram的内容被保留,dsp所有的功能i/o冻结为最后的状态。

[0107]

步骤s15,dsp输入管脚的配置。dsp进入pd3状态后,其内核电路的状态、输出及三态管脚的状态被锁定,此时fpga对dsp的输入管脚进行硬拉偏为固定的状态,并将fpga连接器中未用的管家通过ise软件设置为高阻态。

[0108]

步骤s16,进行辐照。dsp的静态偏置状态完成之后,将整个总剂量检测系统放入辐射环境中进行实验,其中除dsp之外的所有器件均使用铅砖进行遮挡。试验中要求的剂量率为2rad(si)/s。

[0109]

步骤s17,上位机实时记录dsp的实时状态和电流电压值。实验过程中对dsp的i/o电源3.3v和内核电源1.8v进行实时监测,将数字电源上的电流电压值通过上位机进行显示,并绘制成曲线。

[0110]

dsp静态偏置完成后,将测试板放入辐射室进行辐照,实验过程中每5min 记录一次电流电压值,当dsp的电流电压值出现明显增大时,应停止辐照,确定累积的总剂量值。静态试验的调试相对简单,通过fpfa母板对dsp的输入输出管脚进行固定的偏置,dsp子板运行程序对内核电路进行偏置,辐射试验过程中通过上位机实时记录dsp的电流电压值。

[0111]

实施例三:

[0112]

本发明还提供了一种数字信号处理电路动态偏置总剂量测试方法,如图 13所示,包括以下步骤:

[0113]

步骤s21,上位机的启动与fpga上电。

[0114]

步骤s22,fpga进行配置:

[0115]

fpga的配置采用主串模式,通过程序配置fpga,定义fpga的初始功能。

[0116]

步骤s23,fpga初始化:

[0117]

对fpga与dsp外设相连接的接口模块进行配置,以便fpga和dsp的各个单元信号都能进行数据交换,这些模块包括urat、emif、hpi、mcbsp、dma、timers等,同时fpga控制bootmode[0:4]、lenian、pllfreq[0:2]、 clkmode[0:1]模式选择;由于dsp在辐射期间需要

不断运行程序,并不时地将数据返回并保存,因此需要将动态程序提前保存母板上的sram中, sram作为fpga的外部存储器,保存dsp在动态时需要运行的算法程序,并将dsp返回给fpga的数据保存到sram中。

[0118]

步骤s24,dsp上电,并执行初始化程序:

[0119]

初始化程序提前烧写到dsp所挂的flash中,使dsp进入初始工作状态。 5)dsp执行功能程序:timer0/1配置为脉冲模式,由tout0/1引脚输出定时脉冲。mcbsp0/1配置为数据回环模式,从fpga接收数据并发送到fpga。 fpga通过hpi给dsp中64kb数据sram读写数据。cpu进行1024点fft 运算,每个计算结果存储在片上数据存储区,当计算结束通过dma把1024 个计算结果搬运到外部存储区。

[0120]

步骤s26,进行辐照:辐照期间dsp一直执行动态程序。

[0121]

步骤s27,上位机记录dsp实时电流电压值。一般通过数字电源对dsp 的电流电压值进行实时监测,可以通过把数字电源和上位机连接,使上位机实时显示出实验中dsp的电流电压值,并绘制成曲线,观察曲线的变化情况。

[0122]

dsp动态偏置完成后,将测试板放入辐射室进行辐照,实验过程中每5min 记录一次电流电压值,并且随时注意上位机显示的dsp运算出错的数据和时间。当数据大面积出错或电流值大幅度增大时,应停止辐照,确定累积的总剂量值。

[0123]

动态偏置测试的调试相对复杂,本发明是基于fpga母板和dsp子板的硬件系统,在动态偏置试验的电路调试过程中,dsp子板的单独调试是正确的,可以通过ccs软件对dsp进行操作,对dsp的寄存器进行赋值,并在子板的测试端口可以查看调试的结果。

[0124]

实施例四:

[0125]

本发明还提供了一种抗电磁脉冲数字信号处理电路,包括所述的dsp子板电路,还包括外接的抗电磁脉冲电路,如图14所示,所述抗电磁脉冲电路包括:第一输入端(i1)、第二输入端(i2)、第一输出端(o1)、第二输出端(o2)、第一压敏电阻(r1)、第二压敏电阻(r2)、第一气体放电管(g1)、第二气体放电管 (g2)、第一电感(l1)、第二电感(l2).

[0126]

g1和g2串联后跨接在输入端两端i1和i2之间,g1和g2之间的连接点接地;r1和r2串联连接在输出端的两端o1、o2,其连接点接地。l1连接i1和o1,l2连接i2和o2。当遭受高能电磁脉冲浪涌袭击时,i1、i2对地均承受了极大过电压和过电流。当r1和r2两端承受的电压超过其启动电压后,r1、r2导通泄放电流,对高能电磁脉冲防护电路提供共模保护。当g1、 g2两端承受的电压超过二者的启动电压时,g1和g2从高阻态变为导通,泄放掉大部分的浪涌过电流。l1和l2对浪涌进行阻碍和削弱。

[0127]

气体放电管在平时呈高阻状态,对正常线路传输没有任何影响。气体放电管拥有通流量大的特点,可以将大部分核电磁脉冲产生的浪涌泄放到大地。但气体放电管的响应时间长,在尚未泄放浪涌时就已经造成了后端元器件的损坏,所以在本发明所述电路中使用响应时间快的压敏电阻。压敏电阻是典型的具有非线性特性的器件,在平时也是呈高阻状态,不会对正常线路传输造成影响,但压敏电阻的优点是响应时间快,在气体放电管尚未启动之前就泄放掉一部分的浪涌,直到气体放电管启动后泄放掉大部分的浪涌。在压敏电阻和气体放电管之间连接有电感,电感能够对交变电流起到阻碍遏制的作用,将能量强大的核电磁脉冲削弱一部分,对压敏电阻和气体放电管起到保护作用。

[0128]

需要说明的是,上文只是对本发明进行示意性说明和阐述,本领域的技术人员应

当明白,对本发明的任意修改和替换都属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1