双通道联合零值实时校准装置及方法与流程

1.本发明涉及零值校准技术领域,尤其涉及一种双通道联合零值实时校准装置及方法。

背景技术:

2.随着卫星测控、星间链路、时间同步等领域的发展,对于零值测量准确度和稳定度要求越来越高。对于使用伪码测距方式的具有零值实时校准需求的设备而言,零值测量精度对于定位、定轨、时间同步精度均有较大影响,零值实时校准技术也成为一种至关重要的技术。

技术实现要素:

3.本发明的目的在于提供一种双通道联合零值实时校准装置及方法,既可有效去除因采样时钟相位变化、测距时标漂移等因素引起的短期零值变化,又可体现出因元器件老化和环境温度变化等因素引起的长期零值变化,保证通道零值测量的准确度和稳定度。

4.为实现上述发明目的,本发明的技术方案是:

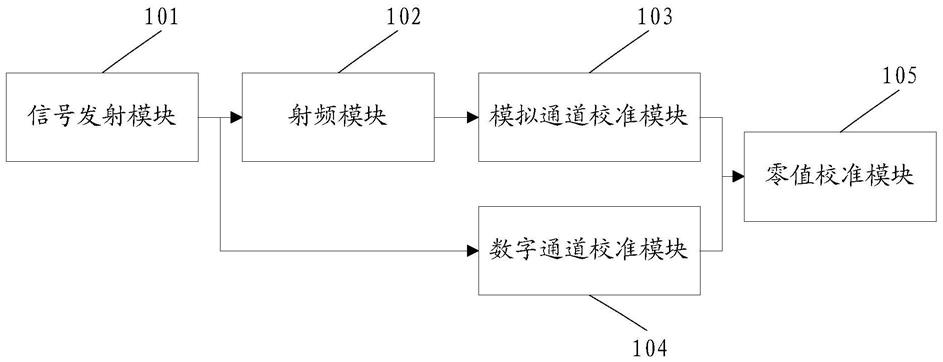

5.本发明提供一种双通道联合零值实时校准装置,包括:信号发射模块、射频模块、模拟通道校准模块、数字通道校准模块和零值校准模块,

6.所述信号发射模块用于生成发射载波和测量通道伪码,一路将所述测量通道伪码与所述发射载波经数字混频后转换输出模拟信号,另一路输出所述测量通道伪码至所述数字通道校准模块;

7.所述射频模块用于对所述模拟信号进行上下变频处理,并输出模拟中频信号;

8.所述模拟通道校准模块用于对所述模拟中频信号进行模数转换和模拟通道零值测量,并输出模拟通道零值;

9.所述数字通道校准模块用于测量所述测量通道伪码的相位,并输出数字通道零值;

10.所述零值校准模块用于对所述模拟通道零值和所述数字通道零值进行联合解算,输出最终真实的收发通道零值。

11.根据本发明的一个方面,所述信号发射模块包括:载波生成器、伪码发生器、数字混频器和数模转换器,

12.所述载波生成器用于以发射采样时钟作为工作时钟,利用数控振荡器以载波频率控制字累加溢出形式生成发射载波;

13.所述伪码发生器用于以伪码生成时钟作为移位驱动时钟,并以多级反馈移位寄存器形式生成测量通道伪码;

14.所述数字混频器用于将所述发射载波和所述测量通道伪码进行数字混频;

15.所述数模转换器用于将数字混频后的信号转换为模拟信号。

16.根据本发明的一个方面,所述射频模块包括:上变频通道、耦合通道和下变频通

道,

17.所述上变频通道用于对所述模拟信号进行从中频频率到射频频率的上变频、滤波和放大处理;

18.所述耦合通道用于将处理后的模拟信号耦合一路至所述下变频通道;

19.所述下变频通道用于对耦合支路信号进行从射频频率到中频频率的下变频、滤波和放大处理。

20.根据本发明的一个方面,所述模拟通道校准模块包括:模数转换器、数字混频器、载波生成器、相关器、鉴相器、环路滤波器、伪码发生器和模拟通道零值测量模块,

21.所述模数转换器用于对所述模拟中频信号进行模数转换,输出数字中频信号至所述数字混频器;

22.所述载波生成器用于以接收采样时钟作为工作时钟,利用数控振荡器以载波频率控制字累加溢出形式生成同向支路和正交支路的两路本地载波,并输出至所述数字混频器;

23.所述数字混频器用于对所述数字中频信号和所述两路本地载波进行数字混频完成载波剥离,将所述数字中频信号的频谱搬移至零频附近形成数字基带信号;

24.所述伪码发生器用于以多级反馈移位寄存器形式生成超前支路、即时支路和滞后支路的本地测量通道伪码,利用数控振荡器以伪码频率控制字累加溢出形式控制本地测量通道伪码速率;

25.所述相关器用于对所述数字基带信号和所述本地测量通道伪码进行乘法和相干积分运算,输出同向超前支路相干积分结果、同向滞后支路相干积分结果、正交超前支路相干积分结果和正交滞后支路相干积分结果至所述鉴相器;

26.所述鉴相器用于对所述同向超前支路相干积分结果、所述同向滞后支路相干积分结果、所述正交超前支路相干积分结果和所述正交滞后支路相干积分结果先进行非相干积分,再进行伪码相位鉴别,获得超前支路非相干积分结果和滞后支路非相干积分结果;

27.所述环路滤波器用于对所述超前支路非相干积分结果和滞后支路非相干积分结果进行滤波,输出伪码相位同步误差;

28.所述模拟通道零值测量模块用于在测量时刻根据即时支路本地测量通道伪码相位推算当前信号发射时间,结合本地时间计算模拟通道零值,并输出至所述零值校准模块。

29.根据本发明的一个方面,所述数字通道校准模块包括:相关器、鉴相器、环路滤波器、伪码发生器和数字通道零值测量模块,

30.所述伪码发生器用于以多级反馈移位寄存器形式生成超前支路、即时支路和滞后支路的本地测量通道伪码,利用数控振荡器以伪码频率控制字累加溢出形式控制本地测量通道伪码速率;

31.所述相关器用于对所述信号发射模块输出的测量通道伪码和所述本地测量通道伪码进行乘法和相干积分运算,输出超前支路相干积分结果和滞后支路相干积分结果至所述鉴相器;

32.所述鉴相器用于对所述超前支路相干积分结果和滞后支路相干积分结果进行伪码相位鉴别;

33.所述环路滤波器用于对所述鉴相器输出的结果进行滤波,输出伪码相位同步误

差;

34.所述数字通道零值测量模块用于在测量时刻根据即时支路本地测量通道伪码相位推算当前信号发射时间,结合本地时间计算数字通道零值,并输出至所述零值校准模块。

35.根据本发明的一个方面,所述模拟通道零值扣除所述数字通道零值后为所述真实的收发通道零值,为:

36.ρ=ρ

a-ρb37.其中,ρa表示模拟通道零值,ρb表示数字通道零值。

38.一种利用如上述双通道联合零值实时校准装置实现的双通道联合零值实时校准方法,包括:

39.s1.利用信号发射模块生成发射载波和测量通道伪码,一路将所述测量通道伪码与所述发射载波经数字混频后转换输出模拟信号,另一路输出所述测量通道伪码至数字通道校准模块;

40.s2.利用射频模块对所述模拟信号进行上下变频处理,并输出模拟中频信号;

41.s3.利用模拟通道校准模块对所述模拟中频信号进行模数转换和模拟通道零值测量,并输出模拟通道零值;

42.s4.利用数字通道校准模块测量所述测量通道伪码的相位,并输出数字通道零值;

43.s5.利用零值校准模块对所述模拟通道零值和所述数字通道零值进行联合解算,输出最终真实的收发通道零值。

44.根据本发明的另一个方面,所述步骤s1包括:

45.s11.利用外部输入信号作为所述信号发射模块的输入,所述外部输入信号包括秒脉冲1pps、伪码生成时钟f

code

、发射采样时钟f

st

、载波频率控制字m

t

;

46.s12.利用载波生成器以发射采样时钟作为工作时钟,利用数控振荡器以载波频率控制字累加溢出形式生成发射载波,所述发射载波的频率为:

[0047][0048]

其中,n表示数控振荡器的深度;

[0049]

s13.利用伪码发生器以伪码生成时钟作为移位驱动时钟,并以多级反馈移位寄存器形式生成测量通道伪码,则测量通道伪码的速率为f

code

;

[0050]

s14.利用数字混频器将所述发射载波和所述测量通道伪码进行数字混频;

[0051]

s15.利用数模转换器将数字混频后的信号转换为模拟信号。

[0052]

根据本发明的另一个方面,所述步骤s3包括:

[0053]

s31.利用外部输入信号作为所述模拟通道校准模块的输入,所述外部输入信号包括秒脉冲1pps、接收采样时钟f

sr

、伪码频率控制字m

code

、载波频率控制字mr;

[0054]

s32.利用模数转换器对所述模拟中频信号进行模数转换,输出数字中频信号至所述数字混频器;

[0055]

s33.利用载波生成器以所述接收采样时钟作为工作时钟,利用数控振荡器以所述载波频率控制字累加溢出形式生成同向支路和正交支路的两路本地载波,并输出至所述数字混频器,所述本地载波的频率为:

[0056][0057]

其中,n表示数控振荡器的深度;

[0058]

s33.利用数字混频器对所述数字中频信号和所述两路本地载波进行数字混频完成载波剥离,将所述数字中频信号的频谱搬移至零频附近形成数字基带信号;

[0059]

s34.利用伪码发生器以多级反馈移位寄存器形式生成超前支路、即时支路和滞后支路的本地测量通道伪码,利用数控振荡器以伪码频率控制字累加溢出形式控制本地测量通道伪码速率,所述本地测量通道伪码速率为:

[0060][0061]

s35.利用相关器对所述数字基带信号和所述本地测量通道伪码进行乘法和相干积分运算,输出同向超前支路相干积分结果、同向滞后支路相干积分结果、正交超前支路相干积分结果和正交滞后支路相干积分结果;

[0062]

s36.利用鉴相器对所述同向超前支路相干积分结果ie、所述同向滞后支路相干积分结果i

l

、所述正交超前支路相干积分结果qe和所述正交滞后支路相干积分结果q

l

先进行非相干积分,再进行伪码相位鉴别,获得超前支路非相干积分结果和滞后支路非相干积分结果分别为:

[0063][0064]

鉴相误差函数为:

[0065][0066]

其中,d表示早迟e-l相关器间距;

[0067]

s37.利用环路滤波器对所述超前支路非相干积分结果和所述滞后支路非相干积分结果进行滤波,输出伪码相位同步误差;

[0068]

s38.利用模拟通道零值测量模块在测量时刻根据即时支路本地测量通道伪码相位推算当前信号发射时间,结合本地时间计算模拟通道零值,并输出至所述零值校准模块。

[0069]

根据本发明的另一个方面,所述步骤s4包括:

[0070]

s41.利用外部输入信号作为所述数字通道校准模块的输入,所述外部输入信号包括秒脉冲1pps、接收采样时钟f

sr

、伪码频率控制字m

code

、载波频率控制字mr;

[0071]

s42.利用伪码发生器以多级反馈移位寄存器形式生成超前支路、即时支路和滞后支路的本地测量通道伪码,利用数控振荡器以伪码频率控制字累加溢出形式控制本地测量通道伪码速率,所述本地测量通道伪码速率为:

[0072][0073]

其中,n表示数控振荡器的深度;

[0074]

s43.利用相关器对所述信号发射模块输出的测量通道伪码和所述本地测量通道伪码进行乘法和相干积分运算,输出超前支路相干积分结果和滞后支路相干积分结果至所述鉴相器;

[0075]

s44.利用鉴相器对所述超前支路相干积分结果ie和滞后支路相干积分结果i

l

进行伪码相位鉴别,鉴相误差函数为:

[0076][0077]

其中,d表示早迟e-l相关器间隔;

[0078]

s45.利用环路滤波器对所述鉴相器输出的结果进行滤波,输出伪码相位同步误差;

[0079]

s46.利用数字通道零值测量模块在测量时刻根据即时支路本地测量通道伪码相位推算当前信号发射时间,结合本地时间计算数字通道零值,并输出至所述零值校准模块。

[0080]

有益效果:

[0081]

根据本发明的方案,利用数字通道测量因采样时钟相位变化、测距时标漂移等因素引起的短期零值变化并且在模拟通道零值中剔除。利用模拟通道测量因元器件老化和环境温度变化等因素引起的长期零值变化并且数字通道零值对长期零值变化不敏感。本发明在现有收发通道自闭环校准技术的基础上不新增射频通道和逻辑器件,只在原有的fpga或cpu等可编程器件中增加一路数字通道即可实现收发通道零值高准确度和高稳定度校准,成本低。

[0082]

通过采用模拟通道和数字通道联合测量方法,解算收发通道真实零值,既可有效去除因采样时钟相位变化、测距时标漂移等因素引起的短期零值变化,又可体现出因元器件老化和环境温度变化等因素引起的长期零值变化,保证收发通道零值测量的准确度和稳定度。

附图说明

[0083]

图1示意性表示本发明的一种实施方式的双通道联合零值实时校准装置的模块组成图;

[0084]

图2示意性表示本发明的一种实施方式的双通道联合零值实时校准装置的具体结构示意图;

[0085]

图3示意性表示本发明的一种实施方式的双通道联合零值实时校准装置的信号发射模块内部时序图;

[0086]

图4示意性表示本发明的一种实施方式的双通道联合零值实时校准装置的模拟通道校准模块和数字通道校准模块的内部时序图;

[0087]

图5示意性表示本发明的一种实施方式的双通道联合零值实时校准装置的2阶dll环路滤波器结构图;

[0088]

图6示意性表示本发明的一种实施方式的双通道联合零值实时校准方法的流程图。

具体实施方式

[0089]

为了更清楚地说明本发明实施方式或现有技术中的技术方案,下面将对实施方式中所需要使用的附图作简单地介绍。显而易见地,下面描述中的附图仅仅是本发明的一些实施方式,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些

附图获得其他的附图。

[0090]

下面结合附图和具体实施方式对本发明作详细地描述,实施方式不能在此一一赘述,但本发明的实施方式并不因此限定于以下实施方式。

[0091]

如图1所示,一方面,本实施方式的双通道联合零值实时校准装置,包括:信号发射模块101、射频模块102、模拟通道校准模块103、数字通道校准模块104和零值校准模块105。其中,信号发射模块101用于生成发射载波和测量通道伪码,一路将测量通道伪码与发射载波经数字混频后转换输出模拟信号,另一路输出测量通道伪码至数字通道校准模块104;射频模块102用于对模拟信号进行上下变频处理,并输出模拟中频信号;模拟通道校准模块103用于对模拟中频信号进行模数转换和模拟通道零值测量,并输出模拟通道零值,即为模拟中频信号的零值;数字通道校准模块104用于测量测量通道伪码的相位,并输出数字通道零值,即为测量通道伪码相位的零值;零值校准模块105用于对模拟通道零值和数字通道零值进行联合解算,输出最终真实的收发通道零值。

[0092]

如图2所示,上述信号发射模块101包括:载波生成器、伪码发生器、数字混频器和数模转换器。利用外部输入信号作为信号发射模块101的输入,外部输入信号包括秒脉冲1pps、伪码生成时钟f

code

、发射采样时钟f

st

、载波频率控制字m

t

。

[0093]

其中,载波生成器用于以发射采样时钟作为工作时钟,利用数控振荡器(nco)以载波频率控制字累加溢出形式生成发射载波发射载波的频率为:

[0094][0095]

其中,n表示数控振荡器的深度。在本实施方式中,发射载波频率f

ct

为51.15mhz。

[0096]

伪码发生器用于以伪码生成时钟作为移位驱动时钟,并以多级反馈移位寄存器形式生成测量通道伪码,则测量通道伪码的速率为f

code

。在本实施方式中,测量通道伪码速率f

code

为10.23mcps。数字混频器用于将发射载波和测量通道伪码进行数字混频。数模转换器用于将数字混频后的信号转换为模拟信号。

[0097]

秒脉冲和伪码生成时钟同源,两者相位关系保持固定。信号发射模块101以伪码生成时钟上升沿对秒脉冲进行采样,当识别出秒脉冲高电平后生成发射脉冲,脉冲宽度为一个伪码生成时钟周期。发射信号生成以发射脉冲作为触发信号,可保证发射信号与秒脉冲相位关系严格固定。而发射采样时钟一般由频率综合器产生,可避免因发射采样时钟与秒脉冲相位关系变化引起的零值跳变,如图3所示,发射脉冲与秒脉冲相位差δt1随时间不发生变化,发射采样时钟与秒脉冲相位差δt2随时间发生变化。

[0098]

如图2所示,上述射频模块102包括:上变频通道、耦合通道和下变频通道。其中,上变频通道用于对模拟信号进行从中频频率到射频频率的上变频、滤波和放大处理;耦合通道用于将处理后的模拟信号耦合一路至下变频通道;下变频通道用于对耦合支路信号进行从射频频率到中频频率的下变频、滤波和放大处理。

[0099]

如图2所示,上述模拟通道校准模块103包括:模数转换器、数字混频器、载波生成器、相关器、鉴相器、环路滤波器、伪码发生器和模拟通道零值测量模块。利用外部输入信号作为模拟通道校准模块103的输入,外部输入信号包括秒脉冲1pps、接收采样时钟f

sr

、伪码频率控制字m

code

、载波频率控制字mr。

[0100]

其中,模数转换器用于对模拟中频信号进行模数转换,输出数字中频信号至数字

混频器。载波生成器用于以接收采样时钟作为工作时钟,利用数控振荡器以载波频率控制字累加溢出形式生成同向支路(i)和正交支路(q)的两路本地载波,并输出至数字混频器。两路载波相位相差90

°

,本地载波的频率为:

[0101][0102]

其中,n表示数控振荡器的深度。在本实施方式中,本地载波频率f

cr

为140mhz。

[0103]

数字混频器用于对数字中频信号和两路本地载波进行数字混频完成载波剥离,将数字中频信号的频谱搬移至零频附近形成数字基带信号。伪码发生器用于以多级反馈移位寄存器形式生成超前支路(e)、即时支路(p)和滞后支路(l)的本地测量通道伪码,利用数控振荡器以伪码频率控制字累加溢出形式控制本地测量通道伪码速率。伪码频率控制字根据环路滤波器输出的伪码相位同步误差进行动态调整以保持对测量通道伪码的稳定跟踪,则本地测量通道伪码速率为:

[0104][0105]

在本实施方式中,测量通道伪码速率为f

code_r

为10.23mcps。

[0106]

相关器用于对数字基带信号和本地测量通道伪码进行乘法和相干积分运算,输出同向超前支路相干积分结果ie、同向滞后支路相干积分结果i

l

、正交超前支路相干积分结果qe和正交滞后支路相干积分结果q

l

至鉴相器。鉴相器用于对同向超前支路相干积分结果ie、同向滞后支路相干积分结果i

l

、正交超前支路相干积分结果qe和正交滞后支路相干积分结果q

l

先进行非相干积分,提高信噪比,再进行伪码相位鉴别,获得超前支路非相干积分结果和滞后支路非相干积分结果,分别为:

[0107][0108]

鉴相误差函数为:

[0109][0110]

其中,d表示早迟e-l相关器间距(单位是chips)。

[0111]

环路滤波器用于对超前支路非相干积分结果和滞后支路非相干积分结果进行滤波,输出伪码相位同步误差。这里的环路滤波器采用标准的2阶dll环路滤波器结构,如图5所示。滤波公式如下:

[0112][0113]

y2(n)=0.5[y1(n)+y1(n-1)];

[0114]

y(n)=y2(n)+δ

cp2

(n)*a2ωn;

[0115]

在本实施方式中,环路带宽b

l

为5hz,阻尼系数ξ为0.55。

[0116]

模拟通道零值测量模块用于在测量时刻根据即时支路本地测量通道伪码相位推算当前信号发射时间,结合本地时间计算模拟通道零值ρa(单位为s),并输出至零值校准模块105。tow

analog

为发射信号周内时(单位为s),c

analog

为从发射信号周内时开始到当前测量时刻内伪码整周数,cp

analog

为当前测量时刻对应的即时伪码相位(单位为chips),t

local

为当前测量时刻(单位为s)。在本实施方式中,测量通道伪码速率为f

code_r

为10.23mcps,码长

1023,则伪码整周期为0.0001s;

[0117]

ρa=t

local-tow

analog

+0.0001

×

(c

analog

+cp

analog

/1023)。

[0118]

模拟通道校准模块103以接收采样时钟上升沿对秒脉冲进行采样,当识别出秒脉冲高电平后生成接收脉冲,脉冲宽度为一个接收采样时钟周期。模拟通道零值测量时刻以接收脉冲作为测距时标,延迟固定时间后进行伪码相位测量。接收采样时钟一般由频率综合器产生,与秒脉冲相位关系不固定,会因开关机变化、测距时标漂移等引起短期内模拟通道零值跳变,如图4所示,接收采样时钟与秒脉冲相位差δt3随时间发生变化。因元器件老化和环境温度变化等因素引起的长期零值变化会体现在模拟通道零值结果中。

[0119]

如图2所示,上述数字通道校准模块104包括:相关器、鉴相器、环路滤波器、伪码发生器和数字通道零值测量模块。利用外部输入信号作为数字通道校准模块104的输入,外部输入信号包括秒脉冲1pps、接收采样时钟f

sr

、伪码频率控制字m

code

、载波频率控制字mr。

[0120]

其中,伪码发生器用于以多级反馈移位寄存器形式生成超前支路、即时支路和滞后支路的本地测量通道伪码,利用数控振荡器以伪码频率控制字累加溢出形式控制本地测量通道伪码速率。伪码频率控制字根据环路滤波器输出的伪码相位同步误差进行动态调整以保持对测量通道伪码的稳定跟踪,则本地测量通道伪码速率为:

[0121][0122]

其中,n表示数控振荡器的深度。在本实施方式中,测量通道伪码速率为f

code_r

为10.23mcps。

[0123]

相关器用于对信号发射模块输出的测量通道伪码和本地测量通道伪码进行乘法和相干积分运算,输出超前支路相干积分结果ie和滞后支路相干积分结果i

l

至鉴相器。鉴相器用于对超前支路相干积分结果ie和滞后支路相干积分结果i

l

进行伪码相位鉴别。鉴相误差函数为:

[0124][0125]

其中,d表示早迟e-l相关器间隔(单位是chips)。

[0126]

环路滤波器用于对鉴相器输出的结果进行滤波,输出伪码相位同步误差。这里的环路滤波器采用标准的2阶dll环路滤波器结构,如图5所示。滤波公式如下:

[0127][0128]

y2(n)=0.5[y1(n)+y1(n-1)];

[0129]

y(n)=y2(n)+δ

cp2

(n)*a2ωn;

[0130]

在本实施方式中,环路带宽b

l

为5hz,阻尼系数ξ为0.55。

[0131]

数字通道零值测量模块用于在测量时刻根据即时支路本地测量通道伪码相位推算当前信号发射时间,结合本地时间计算数字通道零值ρb(单位为s),并输出至零值校准模块105。tow

digital

为发射信号周内时(单位为s),c

digital

为从发射信号周内时开始到当前测量时刻内伪码整周数,cp

digital

为当前测量时刻对应的即时伪码相位(单位为chips),t

local

为当前测量时刻(单位为s)。在本实施方式中,测量通道伪码速率为f

code_r

为10.23mcps,码长1023,则伪码整周期为0.0001s;

[0132]

ρb=t

local-tow

digital

+0.0001

×

(c

digital

+cp

digital

/1023)。

[0133]

根据本发明的上述方案,数字通道校准模块104与模拟通道校准模块103共用秒脉冲、接收采样时钟和接收脉冲,在同一测量时刻分别进行数字通道零值和模拟通道零值计算。以接收采样时钟上升沿对秒脉冲进行采样,当识别出秒脉冲高电平后生成接收脉冲,脉冲宽度为一个接收采样时钟周期。数字通道零值测量时刻以接收脉冲作为测距时标,延迟固定时间后进行伪码相位测量。接收采样时钟一般由频率综合器产生,与秒脉冲相位关系不固定,会因开关机变化、测距时标漂移等引起短期内数字通道零值跳变,如图4所示,接收采样时钟与秒脉冲相位差δt3随时间发生变化。数字通道校准模块只在fpga或cpu等可编程器件中实现,不经过其他逻辑器件和模拟器件,对元器件老化和环境温度变化等因素不敏感,这些因素导致的长期零值变化不会体现在数字通道零值结果中。

[0134]

发射信号与秒脉冲相位关系严格固定,发射采样时钟与秒脉冲相位关系的变化不会导致信号发射时产生零值跳变。接收采样时钟一般由频率综合器产生,与秒脉冲相位关系不固定,会因开关机变化、测距时标漂移等引起信号接收时零值跳变。而数字通道零值表征的就是因接收采样时钟与秒脉冲相位关系变化导致的短期零值变化,该零值变化结果同样会体现在模拟通道零值中,并且因元器件老化和环境温度变化等因素引起的长期零值变化不会体现在数字通道零值结果中。因此,模拟通道零值扣除数字通道零值即为真实的收发通道零值ρ,

[0135]

ρ=ρ

a-ρb[0136]

其中,ρa表示模拟通道零值,ρb表示数字通道零值。

[0137]

该结果既可有效去除因采样时钟相位变化、测距时标漂移等因素引起的短期零值变化,又可体现出因元器件老化和环境温度变化等因素引起的长期零值变化,保证通道零值测量的准确度和稳定度。

[0138]

另一方面,如图6所示,本实施方式的双通道联合零值实时校准方法,包括:s1.利用信号发射模块生成发射载波和测量通道伪码,一路将测量通道伪码与发射载波经数字混频后转换输出模拟信号,另一路输出测量通道伪码至数字通道校准模块;s2.利用射频模块对模拟信号进行上下变频处理,并输出模拟中频信号;s3.利用模拟通道校准模块对模拟中频信号进行模数转换和模拟通道零值测量,并输出模拟通道零值;s4.利用数字通道校准模块测量测量通道伪码的相位,并输出数字通道零值;s5.利用零值校准模块对模拟通道零值和数字通道零值进行联合解算,输出最终真实的收发通道零值。

[0139]

其中,步骤s1包括:s11.利用外部输入信号作为信号发射模块的输入,外部输入信号包括秒脉冲1pps、伪码生成时钟f

code

、发射采样时钟f

st

、载波频率控制字m

t

;

[0140]

s12.利用载波生成器以发射采样时钟作为工作时钟,利用数控振荡器以载波频率控制字累加溢出形式生成发射载波,发射载波的频率为:

[0141][0142]

其中,n表示数控振荡器的深度;

[0143]

s13.利用伪码发生器以伪码生成时钟作为移位驱动时钟,并以多级反馈移位寄存器形式生成测量通道伪码,则测量通道伪码的速率为f

code

;

[0144]

s14.利用数字混频器将发射载波和测量通道伪码进行数字混频;

[0145]

s15.利用数模转换器将数字混频后的信号转换为模拟信号。

[0146]

步骤s2包括:s21.利用上变频通道对模拟信号进行从中频频率到射频频率的上变频、滤波和放大处理;

[0147]

s22.利用耦合通道将处理后的模拟信号耦合一路至下变频通道;

[0148]

s23.利用下变频通道对耦合支路信号进行从射频频率到中频频率的下变频、滤波和放大处理。

[0149]

步骤s3包括:s31.利用外部输入信号作为模拟通道校准模块的输入,外部输入信号包括秒脉冲1pps、接收采样时钟f

sr

、伪码频率控制字m

code

、载波频率控制字mr;

[0150]

s32.利用模数转换器对模拟中频信号进行模数转换,输出数字中频信号至数字混频器;

[0151]

s33.利用载波生成器以接收采样时钟作为工作时钟,利用数控振荡器以载波频率控制字累加溢出形式生成同向支路和正交支路的两路本地载波,并输出至数字混频器,本地载波的频率为:

[0152][0153]

其中,n表示数控振荡器的深度;

[0154]

s33.利用数字混频器对数字中频信号和两路本地载波进行数字混频完成载波剥离,将数字中频信号的频谱搬移至零频附近形成数字基带信号;

[0155]

s34.利用伪码发生器以多级反馈移位寄存器形式生成超前支路、即时支路和滞后支路的本地测量通道伪码,利用数控振荡器以伪码频率控制字累加溢出形式控制本地测量通道伪码速率,本地测量通道伪码速率为:

[0156][0157]

s35.利用相关器对数字基带信号和本地测量通道伪码进行乘法和相干积分运算,输出同向超前支路相干积分结果、同向滞后支路相干积分结果、正交超前支路相干积分结果和正交滞后支路相干积分结果;

[0158]

s36.利用鉴相器对同向超前支路相干积分结果ie、同向滞后支路相干积分结果i

l

、正交超前支路相干积分结果qe和正交滞后支路相干积分结果q

l

先进行非相干积分提高信噪比,再进行伪码相位鉴别,获得超前支路非相干积分结果和滞后支路非相干积分结果分别为:

[0159][0160]

鉴相误差函数为:

[0161][0162]

其中,d表示早迟e-l相关器间距;

[0163]

s37.利用环路滤波器对超前支路非相干积分结果和滞后支路非相干积分结果进行滤波,输出伪码相位同步误差;

[0164]

s38.利用模拟通道零值测量模块在测量时刻根据即时支路本地测量通道伪码相

位推算当前信号发射时间,结合本地时间计算模拟通道零值,并输出至零值校准模块。

[0165]

步骤s4包括:s41.利用外部输入信号作为数字通道校准模块的输入,外部输入信号包括秒脉冲1pps、接收采样时钟f

sr

、伪码频率控制字m

code

、载波频率控制字mr;

[0166]

s42.利用伪码发生器以多级反馈移位寄存器形式生成超前支路、即时支路和滞后支路的本地测量通道伪码,利用数控振荡器以伪码频率控制字累加溢出形式控制本地测量通道伪码速率,本地测量通道伪码速率为:

[0167][0168]

其中,n表示数控振荡器的深度;

[0169]

s43.利用相关器对信号发射模块输出的测量通道伪码和本地测量通道伪码进行乘法和相干积分运算,输出超前支路相干积分结果和滞后支路相干积分结果至鉴相器;

[0170]

s44.利用鉴相器对超前支路相干积分结果ie和滞后支路相干积分结果i

l

进行伪码相位鉴别,鉴相误差函数为:

[0171][0172]

其中,d表示早迟e-l相关器间隔;

[0173]

s45.利用环路滤波器对鉴相器输出的结果进行滤波,输出伪码相位同步误差;

[0174]

s46.利用数字通道零值测量模块在测量时刻根据即时支路本地测量通道伪码相位推算当前信号发射时间,结合本地时间计算数字通道零值,并输出至零值校准模块。

[0175]

对于本发明的方法所涉及的上述各个步骤的序号并不意味着方法执行顺序的先后,各步骤的执行顺序应以其功能和内在逻辑确定,而不应对本发明的实施方式的实施过程构成任何限定。

[0176]

以上所述仅为本发明的一个实施方式而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包括在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1