半导体测试设备的数字I/O通道校准方法与流程

本发明涉及i/o通道校准,具体涉及一种半导体测试设备的数字i/o通道校准方法。

背景技术:

1、在半导体测试领域,针对asic(application specific integrated circuit,特殊应用集成电路,即专用芯片)、存储芯片等数字芯片,测试设备通过提供数字i/o通道连接到芯片的被测管脚,并给予符合时序要求的激励信号或者从被测芯片接收信号,达到测试芯片功能和时序参数等的目的。测试设备提供的数字i/o通道一般较多,测试过程中,要求从这些i/o通道发送到被测芯片的信号的延时或者从被测芯片接收的信号的延时相等或者有一个固定的差值,使得测试信号的收发能够同步,尤其对于并行接口的测试,例如测试ddr芯片时,信号与信号之间的时序要求能精确控制。所以,为了达到i/o通道之间延时相等或固定,需要在测试设备出厂前对i/o通道进行校准,把i/o通道间发送信号到被测芯片的延时或者从被测芯片接收信号的延时测量出来,补偿到信号发送或接收的延时电路中,做到通道间的信号收发同步。

2、现有的一种通用的i/o通道校准方法是设计2块校准板,如图1所示,校准板1用于对数字i/o通道发送方向上的信号延时进行测量,在校准板1上采用tdc(time-to-digitalconverter,即时间数字转换器,是常用的时间间隔测量电子学电路,常用的高精度时间测量芯片有tdc-gp2等)芯片测试不同i/o通道(图1中的数字“1”“2”分别表示测试设备上的i/o通道1、i/o通道2)间的信号延时。校准板2用于对数字i/o通道接收方向上的信号延时进行测量,在校准板2上采用同步信号发生器发出相位对齐的同步信号,由tg(timinggenerator,信息时序发生器,一般用fpga芯片实现)测量出接收方向上的信号延时。最终,根据测得的i/o通道间发送和接收两个方向上的信号延时进行延时补偿,使得信号同步。

3、但现有的上述i/o通道校准方法存在以下两个技术问题:

4、1、校准板设计复杂,校准板上的tdc和同步信号发生器的布局数量有限,且单个tdc芯片和同步信号发生器上的通道数也是有限的,一般为4个、8个或16个。因此,在i/o通道数较多的情况下,需要在校准板上布置更多数量的tdc芯片和同步信号发生器,增加了校准板的设计难度和制造成本。

5、2、校准板上多个tdc芯片之间,或者多个同步信号发生器之间同样需要作信号同步,这种同步需要一个统一的参考源ref_clk,并需要增加一级或者多级同步信号发生器分发到用来测量延时的tdc芯片或产生同步信号的发生器上来实现,每一个同步信号发生器产生的信号之间虽同步性比较高,但还是存在一定的同步误差,这个误差经过多级累计被放大,影响校准板的校准精度。

技术实现思路

1、本发明以不增加校准板设计难度和制造成本为前提,以解决测试设备的i/o通道间信号不同步的问题为目的,提供了一种半导体测试设备的数字i/o通道校准方法。

2、为达此目的,本发明采用以下技术方案:

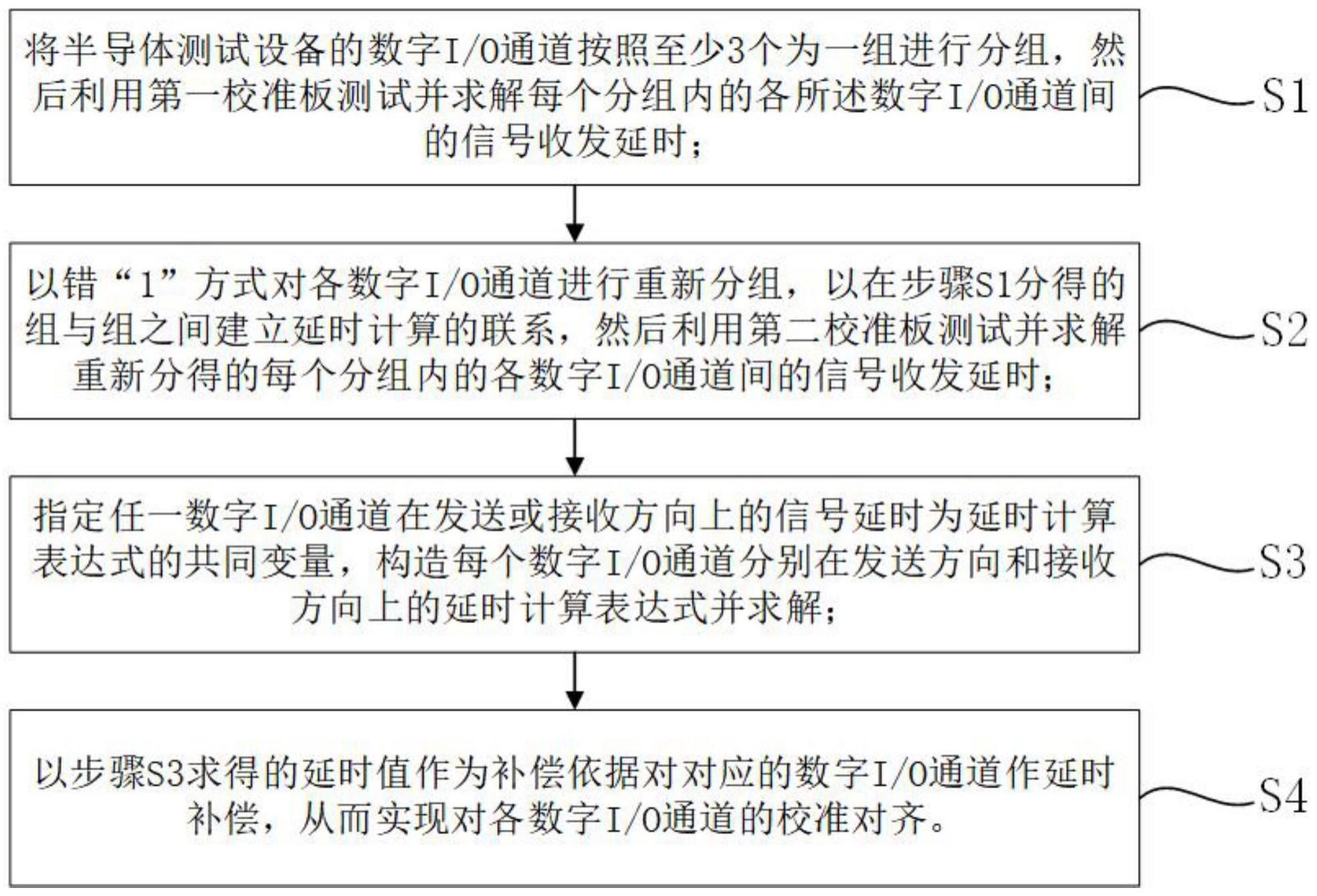

3、提供一种半导体测试设备的数字i/o通道校准方法,步骤包括:

4、s1,将半导体测试设备的数字i/o通道按照至少3个为一组进行分组,然后利用第一校准板测试并求解每个分组内的各所述数字i/o通道间的信号收发延时;

5、s2,以错“1”方式对各所述数字i/o通道进行重新分组,以在步骤s1分得的组与组之间建立延时计算的联系,然后利用第二校准板测试并求解重新分得的每个分组内的各所述数字i/o通道间的信号收发延时;

6、s3,指定任一所述数字i/o通道在发送或接收方向上的信号延时为延时计算表达式的共同变量,构造每个所述数字i/o通道分别在发送方向和接收方向上的延时计算表达式并求解;

7、s4,以步骤s3求得的延时值作为补偿依据对对应的所述数字i/o通道作延时补偿,从而实现对各所述数字i/o通道的校准对齐。

8、作为本发明的一种优选方案,步骤s1中,以3个为一组将所述测试设备上的若干个数字i/o通道划分为多个组。

9、作为本发明的一种优选方案,步骤s1分得的每组内的每个所述数字i/o通道在所述半导体测试设备与所述第一校准板间的布线长度相同。

10、作为本发明的一种优选方案,利用所述第一校准板或所述第二校准板测试并求解每个分组内的各所述数字i/o通道间的信号收发延时的方法通过以下公式(1)表达:

11、dtrij=ti+rj+2m公式(1)

12、公式(1)中,dtrij表示同一分组内从数字i/o通道i发送到数字i/o通道j间的信号接收延时;

13、ti表示所述数字i/o通道i在信号发送方向上的延时;

14、rj表示所述数字i/o通道j在信号接收方向上的延时;

15、m为测试信号从连接器到所述第一校准板或所述第二校准板上pcb走线连接点的延时。

16、作为本发明的一种优选方案,步骤s2中,以错“1”方式对步骤s1分得的各组进行重新分组的方法为:

17、s21,对步骤s1分得的每个分组进行排序;

18、s22,完成分组排序后,对每个分组中的各所述数字i/o通道进行排序,形成按序排列的序列;

19、s23,从所述序列中排序第二的所述数字i/o通道开始将所述半导体测试设备的各所述数字i/o通道重新分为若干组。

20、作为本发明的一种优选方案,步骤s23中,从所述序列中排序第二的所述数字i/o通道开始以与步骤s1相同的分组单位将所述半导体测试设备的各所述数字i/o通道重新分为若干组。

21、作为本发明的一种优选方案,步骤s2中,以错“1”方式分得的每组内的每个所述数字i/o通道在所述半导体测试设备与所述第二校准板间的布线长度相同。

22、作为本发明的一种优选方案,步骤s2中,以3个为一组对所述测试设备上的若干个所述数字i/o通道进行重新分组。

23、作为本发明的一种优选方案,所述数字i/o通道在所述半导体测试设备与所述第一校准板间的布线长度包括从所述半导体测试设备的i/o接口到连接器的接线长度以及从所述连接器到所述第一校准板上的pcb走线连接点的接线长度;

24、每个所述i/o接口到所述连接器的接线长度相同且从所述连接器引出的连接在所述第一校准板的pcb走线连接点上的每条接线的长度相同。

25、作为本发明的一种优选方案,所述数字i/o通道在所述半导体测试设备与所述第二校准板间的布线长度包括从所述半导体测试设备的i/o接口到连接器的接线长度以及从所述连接器到所述第二校准板上的pcb走线连接点的接线长度;

26、每个所述i/o接口到所述连接器的接线长度相同且从所述连接器引出的连接在所述第二校准板的pcb走线连接点上的每条接线的长度相同。

27、本发明提供的半导体测试设备的数字i/o通道校准方法简单,在不额外增加校准板的设计难度和制造成本的前提下,解决了测试设备的数字i/o通道间信号不同步的问题,且校准结果准确、可靠。

- 还没有人留言评论。精彩留言会获得点赞!