磁传感器的制作方法

1.本发明涉及磁传感器。

背景技术:

2.作为公报中记载的现有技术,存在下述磁阻抗效应元件,其具备:薄膜磁铁,其形成于非磁性基板上,并且由硬磁体膜形成;绝缘层,其将前述薄膜磁铁的上部覆盖;和感磁部,其形成于前述绝缘层上,被赋予了单轴各向异性,并且由一个或多个长方形的软磁体膜形成(参见专利文献1)。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2008-249406号公报

技术实现要素:

6.发明所要解决的课题

7.此外,具备通过磁阻抗效应来感应磁场的感应元件的磁传感器利用了阻抗相对于磁场发生变化这一点。为了提高磁传感器的灵敏度,要求阻抗相对于磁场的变化增大。

8.本发明的目的在于提高利用了磁阻抗效应的磁传感器的灵敏度。

9.用于解决课题的手段

10.应用了本发明的磁传感器具备非磁性的基板、和设置于基板上的感应元件,所述感应元件包含饱和磁化为300emu/cc以上且650emu/cc以下的、以co为主成分的非晶合金的软磁体层,并且,所述感应元件具有长边方向和短边方向,在与长边方向交叉的方向上具有单轴磁各向异性,并通过磁阻抗效应来感应磁场。

11.此处,其特征可以在于,软磁体层的饱和磁化为300emu/cc以上且550emu/cc以下。

12.另外,其特征可以在于,软磁体层的饱和磁化为300emu/cc以上且450emu/cc以下。

13.从其他观点来理解时,应用了本发明的磁传感器具备非磁性的基板、和设置于基板上的感应元件,所述感应元件包含zr为3at%、nb为17at%以上且低于21at%、余量为co的非晶合金的软磁体层,并且,所述感应元件具有长边方向和短边方向,在与长边方向交叉的方向上具有单轴磁各向异性,并通过磁阻抗效应来感应磁场。

14.此处,其特征可以在于,软磁体层中,nb高于17at%且低于21at%。

15.另外,其特征可以在于,软磁体层中,nb高于18at%且低于21at%。

16.对于这样的磁传感器而言,其特征可以在于,感应元件包含多个软磁体层,在多个软磁体层之间包含抑制在软磁体层中产生闭合磁畴的磁畴抑制层。

17.另外,其特征可以在于,感应元件包含多个软磁体层,在多个软磁体层之间包含导电性比软磁体层高的、非磁性的导电体层。

18.而且,其特征可以在于,感应元件包含多个软磁体层,在多个软磁体层之间包含使软磁体层进行反铁磁性耦合的、非磁性体的反铁磁性耦合层。

19.发明效果

20.根据本发明,能够提高利用了磁阻抗效应的磁传感器的灵敏度。

附图说明

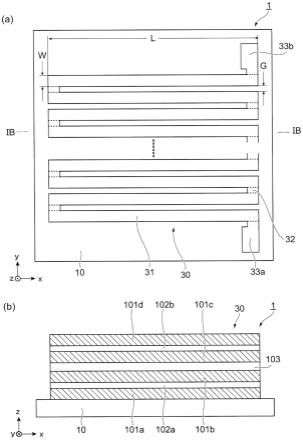

21.[图1]为对应用了本实施方式的磁传感器的一例进行说明的图。(a)为俯视图,(b)为沿(a)中的ib-ib线的截面图。

[0022]

[图2]为对在感应元件的感应部的长边方向上施加的磁场与感应元件的阻抗之间的关系进行说明的图。

[0023]

[图3]为示出对阻抗变化进行测定的测定电路的一例的图。

[0024]

[图4]为示出nb比率与灵敏度及各向异性磁场之间的关系的图。(a)为灵敏度,(b)为各向异性磁场。

[0025]

[图5]为示出软磁体层中的nb比率与饱和磁化之间的关系的图。

[0026]

[图6]为对饱和磁化与磁传感器的灵敏度之间的关系进行说明的图。

[0027]

[图7]为磁传感器的变形例的截面图。(a)为感应元件中的感应部由一层软磁体层构成的磁传感器,(b)为感应元件中的感应部由夹着磁畴抑制层的两层软磁体层构成的磁传感器,(c)为感应元件中的感应部由夹着导电体层的两层软磁体层构成的磁传感器。

[0028]

附图标记说明

[0029]

1、2、3、4

…

磁传感器,10

…

基板,30

…

感应元件,31

…

感应部,32

…

连接部,33、33a、33b

…

端子部,50

…

电桥电路,101、101a、101b、101c、101d

…

软磁体层,102、102a、102b

…

磁畴抑制层,103

…

导电体层,h

…

磁场,hb

…

偏置磁场,hk

…

各向异性磁场,ms

…

饱和磁化,p

…

交流电源,z

…

阻抗

具体实施方式

[0030]

以下,参照附图来对本发明的实施方式(下文中,记载为本实施方式。)进行说明。

[0031]

(磁传感器1的构成)

[0032]

图1为对应用了本实施方式的磁传感器1的一例进行说明的图。图1(a)为俯视图,图1(b)为沿图1(a)中的ib-ib线的截面图。图1(a)中,将纸面的右向作为x方向,将纸面的向上方向作为y方向,将纸面的表面方向作为z方向。图1(b)中,将纸面的右向作为x方向,将纸面的向上方向作为z方向,将纸面的背面方向作为y方向。

[0033]

如图1(b)所示,应用了本实施方式的磁传感器1具备非磁性的基板10、和设置于基板10上的感应元件30,所述感应元件30包含对磁场进行感应的软磁体层。

[0034]

需要说明的是,关于图1(b)所示的磁传感器1的截面结构,在后文中详细说明。

[0035]

此处,软磁体为所谓的矫顽力小的材料,即,容易被外部磁场磁化,但若去除外部磁场,则会迅速恢复到没有磁化或磁化小的状态。

[0036]

利用图1(a),对磁传感器1的平面结构进行说明。作为一例,磁传感器1具有四边形的平面形状。磁传感器1的平面形状为数mm见方。例如,x方向的长度为4mm~6mm,y方向的长度为3mm~5mm。需要说明的是,磁传感器1的平面形状的大小也可以为其他值。另外,磁传感器1的平面形状也可以为四边形以外的形状。

[0037]

接下来,对设置于基板10上的感应元件30进行说明。感应元件30具备平面形状为

具有长边方向和短边方向的长条状的多个感应部31。图1(a)中,x方向为感应元件30的长边方向。多个感应部31以长边方向并列的方式配置。而且,感应元件30具备将相邻的感应部31串联连接成曲折状的连接部32、和连接有用于供给电流的电线的端子部33。感应部31对磁场或磁场的变化进行感应从而产生磁阻抗效应。即,感应部31利用被串联连接的感应元件30的阻抗变化来测量磁场或磁场的变化。下文中,有时将感应元件30的阻抗记载为磁传感器1的阻抗。

[0038]

在图1(a)中图示了8根感应部31,但感应部31也可以不是8根。因此,图1(a)中,将纸面上侧的4根与纸面下侧的4根之间设为虚线,表示根数不限于8根。

[0039]

连接部32设置于相邻的感应部31的端部之间,将相邻的感应部31串联连接成曲折状。

[0040]

端子部33(端子部33a、33b)分别设置于未被连接部32连接的感应部31的2个端部。端子部33作为连接用于供给电流的电线的焊盘部而发挥功能。端子部33为能连接电线的大小即可。需要说明的是,端子部33(端子部33a、33b)在图1(a)的纸面中设置于右侧,但也可以设置于左侧,还可以分开设置在左右侧。

[0041]

此处,将感应部31的长边方向(x方向)的长度设为长度l。而且,将感应部31的短边方向的宽度设为宽度w。将相邻的感应部31间的间隔设为间隔g。感应部31的长度l例如为1mm~10mm,宽度w例如为10μm~150μm,间隔g例如为10μm~150μm。需要说明的是,各个感应部31的大小(长度l、宽度w、厚度等)、感应部31的数量、感应部31间的间隔g等根据待感应、即待测量的磁场的大小等来设定即可。需要说明的是,感应部31也可以为1个。

[0042]

接下来,利用图1(b),对磁传感器1的截面结构进行说明。

[0043]

基板10为由非磁体形成的基板,例如可举出玻璃、蓝宝石这样的氧化物基板、硅等半导体基板、或铝、不锈钢、实施了镍磷镀覆的金属等金属基板等。需要说明的是,在基板10的导电性高的情况下,在设置感应元件30的一侧的基板10的表面上设置将基板10与感应元件30电绝缘的绝缘体层为宜。作为构成这样的绝缘体层的绝缘体,可举出sio2、al2o3、tio2等氧化物、或si3n4、aln等氮化物等。此处,将基板10设定为玻璃来进行说明。

[0044]

作为一例,感应元件30从基板10侧起具备4层软磁体层101a、101b、101c、101d。而且,感应元件30在软磁体层101a与软磁体层101b之间具备抑制在软磁体层101a和软磁体层101b中产生闭合磁畴的磁畴抑制层102a。此外,感应元件30在软磁体层101c与软磁体层101d之间具备抑制在软磁体层101c和软磁体层101d中产生闭合磁畴的磁畴抑制层102b。而且,感应元件30在软磁体层101b与软磁体层101c之间具备使感应元件30的电阻(此处,称为电阻值。)降低的导电体层103。在不将软磁体层101a、101b、101c、101d分别区分开的情况下,记载为软磁体层101。在不将磁畴抑制层102a、102b分别区分开的情况下,记载为磁畴抑制层102。

[0045]

软磁体层101由显示磁阻抗效应的非晶合金的软磁体构成。软磁体层101的厚度例如为100nm~1μm。应用了本实施方式的感应元件30中,软磁体层101由饱和磁化为300emu/cc以上且650emu/cc以下的、以co为主成分的非晶合金的软磁体构成。关于软磁体层101,在后文中详细说明。

[0046]

需要说明的是,本说明书中,所谓非晶合金、非晶金属,是指具备不具有晶体那样的原子有序排列的结构、利用溅射法等形成的物质。

[0047]

磁畴抑制层102抑制在夹着磁畴抑制层102的上下的软磁体层101中产生闭合磁畴。

[0048]

通常,在软磁体层101中,容易形成各自的磁化的方向不同的多个磁畴。在该情况下,形成磁化的方向呈环状的闭合磁畴。若外部磁场变大,则磁壁移动,外部磁场的方向与磁化的方向相同的磁畴的面积变大,外部磁场的方向与磁化的方向相反的磁畴的面积变小。而且,若外部磁场进一步变大,则在磁化的方向与外部磁场的方向不同的磁畴中,以磁化的方向与外部磁场的方向朝向相同方向的方式发生磁化旋转。而且,最终,在相邻的磁畴彼此之间存在的磁壁消失,成为1个磁畴(单磁畴)。即,若形成了闭合磁畴,则产生构成闭合磁畴的磁壁伴随着外部磁场的变化以阶梯状不连续地移动的巴克豪森效应。该磁壁的不连续移动成为磁传感器1中的噪声,有可能发生从磁传感器1得到的输出中的s/n的降低。磁畴抑制层102抑制在设置于磁畴抑制层102上下的软磁体层101中形成面积小的多个磁畴。由此,可抑制闭合磁畴的形成,从而抑制由磁壁不连续地移动而导致的噪声的产生。需要说明的是,对于磁畴抑制层102而言,与不含磁畴抑制层102的情况相比,可获得所形成的磁畴的数量变少、即磁畴的大小变大的效果即可。

[0049]

作为这样的磁畴抑制层102,可举出ru、sio2等非磁体、crti、alti、crb、crta、cow等非磁性非晶金属。这样的磁畴抑制层102的厚度例如为10nm~100nm。

[0050]

导电体层103降低感应元件30的电阻。即,导电体层103的导电性比软磁体层101高,与不含导电体层103的情况相比,使感应元件30的电阻减小。由感应元件30感应的磁场或磁场的变化利用在2个端子部33a、33b间流通交流电流时的阻抗(下文中,记载为阻抗z。)的变化(记载为δz。)来测量。此时,交流电流的频率越高,则相对于外部磁场的变化(此处,记载为δh。)而言的阻抗z的变化率δz/δh(以下为阻抗变化率δz/δh)越大。但是,若在不含导电体层103的状态下增高交流电流的频率,则由于磁传感器1所具有的寄生电容,使得阻抗变化率δz/δh反而变小。即,若将感应元件30的电阻设为r,将寄生电容设为c,使感应元件30为电阻r与寄生电容c的并联电路,则磁传感器1的弛豫频率f0由式(1)表示。

[0051]

[数学式1]

[0052][0053]

由式(1)可知,若寄生电容c大,则弛豫频率f0变小。因此,若使交流电流的频率比弛豫频率f0高,则阻抗变化率δz/δh反而降低。因此,设置导电体层103,使感应元件30的电阻r降低,从而增高了弛豫频率f0。

[0054]

作为这样的导电体层103,优选使用导电性高的金属或合金,更优选使用导电性高且非磁性的金属或合金。作为这样的导电体层103,可举出al、cu、ag、au等金属。导电体层103的厚度例如为10nm~1μm。对于导电体层103而言,与不含导电体层103的情况相比,能降低感应元件30的电阻即可。

[0055]

需要说明的是,夹着磁畴抑制层102的上下的软磁体层101、及夹着导电体层103的上下的软磁体层101彼此进行了反铁磁性耦合(afc:antiferromagnetically coupled)。通过使上下的软磁体层101进行反铁磁性耦合,从而反磁场得以抑制,磁传感器1的灵敏度得以提高。

[0056]

磁传感器1可如下所述地制造。

[0057]

首先,在基板10上,利用已知的光刻技术形成在基板10的表面上将除感应元件30的平面形状的部分以外的部分覆盖的光致抗蚀剂图案。接着,利用例如溅射法,在基板10上依次堆积软磁体层101a、磁畴抑制层102a、软磁体层101b、导电体层103、软磁体层101c、磁畴抑制层102b、软磁体层101d。然后,将堆积于光致抗蚀剂上的软磁体层101a、磁畴抑制层102a、软磁体层101b、导电体层103、软磁体层101c、磁畴抑制层102b、软磁体层101d与光致抗蚀剂一同除去。于是,在基板10上残留有已被加工成感应元件30的平面形状的、由软磁体层101a、磁畴抑制层102a、软磁体层101b、导电体层103、软磁体层101c、磁畴抑制层102b、软磁体层101d形成的层叠体。即,形成了感应元件30。

[0058]

对于软磁体层101,沿着与长边方向交叉的方向、例如短边方向(图1(a)的y方向)赋予了单轴磁各向异性。需要说明的是,所谓与长边方向交叉的方向,相对于长边方向具有超过45

°

且为90

°

以下的角度即可。单轴磁各向异性可以通过下述方式来赋予:针对形成于基板10上的感应元件30,进行例如3kg(0.3t)的旋转磁场中的400℃下的热处理(旋转磁场中热处理)、和继其之后的3kg(0.3t)的静磁场中的400℃下的热处理(静磁场中热处理)。对于单轴磁各向异性的赋予,也可以在构成感应元件30的软磁体层101的堆积时利用磁控溅射法而进行,来代替通过旋转磁场中热处理及静磁场中热处理而进行。即,通过磁控溅射法中使用的磁铁(磁石)所形成的磁场,在软磁体层101的堆积的同时,对软磁体层101赋予单轴磁各向异性。

[0059]

在以上说明的制造方法中,连接部32、端子部33与感应部31同时作为一体而形成。需要说明的是,可以利用导电性的al、cu、ag、au等金属形成连接部32、端子部33。另外,也可以在与感应部31同时一体地形成的连接部32、端子部33上层叠导电性的al、cu、ag、au等金属。

[0060]

(感应元件30的动作)

[0061]

对感应元件30的作用进行说明。

[0062]

图2为对在感应元件30的感应部31的长边方向(图1(a)的x方向)上施加的磁场h与感应元件30的阻抗z之间的关系进行说明的图。图2中,横轴为磁场h,纵轴为阻抗z。需要说明的是,对于阻抗z而言,在图1(a)所示的感应元件30的端子部33a、33b间流通交流电流来进行测定。

[0063]

如图2所示,感应元件30的阻抗z随着在感应部31的长边方向上施加的磁场h变大而变大。而且,感应元件30的阻抗z在施加的磁场h较之各向异性磁场hk变大时反而变小。在小于各向异性磁场hk的范围内,使用阻抗z的变化量δz相对于磁场h的变化量δh大的部分、即阻抗变化率δz/δh陡峭的部分(大)时,能够将磁场h的微弱变化作为阻抗z的变化量δz而提取出来。图2中,将阻抗变化率δz/δh大的磁场h的中心表示为磁场hb。即,能够高精度地测量磁场hb的附近(图2中箭头所示的范围)的磁场h的变化量δh。此处,将阻抗z的变化量δz最陡峭的(阻抗变化率δz/δh最大)部分、即磁场hb中的每单位磁场的阻抗的变化量zmax除以磁场hb处的阻抗z(记载为阻抗zb。)而得到的值(zmax/zb)为灵敏度。灵敏度zmax/zb越高,则磁阻抗效应越大,越容易测量磁场或磁场的变化。换言之,相对于磁场h而言的阻抗z的变化越陡峭,则灵敏度zmax/zb越高。为此,各向异性磁场hk越小越好。即,磁传感器1中,优选灵敏度zmax/zb高,为此,优选各向异性磁场hk小。磁场hb有时被称为偏置磁场。下文中,将磁场hb记载为偏置磁场hb。

[0064]

(灵敏度zmax/zb的测定方法)

[0065]

图3为示出对阻抗变化进行测定的测定电路的一例的图。图3所示的测定电路为电桥电路50。电桥电路50具备端子a、b、c、d。而且,端子a-b间、端子c-d间、端子d-a间被设定为阻抗z。在端子b-c间设置有阻抗发生变化的试样s。即,构成电桥的4条边中,在3条边设定了阻抗z,在剩余的1条边设定了试样s。在端子a-c间连接有供给交流电流的交流电源p。端子a-c间为电压vin。而且,在电桥电路50中,测定端子b-d间的电压δv。

[0066]

此处,对于试样s而言,使阻抗从z变化为z+δz。试样s为阻抗z时,电桥电路50中的4条边为阻抗z。因此,电桥电路50为平衡状态,在端子b-d间不产生电压。即,δv为0v。另一方面,若试样s变为阻抗z+δz,则δv变为δz/(4z)

×

vin(δv≈δz/(4z)

×

vin)。

[0067]

在使试样s为磁传感器1、并施加有偏置磁场hb的状态的情况下,δh=1时的上述δz/z对应于灵敏度zmax/zb(δz/z=zmax/zb)。如此,磁传感器1的灵敏度zmax/zb可利用电桥电路50来测量。需要说明的是,磁传感器1的灵敏度zmax/zb也可以利用电桥电路50以外的方法来测定。

[0068]

(nb比率与灵敏度zmax/zb之间的关系)

[0069]

在此之前,如现有技术文献1中记载的那样,作为构成利用了磁阻抗效应的磁传感器1的软磁体层101的软磁体,使用了nb为12at%、zr为3at%、余量为co的co

85

nb

12

zr3(有时记载为co12nb3zr。)。然而发现,提高nb的比率时,灵敏度zmax/zb得以提高。下文中,不记载co、nb、zr的比率的情况下,记载为conbzr。

[0070]

图4为示出nb比率与灵敏度zmax/zb及各向异性磁场hk之间的关系的图。图4(a)为灵敏度zmax/zb,图4(b)为各向异性磁场hk。图4(a)中,横轴为nb比率(at%),纵轴为灵敏度zmax/zb(/oe)。图4(b)中,横轴为nb比率(at%),纵轴为各向异性磁场hk(oe)。

[0071]

对于磁传感器1而言,使感应元件30中的感应部31的根数为24根,使感应部31的长度l为4mm,使感应部31的宽度w为100μm,使感应部31间的间隔g为50μm。

[0072]

软磁体层101a、101b、101c、101d(参见图1(b))是作为以co为主成分的非晶合金的conbzr,使nb比率变化为12、17、18、19、20at%。需要说明的是,zr比率固定为3at%。即,与nb比率的增加相应地,使co比率减少。使软磁体层101a、101b、101c、101d的各厚度为500nm。

[0073]

磁畴抑制层102a、102b(参见图1(b))是原子数比为1:1的crti。使磁畴抑制层102a、102b的各厚度为25nm。

[0074]

导电体层103(参见图1(b))为ag。使导电体层103的厚度为400nm。

[0075]

如图4(a)所示,若nb比率增加,则灵敏度zmax/zb得以提高。另一方面,如图4(b)所示,若nb比率增加,则各向异性磁场hk变小。即,由于各向异性磁场hk变小,使得相对于磁场h而言的阻抗z的变化变得陡峭。由此,认为灵敏度zmax/zb得以提高。

[0076]

(nb比率与饱和磁化ms之间的关系)

[0077]

图5为示出软磁体层101中的nb比率与饱和磁化ms之间的关系的图。图5中,横轴为nb比率(at%),纵轴为饱和磁化ms(emu/cc)。此处,在基板10上设置软磁体层101,对饱和磁化ms进行测定。将磁壁因磁场而消失的状态称为磁化饱和。而且,将磁化已饱和的状态的磁化称为饱和磁化ms。

[0078]

图5中,除了conbzr(黑圆圈)以外,还增加了记载为cofecr mnsib(白圆圈)的、以co为主成分的非晶合金。需要说明的是,cofecrmnsib中,fe为1.4at%,si为13.8at%,mn为

3.6at%,cr为5at%,b为9.5at%,余量为co。即,此处所示的cofecrmnsib为co

66.7

fe

1.4

cr5mn

3.6

si

13.8b9.5

(有时记载为co1.4fe5cr3.6mn13.8si9.5b。)。

[0079]

另外,图5中,还示出了conbzr中nb比率为21at%的情况。

[0080]

如图5所示,对于conbzr而言,随着nb比率变大,饱和磁化ms变小。即,容易发生由磁场导致的磁化的饱和。另外,cofecrmnsib的饱和磁化ms为390emu/cc,与nb为19at%的conbzr的421emu/cc、nb为20at%的conbzr的365emu/cc相近。

[0081]

需要说明的是,对于nb为21at%的conbzr而言,饱和磁化ms为284emu/cc这样小,但在制成磁传感器1的情况下,各向异性磁场hk变得过小,未能作为磁传感器来工作。认为这是因为,若饱和磁化ms过小,则难以赋予单轴各向异性。

[0082]

(饱和磁化ms与灵敏度zmax/zb之间的关系)

[0083]

图6为对饱和磁化ms与磁传感器1的灵敏度zmax/zb之间的关系进行说明的图。图6中,横轴为饱和磁化ms(emu/cc),纵轴为灵敏度zmax/zb(/oe)。此处,示出了前述的nb比率(at%)不同的conbzr(黑圆圈)、和cofecrmnsib(白圆圈)。需要说明的是,关于conbzr,将nb比率(at%)示于()内。此外,使用了cofecrmnsib的磁传感器1具有图1所示的结构。其中,使软磁体层101a、101b、101c、101d的各厚度为250nm。

[0084]

如图6所示,在饱和磁化ms为300emu/cc以上且650emu/cc以下时,与nb比率为12at%时的饱和磁化ms为801emu/cc的情况相比,灵敏度zmax/zb得以提高。这并不限于软磁体层101由conbzr构成的情况,即使在软磁体层101由cofecrmnsib构成的情况下也符合。由此表明,对于利用了磁阻抗效应的磁传感器1而言,若以co为主成分的软磁体层101的饱和磁化ms为300emu/cc以上且650emu/cc以下,则灵敏度zmax/zb得以提高。此处,所谓co为主成分,是指co比率为60at%以上。需要说明的是,如前文所述,若饱和磁化ms低于300emu/cc,则各向异性磁场hk变得过小,因此不优选。

[0085]

另外,如图4(b)所示,若nb比率高于17at%,则各向异性磁场hk进一步降低。另一方面,如图6所示,nb比率高于17at%的情况下,饱和磁化ms为550emu/cc以下,因此,更优选使用饱和磁化ms为300emu/cc以上且550emu/cc以下的、以co为主成分的软磁体层101。此外,如图6所示,若饱和磁化ms为450emu/cc以下,则灵敏度zmax/zb变得更高,因此,进一步优选使用饱和磁化ms为300emu/cc以上且450emu/cc以下的、以co为主成分的软磁体层101。

[0086]

conbzr中,nb比率优选为17at%以上且低于21at%。需要说明的是,如前文所述,若nb比率为21at%以上,则各向异性磁场hk变得过小,因此不优选。另外,如图4(b)所示,若nb比率高于17at%,则各向异性磁场hk进一步降低,因此更优选nb比率高于17at%且低于21at%。此外,如图6所示,若nb比率高于18at%,则灵敏度zmax/zb进一步变高,因此,进一步优选nb比率高于18at%且低于21at%。

[0087]

(变形例)

[0088]

图7为磁传感器1的变形例的截面图。图7(a)为感应元件30中的感应部31由一层软磁体层101构成的磁传感器2,图7(b)为感应元件30中的感应部31由夹着磁畴抑制层102的两层软磁体层101构成的磁传感器3,图7(c)为感应元件30中的感应部31由夹着导电体层103的两层软磁体层101构成的磁传感器4。需要说明的是,在图7(a)、图7(b)、图7(c)中,与图1所示的磁传感器1同样的部分标注了相同的附图标记。

[0089]

感应部31可以如图7(a)所示那样由一层软磁体层101构成,也可以如图7(b)所示

那样由夹着磁畴抑制层102的两层软磁体层101构成,还可以如图7(c)所示那样由夹着导电体层103的两层软磁体层101构成。另外,感应部31也可以利用三层以上的软磁体层101来设置。

[0090]

另外,可以使用使上下的软磁体层101进行反铁磁性耦合的反铁磁性耦合层来代替图7(b)中的磁畴抑制层102。另外,也可以将图1(b)所示的磁传感器1中的磁畴抑制层102a、102b作为反铁磁性耦合层。如前文所述,磁畴抑制层102抑制闭合磁畴的产生,并且使上下的软磁体层101进行反铁磁性耦合。所谓反铁磁性耦合层,是不具有抑制闭合磁畴的产生的功能、或者抑制闭合磁畴的产生的功能弱的层。通过具有反铁磁性耦合层,从而上下的软磁体层101进行反铁磁性耦合,由此反磁场得以抑制,磁传感器的灵敏度zmax/zb得以提高。作为这样的反铁磁性耦合层,可举出ru或ru合金。

[0091]

而且,感应部31可以包含磁畴抑制层102、导电体层103及反铁磁性耦合层这样的多个层。

[0092]

此外,在磁传感器1~4中,可以在基板10与感应元件30之间设置施加偏置磁场hb(参见图2)的、由硬磁体层构成的磁铁(下文中,记载为薄膜磁铁。)。硬磁体为所谓的矫顽力大的材料,即,若被外部磁场磁化,则即使去除外部磁场也保持被磁化了的状态。对于薄膜磁铁而言,磁极n、s以磁通沿感应元件30中的感应部31的长边方向透过的方式设置即可。需要说明的是,即使在基板10与感应元件30之间设置有薄膜磁铁的情况下,也将基板10和薄膜磁铁一起作为基板。

[0093]

以上,对本发明的实施方式进行了说明,但本发明不限定于本实施方式。只要不违反本发明的主旨,则可以进行各种变形、组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1