一种确定复合门电路毛刺功耗的方法、装置、电子设备与流程

本说明书涉及计算机,尤其涉及一种确定复合门电路毛刺功耗的方法、装置、电子设备。

背景技术:

1、毛刺信号(glitch)是指在逻辑门电路中信号无效翻转的现象,电路中可能因为多种情况引起毛刺信号的产生,毛刺信号对应的无效翻转会带来一定功耗。由于毛刺信号的功耗可能会影响到芯片设计,如会影响到供电金属线的宽度,以及外部封装、板级的设计,因此在芯片设计阶段,需要对芯片中毛刺的功耗进行计算,进而基于计算结果对芯片的性能进行分析。

2、目前,业界在计算毛刺信号的功耗时,通常是在逻辑门的输出端出现毛刺信号时才对该毛刺信号的功耗进行计算,但是在具有多级门结构的复合门电路中,毛刺信号往往不会出现在复合门电路的输出端,而是会在复合门电路内部出现并造成一定的功耗,现有技术中会对这部分的功耗进行忽略,然而随着芯片中复合门电路的快速增长,如果仍然采用现有的方式计算毛刺的功耗,则会忽略掉大部分功耗,导致实际功耗与计算出的功耗相差较大,因此,亟需一种新的确定复合门电路毛刺功耗的方法。

技术实现思路

1、针对上述技术问题,本说明书提供一种确定复合门电路毛刺功耗的方法及装置,技术方案如下。

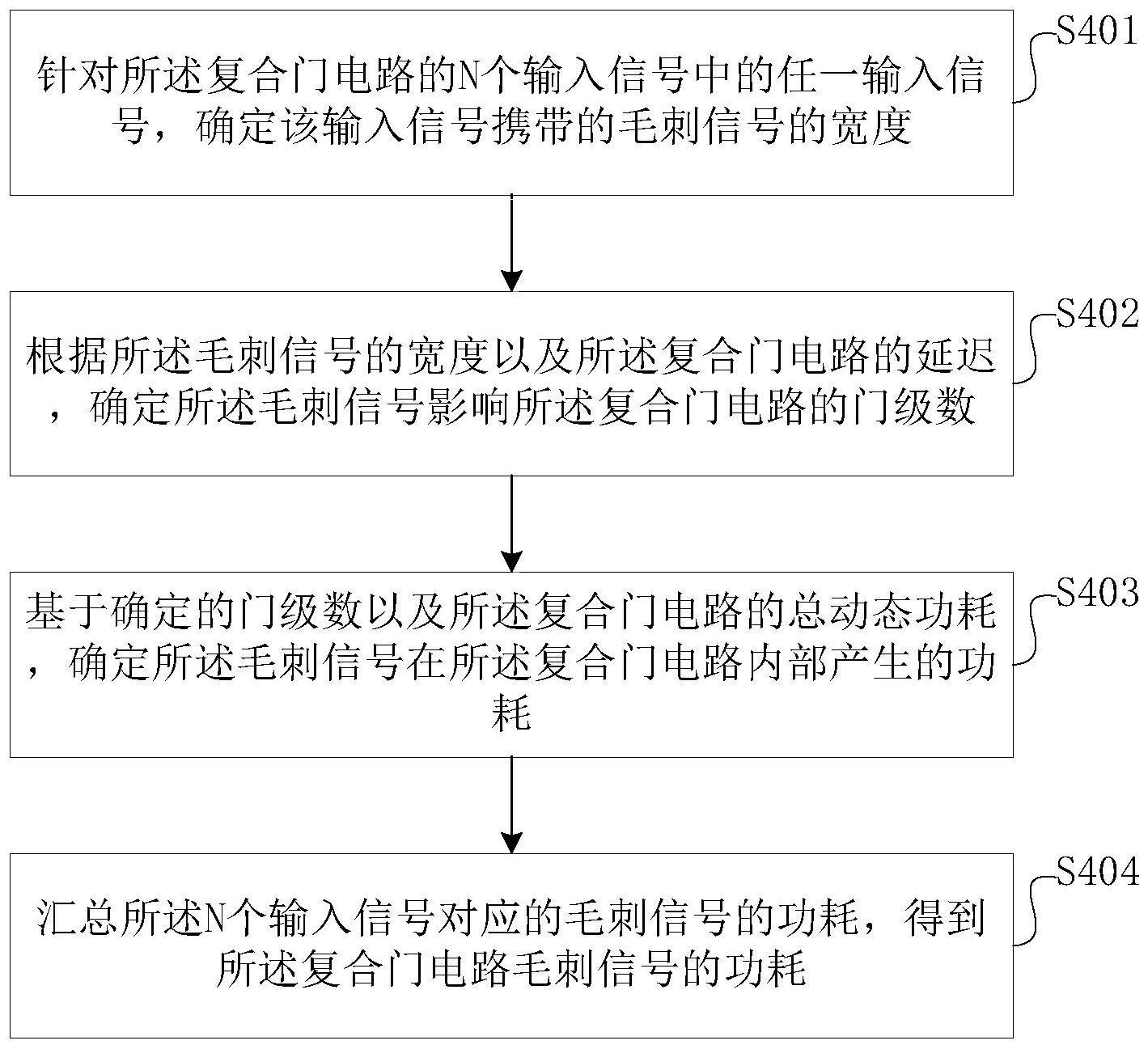

2、根据本说明书的第一方面,提供一种确定复合门电路毛刺功耗的方法,包括:

3、针对所述复合门电路的n个输入信号中的任一输入信号,确定该输入信号携带的毛刺信号的宽度;

4、根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级数;

5、基于确定的门级数以及所述复合门电路的总动态功耗,确定所述毛刺信号在所述复合门电路内部产生的功耗;

6、汇总所述n个输入信号对应的毛刺信号的功耗,得到所述复合门电路毛刺信号的功耗。

7、在一个实施例中,所述根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级数,包括:

8、确定所述复合门电路的门级数;

9、根据所述复合门电路的门级数以及所述复合门电路的延迟,确定每一级门所对应的延迟;

10、根据所述毛刺信号的宽度以及每一级门所对应的延迟确定所述毛刺影响所述复合门电路的门级数。

11、在一个实施例中,所述根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级数,包括:

12、根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级比重;

13、确定所述复合门电路的门级数;

14、利用所述门级比重以及所述复合门电路的门级数确定所述毛刺信号影响所述复合门电路的门级数。

15、在一个实施例中,所述确定所述复合门电路的门级数,包括:

16、根据复合门电路的输入信号个数n,采用以下公式确定所述复合门电路的门级数l:

17、在一个实施例中,所述基于确定的门级数以及所述复合门电路的总动态功耗,确定所述毛刺信号在所述复合门电路内部产生的功耗,包括:

18、确定复合门电路中的门个数q;

19、基于所述门个数q以及所述复合门电路的总动态功耗p,确定每个门的功耗p0;

20、基于每个门的功耗p0以及所述毛刺信号影响所述复合门电路的门级数b,采用以下公式计算所述毛刺信号在所述复合门电路内部的产生功耗px:

21、

22、根据本申请实施例的第二个方面,提供了一种确定复合门电路毛刺功耗的装置,所述复合门电路包括至少两级门,以及n个输入信号,所述装置包括:

23、宽度确定模块,用于针对所述复合门电路的n个输入信号中的任一输入信号,确定该输入信号携带的任一毛刺信号的宽度;

24、级数确定模块,用于根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级数;

25、功耗确定模块,用于基于确定的门级数以及所述复合门电路的总动态功耗,确定所述毛刺信号在所述复合门电路内部产生的功耗;

26、汇总模块,用于汇总所述n个输入信号对应的毛刺信号的功耗,得到所述复合门电路毛刺信号的功耗。

27、在一个实施例中,所述级数确定模块,具体用于确定所述复合门电路的门级数;根据所述复合门电路的门级数以及所述复合门电路的延迟,确定每一级门所对应的延迟;根据所述毛刺信号的宽度以及每一级门所对应的延迟确定所述毛刺影响所述复合门电路的门级数。

28、在一个实施例中,所述级数确定模块,具体用于根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级比重;确定所述复合门电路的门级数;利用所述门级比重以及所述复合门电路的门级数确定所述毛刺信号影响所述复合门电路的门级数。

29、在一个实施例中,所述级数确定模块,具体用于根据复合门电路的输入信号个数n,采用以下公式确定所述复合门电路的门级数l:

30、在一个实施例中,所述功耗确定模块,具体用于确定复合门电路中的门个数q;

31、基于所述门个数q以及所述复合门电路的总动态功耗p,确定每个门的功耗p0;

32、基于每个门的功耗p0以及所述毛刺信号影响所述复合门电路的门级数b,采用以下公式计算所述毛刺信号在所述复合门电路内部的产生功耗px:

33、

34、根据本申请实施例的第三个方面,提供了一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,其中,所述处理器执行所述程序时实现上述确定复合门电路毛刺功耗的方法。

35、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本说明书。

技术特征:

1.一种确定复合门电路毛刺功耗的方法,所述复合门电路包括至少两级门,以及n个输入信号,所述方法包括:

2.根据权利要求1所述的方法,所述根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级数,包括:

3.根据权利要求1所述的方法,所述根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级数,包括:

4.根据权利要求2或权利要求3任一项所述的方法,所述确定所述复合门电路的门级数,包括:

5.根据权利要求1所述的方法,所述基于确定的门级数以及所述复合门电路的总动态功耗,确定所述毛刺信号在所述复合门电路内部产生的功耗,包括:

6.一种确定复合门电路毛刺功耗的装置,所述复合门电路包括至少两级门,以及n个输入信号,所述装置包括:

7.根据权利要求6所述的装置,

8.根据权利要求6所述的装置,

9.根据权利要求7或权利要求8任一项所述的装置,

10.根据权利要求6所述的装置,

11.一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,其中,所述处理器执行所述程序时实现如权利要求1至5任一项所述的方法。

技术总结

本说明书提供了一种确定复合门电路毛刺功耗的方法,所述复合门电路包括至少两级门,以及N个输入信号,所述方法包括:针对所述复合门电路的N个输入信号中的任一输入信号,确定该输入信号携带的毛刺信号的宽度;根据所述毛刺信号的宽度以及所述复合门电路的延迟,确定所述毛刺信号影响所述复合门电路的门级数;基于确定的门级数以及所述复合门电路的总动态功耗,确定所述毛刺信号在所述复合门电路内部产生的功耗;汇总所述N个输入信号对应的毛刺信号的功耗,得到所述复合门电路毛刺信号的功耗。

技术研发人员:张涛

受保护的技术使用者:象帝先计算技术(重庆)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!