用于芯片测试的插座组件以及芯片测试系统的制作方法

本公开主要涉及芯片测试,更具体地,涉及用于芯片测试的插座组件以及包括该插座组件的芯片测试系统。

背景技术:

1、芯片测试是在芯片制造期间或在制造后对芯片进行测试,以验证芯片的功能和性能,从而确保芯片的良品率。芯片测试过程中需要使用专门的设备或装置来完成芯片的测试。例如,可以提供芯片测试分选机(handler)、测试夹具或插座(socket)以及测试机(tester)等设备。在测试过程中,可以将芯片压到用于接纳芯片的测试夹具或插座(socket)上,以使芯片的焊球或引脚经由插座连接到测试机,从而利用测试机来对芯片的各种功能和性能进行测试。

2、这些专门的设备或装置通常可以测试一批或多批芯片。如果测试过程中出现异常操作或者这些设备或装置的性能出现问题,可能会影响大量芯片的测试结果,甚至会造成很多芯片的损坏。然而,目前对于测试过程中的操作异常或者用于测试的设备或装置的异常,缺乏有效和实时的监测手段。

技术实现思路

1、为了解决上述问题,本公开的实施例提供了一种用于芯片测试的改进插座组件以及包括该插座组件的芯片测试系统。

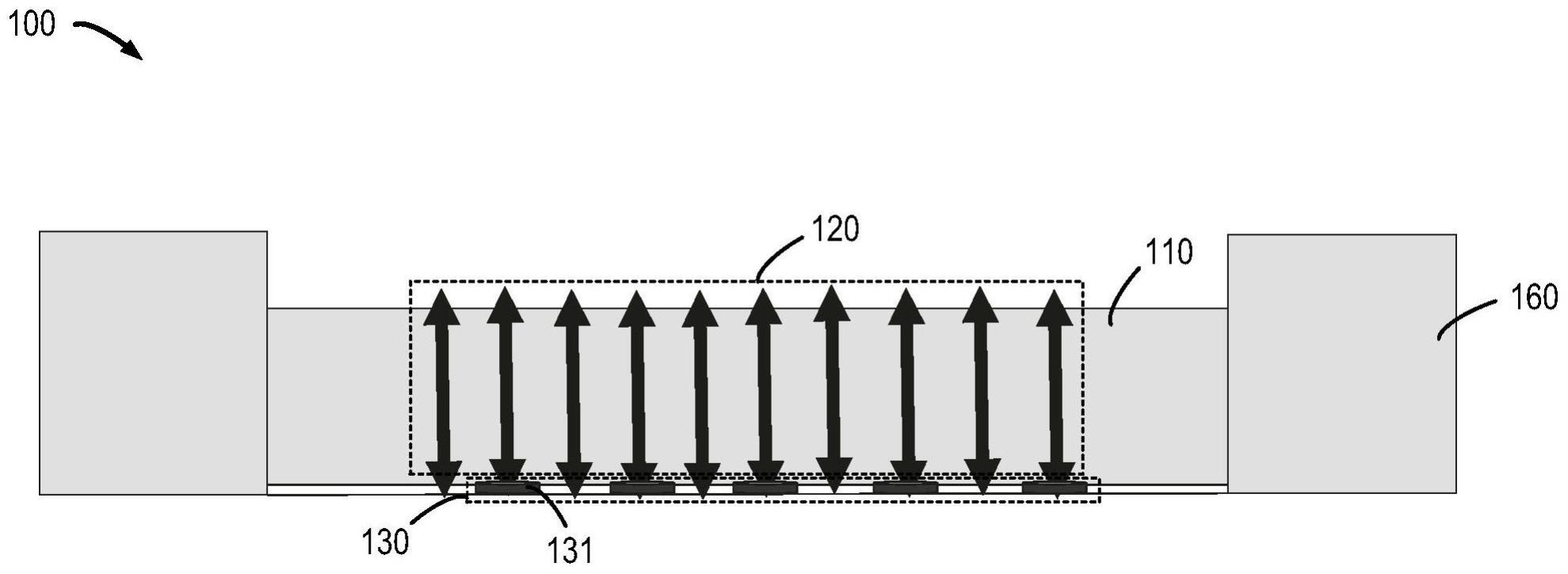

2、在本公开的第一方面,提供了用于芯片测试的插座组件,该插座组件包括:第一本体;多个第一探针,穿过第一本体,多个第一探针适于在第一本体的第一表面处受到待测试芯片按压、并且在第一本体的第二表面处按压测试设备,以电连接待测试芯片和测试设备;以及压力感测装置,被布置为感测多个第一探针中的至少一部分第一探针所承受的压力。

3、在本公开的方案中,通过在插座组件中设置压力感测装置,可以在芯片测试期间对待测试芯片所承受的压力进行实时监测,从而避免压力异常造成的质量事故。此外,借助于压力感测装置,还可以对用于芯片测试的无源硬件设备进行编码和标识,并且可以对无源硬件设备的使用次数进行精确计数以评估磨损状况。

4、在本公开的某些实施例中,压力感测装置包括多个第一压力感测元件,每个第一压力感测元件被布置在对应的第一探针处。在该实施例中,通过感测第一探针的压力或形变,可以实时准确地获得待测试芯片的压力分布状况。

5、在本公开的某些实施例中,每个第一压力感测元件被布置在对应的第一探针的邻近测试设备的位置处。通过该实施例,可以更敏感地感测到第一探针的形变,从而准确感测压力。

6、在本公开的某些实施例中,多个第一压力感测元件的数目等于或少于多个第一探针的数目。通过该实施例,可以在确保监测效果的情况下,尽可能地降低监测成本。

7、在本公开的某些实施例中,多个第一压力感测元件以均匀分布的方式布置到多个第一探针处。在该实施例中,可以使用相对少量的第一压力感测元件来获取芯片的压力分布状况。

8、在本公开的某些实施例中,多个第一压力感测元件中的至少一部分第一压力感测元件被布置在与待测试芯片的高速引脚相对应的第一探针处。通过该实施例,可以更精确地监测对接触电阻要求较高的高速引脚处的压力情况,以避免影响测试过程中的信号传输。

9、在本公开的某些实施例中,插座组件还包括:第二本体,适于布置在待测试芯片的背离第一本体的一侧;多个第二探针,穿过第二本体,多个第二探针适于在第二本体的第一表面处受到施压设备按压、并且在第二本体的第二表面处按压待测试芯片,以电连接施压设备和待测试芯片;框体,环绕并固接至第一本体;以及至少一个第三探针,穿过框体,至少一个第三探针适于在框体的第一表面处受到施压设备按压、并且在框体的第二表面处按压测试设备,以电连接施压设备和测试设备。通过该实施例,可以对与芯片顶面引脚或焊球相关联的功能进行测试,并且可以对芯片顶面上方的无源硬件设备的使用次数进行计数以及标识无源硬件设备。

10、在本公开的某些实施例中,压力感测装置还包括多个第二压力感测元件,多个第二压力感测元件被布置在第一本体中,并且适于受到待测试芯片的下基底环按压。在该实施例中,通过布置第二压力感测元件,可以更全面的感测待测试芯片的承压状况。

11、在本公开的第二方面,提供了一种芯片测试系统,该芯片测试系统包括:根据第一方面的插座组件;测试设备;以及施压设备,被配置为朝向测试设备按压待测试芯片和插座组件。

12、在本公开的某些实施例中,测试设备被配置为基于来自压力感测装置的信号指示压力超过第一阈值而发出警报、或者向施压设备发出指令以停止按压操作。通过该实施例,可以在芯片测试出现异常时及时发出提示或停止测试,从而可以对硬件设备进行维护或更换,以避免造成大量芯片损坏的测试质量事故。

13、在本公开的某些实施例中,测试设备被配置为基于来自压力感测装置的信号来标识第一本体和多个第一探针。通过该实施例,有利于对芯片组件进行管理。

14、在本公开的某些实施例中,测试设备被配置为基于来自压力感测装置的信号指示压力超过第二阈值而将第一本体和多个第一探针的已使用次数加一。通过该实施例,可以精确统计芯片组件中的部件的使用次数,从而准确评估部件的磨损情况。

15、在本公开的某些实施例中,测试设备被配置为基于至少一个第三探针的连通信号来标识第二本体和多个第二探针。通过该实施例,可以对芯片顶面上方的插座组件的部件进行标识,从而有利于芯片组件的管理。

16、在本公开的某些实施例中,测试设备被配置为基于接收到至少一个第三探针的连通信号而将第二本体和多个第二探针的已使用次数加一。通过该实施例,可以精确统计芯片顶面上方的插座组件的部件的使用次数,从而准确评估部件的磨损情况。

17、在本公开的某些实施例中,测试设备包括测试机和附接到测试机的第一电路板,并且第一电路板包括将压力感测装置电连接到测试机的布线。通过该实施例,有助于将压力感测装置的指示压力的信号传递到测试设备。

18、在本公开的某些实施例中,施压设备包括推压头,并且推压头适于按压待测试芯片的裸片。通过该实施例,有助于对裸片外露的芯片进行测试。

19、在本公开的某些实施例中,其中施压设备还包括附接到推压头的第二电路板。通过该实施例中,有助于在对与芯片顶面引脚或焊球相关联的功能进行测试期间传递测试信号。

20、应当理解,

技术实现要素:

部分中所描述的内容并非旨在限定本公开的实施例的关键或重要特征,亦非用于限制本公开的范围。本公开的其它特征将通过以下的描述变得容易理解。

技术特征:

1.一种用于芯片测试的插座组件(100),包括:

2.根据权利要求1所述的插座组件(100),其中所述压力感测装置(130)包括多个第一压力感测元件(131),每个第一压力感测元件(131)被布置在对应的第一探针(120)处。

3.根据权利要求2所述的插座组件(100),其中每个第一压力感测元件(131)被布置在对应的第一探针(120)的邻近所述测试设备(200)的位置处。

4.根据权利要求2或3所述的插座组件(100),其中所述多个第一压力感测元件(131)的数目少于或等于所述多个第一探针(120)的数目。

5.根据权利要求4所述的插座组件(100),其中所述多个第一压力感测元件(131)以均匀分布的方式布置到所述多个第一探针(120)处。

6.根据权利要求4所述的插座组件(100),其中所述多个第一压力感测元件(131)中的至少一部分第一压力感测元件被布置在与所述待测试芯片(2000)的高速引脚相对应的第一探针处。

7.根据权利要求1所述的插座组件(100),还包括:

8.根据权利要求7所述的插座组件(100),其中所述压力感测装置(130)还包括多个第二压力感测元件(132),所述多个第二压力感测元件(132)被布置在所述第一本体(110)中,并且适于受到所述待测试芯片(2000)的下基底环(2400)按压。

9.一种芯片测试系统(1000),包括:

10.根据权利要求9所述的芯片测试系统(1000),其中所述测试设备(200)被配置为基于来自所述压力感测装置(130)的信号指示压力超过第一阈值而发出警报、或者向所述施压设备(300)发出指令以停止按压操作。

11.根据权利要求9所述的芯片测试系统(1000),其中所述测试设备(200)被配置为基于来自所述压力感测装置(130)的信号来标识所述第一本体(110)和所述多个第一探针(120)。

12.根据权利要求9所述的芯片测试系统(1000),其中所述测试设备(200)被配置为基于来自所述压力感测装置(130)的信号指示压力超过第二阈值而将所述第一本体(110)和所述多个第一探针(120)的已使用次数加一。

13.根据权利要求9所述的芯片测试系统(1000),其中所述插座组件(100)为根据权利要求7或8所述的插座组件(100),并且其中所述测试设备(200)被配置为基于所述至少一个第三探针(170)的连通信号来标识所述第二本体(140)和所述多个第二探针(150)。

14.根据权利要求9所述的芯片测试系统(1000),其中所述插座组件(100)为根据权利要求7或8所述的插座组件(100),并且其中所述测试设备(200)被配置为基于接收到所述至少一个第三探针(170)的连通信号而将所述第二本体(140)和所述多个第二探针(150)的已使用次数加一。

15.根据权利要求9所述的芯片测试系统(1000),其中所述测试设备(200)包括测试机(210)和附接到所述测试机(210)的第一电路板(220),并且所述第一电路板(220)包括将所述压力感测装置(130)电连接到所述测试机(210)的布线(221)。

16.根据权利要求9所述的芯片测试系统(1000),其中所述施压设备(300)包括推压头(310),并且所述推压头(310)适于按压所述待测试芯片(2000)的裸片(2100)。

17.根据权利要求16所述的芯片测试系统(1000),其中所述插座组件(100)为根据权利要求7或8所述的插座组件(100),并且其中所述施压设备(300)还包括附接到所述推压头(310)的第二电路板(340)。

技术总结

本公开的实施例提供了用于芯片测试的插座组件以及芯片测试系统。该插座组件包括:第一本体;多个第一探针,穿过第一本体,多个第一探针适于在第一本体的第一表面处受到待测试芯片按压、并且在第一本体的第二表面处按压测试设备,以电连接待测试芯片和测试设备;以及压力感测装置,被布置为感测多个第一探针中的至少一部分第一探针所承受的压力。本公开的方案可以在芯片测试过程中对芯片所承受的压力进行实时监测以避免测试过程中发生质量事故,并且还可以实现测试硬件的寿命监测。

技术研发人员:尹鹏飞,李春雷,孙斌,任延增,王伟君

受保护的技术使用者:华为技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!