一种砷化镓基集成电路工艺下的去嵌入方法

1.本发明属于射频微波测量领域,具体涉及一种砷化镓基集成电路工艺下的去嵌入方法。

技术背景

2.现代无线通信系统正朝着高频,高速和小型化的方向发展,相应的射频器件也朝着高集成度的方向发展。由于射频集成器件更小的尺寸和更高的工作频率,测量时引入的引线及焊盘结构,在射频微波测量时对器件性能造成的影响往往较大。针对射频集成电路片上测量的去嵌入方法具有很高的实用性。

3.射频集成器件由复杂的半导体工艺制造而成,其物理尺寸为微米级。与之相关的测量为晶圆测量,即将器件所在的半导体晶圆固定于射频探针台上,借由显微镜观察操作,通过与矢量网络分析仪相连的微米级射频探针完成对器件的测量。

4.晶圆测量前的校准分为片外校准和片上去嵌,片外校准即使用矢量分析仪配套的标准件将测量时的参考面从矢量分析仪的端口处校准到射频探针尖端。片上去嵌即使用自制的校准件将测量时的参考面从射频探针尖端平移到待测器件的理想位置。

5.在文献1(j.v.butler,d.rytting,m.f.iskander,r.pollard and m.vanden bossche,"16-term error model and calibration procedure for on wafer network analysis measurements(mmics),"in ieee trans.microwave symposium digest,vol.3,no.12,pp.1125-1127,dec.1991.)中提出了一种16项误差模型的晶圆上测量的校准程序,由于考虑了待测件两侧的串扰,故其中八项误差是用来追索泄露误差的,对于无信号泄露系统,可大大简化误差模型,同时保证去嵌精度不变。

6.在文献2(c.liu,a.wu,c.li and n.ridler,"anew solt calibration method for leaky on-wafer measurements using a 10-term error model,"in ieee transactions on microwave theory and techniques,vol.66,no.8,pp.3894-3900,aug.2018.)中提出了一种10项误差模型的去嵌入方法,由于只考虑射频探针间的串扰,是一种对16项误差模型的简化,并且十分依赖匹配校准件的精度。

7.在无泄露串扰的系统中,保证去嵌精度的前提下,误差模型可进一步简化为八项误差模型。去嵌过程通过使用一套直通、反射和线校准件实现。待测件两侧的八项误差网络由校准件散射参数通过矩阵恒等,信号流分析的方法求解,最终根据散射参数级联原理完成对待测件散射参数的去嵌修正。

技术实现要素:

8.本发明的目的在于提出一种砷化镓基集成电路工艺下的去嵌入方法,该方法针对射频集成电路片上测量时引入的引线及焊盘结构对待测件散射参数测量结果造成的影响进行去嵌消除;通过直通,反射和线校准件的散射参数,经由去嵌算法的计算确定引线及焊盘结构引入的八项干扰误差,再根据散射参数的级联原理,最终完成去嵌。

9.实现本发明目的的技术解决方案为:第一方面,本发明提供一种砷化镓基集成电路工艺下的去嵌入方法,包括如下步骤:

10.步骤1、根据待测件引线及焊盘结构,构建直通、反射、线校准件;

11.步骤2、获取待测件及校准件的s参数;

12.步骤3、求解引线及焊盘结构引入的八项误差;

13.步骤4、根据所求八项误差完成对待测件s参数的去嵌入。

14.第二方面,本技术还提供了一种计算机设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现上述第一方面所述的方法。

15.第三方面,本技术还提供了一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现上述第一方面所述的方法。

16.与现有技术相比,本发明的有益效果为:

17.(1)本发明提出的去嵌算法借由黑盒理论分析得到,只关注焊盘和传输线引入的误差网络的端口散射参数矩阵,故无需对误差网络内部进行复杂建模,操作简便;

18.(2)本发明去嵌所用直通,反射和线校准件,无需依赖如匹配校准件这样精度要求很高的标准件,具有更好的去嵌精度和可重复性;

19.(3)本发明针对无泄露串扰的系统,进一步简化误差模型为八项误差模型,在保证去嵌精度的同时,去嵌算法更为简洁,去嵌程序在时间复杂度上更低。

附图说明

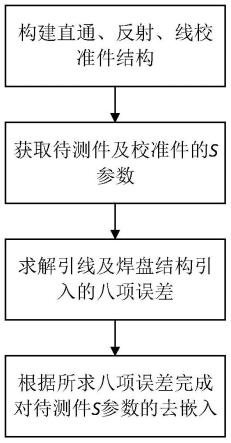

20.图1为本发明的实现流程图。

21.图2为本发明去嵌演示所用电感待测件的结构示意图。

22.图3为本发明去嵌演示中待测件测量所需引入的引线和焊盘结构示意图,是去嵌应消除的误差网络部分。

23.图4(a)为直通校准件结构示意图,图4(b)为反射校准件结构示意图,图4(c)为线校准件结构示意图。

24.图5(a)为直通件级联t参数矩阵示意图,图5(b)为线校准件级联t参数矩阵示意图,图5(c)为反射校准件端口归一化电压示意图。

25.图6(a)为s

11

实部去嵌结果图,其中图6(b)为s

11

虚部去嵌结果图。

26.图7(a)为s

21

实部去嵌结果图,其中图7(b)为s

21

虚部去嵌结果图。

27.图8(a)为s

11

相位去嵌结果图,图8(b)为s

21

相位去嵌结果图。

具体实施方式

28.如图1所示,本发明提出一种砷化镓基集成电路工艺下的去嵌入方法,包括:根据待测件引线及焊盘结构构建直通、反射、线校准件;获取待测件及校准件的s参数;将待测件及校准件的s参数导入计算机去嵌程序;求解引线及焊盘结构引入的八项误差;根据所求八项误差完成对待测件s参数的去嵌入。

29.该方法针对二端口射频集成电路测量时引入的引线和焊盘结构对原电路性能造成的影响,采用一套直通、反射、线校准件,对测量结果进行去嵌入,以还原出射频集成电路

原本性能。

30.构建校准件有如下过程:将待测件两侧引入的引线及焊盘结构直接连通,构成直通校准件;将待测件两侧引入的引线及焊盘结构水平放置,并保持一定间距实现终端开路,构成反射校准件;将待测件两侧引入的引线及焊盘结构水平放置,并在中间连上一段等宽的传输线,构成线校准件,为了避免去嵌结果产生相位模糊,要求传输线长度引起的相位延迟不超过160

°

。

31.获取待测件和校准件的s参数并导入计算机去嵌程序,将待测件和校准件的s参数转化为t参数以备后续对误差网络八项误差的求解;具体为:

32.将直通校准件和线校准件的s参数矩阵转化成级联t参数矩阵;

33.根据t参数的级联原理,有直通件t参数矩阵等于待测件两侧误差网络t参数矩阵级联,线校准件t参数矩阵等于待测件两侧误差网络t参数矩阵中间与延长线t参数矩阵级联;根据这两个矩阵恒等关系联立方程组,求解出待测件两侧误差网络的误差项e1、e2;

34.根据直通件t参数矩阵等于待测件两侧误差网络t参数矩阵级联的恒等关系,通过代入误差项e1、e2并消元化简,求解出待测件两侧误差网络的误差项e3、e4、e5、e6;

35.根据反射校准件两端口的级联t参数矩阵运算规则,端口1归一化电压波等于反射件网络级联t参数矩阵乘以端口2归一化电压波,得到反射校准件端口散射参数、终端反射率和反射件级联t参数关于端口归一化电压波的表达式,经消元化简求出待测件两侧误差网络的误差项e7、e8。

36.对八项误差的求解有如下过程:设待测件左右焊盘和引线引入的t参数误差矩阵ta、tb为ta、tb即为所要求取的误差矩阵,其中a、b、c、d、e、f、x

22

、y

22

为所设待测件左右焊盘和引线引入的t参数误差矩阵的未知量,是所要求取的八项误差;将直通校准件和线校准件的s参数矩阵转化成级联t参数矩阵t

t

和t

l

,有其中t

t

和t

l

为直通件和线校准件的级联t参数矩阵,为测量已知量,线校准件级联t参数矩阵t

l

由左右误差网络和中间延长线的t参数矩阵级联构成,根据传输线理论为线校准件延长线的t参数矩阵,其中γ是传输线传播常数,l是传输线长度,后续计算可通过消元去除,无需已知;是线校准件t参数矩阵乘直通校准件t参数矩阵的逆,为已测量知量;反射件输入端口处回波损耗为s

r11

、s

r22

均为已知量。

37.根据t

t

=ta*tb、的矩阵等式关系代入消元得的矩阵等式关系代入消元得即为:

[0038][0039]

根据以上矩阵恒等关系并通过消元去除得到关于误差项e1、e2的方程组:

[0040][0041]

其中e2=b,t

l

为线校准件延长线的t参数矩阵,无需已知;误差项e1、e2即为上述方程的解。

[0042]

根据t

t

=ta*tb的直通件级联关系有如下矩阵等式:

[0043][0044]

根据以上矩阵恒等关系求解出下述四个误差项:

[0045][0046][0047]

由反射校准件两端口级联t参数矩阵与端口归一化电压波关系得:

[0048][0049][0050]

其中a

ij

、b

ij

为反射校准件端口处归一化电压波,i为反射校准件输入端口编号,j为单侧反射件端口编号。反射件末端开路处反射系数为γr,无需知晓。通过消元、化简求得误差项如下:

[0051][0052]

根据所求八项误差完成对待测件s参数的去嵌入,具体包括:将待测件s参数矩阵转化为t参数矩阵以备后续运算处理;通过t参数级联关系修正得到待测件去嵌后t参数矩阵等于待测件未去嵌的t参数矩阵两侧乘以由误差项e

1~

e8确定的待测件两侧误差网络t参数矩阵的逆矩阵;将待测件去嵌后所得t参数矩阵转化成s参数矩阵输出。

[0053]

完成e1~e8的八项误差求解后,根据散射参数级联原理,待测件去嵌后t参数矩阵表述如下:

[0054][0055]

其中t

de-embed

是待测件去嵌后所得t参数矩阵,ta、tb是待测件左右焊盘和引线引入的级联t参数误差矩阵,t

dut

是待测件未去嵌的t参数矩阵。

[0056]

最后,将待测件去嵌后的t参数矩阵转化为s参数矩阵输出,即完成了对待测件s参数的去嵌入。

[0057]

下面结合附图和实施例对本发明作进一步说明。

[0058]

实施例

[0059]

如图1所示,本发明一种砷化镓基集成电路工艺下的去嵌入方法,其实现分为四个步骤:构建直通、反射和线校准件结构;获取待测件和校准件s参数;求解焊盘和引线引入的八项误差;根据所求八项误差完成对待测件s参数的去嵌入。

[0060]

校准件的构建分为三步:将待测件两侧引入的引线及焊盘结构直接连通,构成直通校准件;将待测件两侧引入的引线及焊盘结构水平放置,并保持一定间距实现终端开路,构成反射校准件;将待测件两侧引入的引线及焊盘结构水平放置,并在中间连上一段等宽的传输线,构成线校准件,为了避免去嵌结果产生相位模糊,要求传输线长度引起的相位延迟低于160

°

,相位对应的频率范围即去嵌适用的频率范围,其具体长度通过电磁仿真软件确定。

[0061]

将待测件及校准件的s参数输入计算机,然后将待测件s参数矩阵转化为t参数矩阵t

dut

,直通件s参数矩阵转化为t参数矩阵t

t

,线校准件s参数转化为t参数矩阵t参数矩阵t

l

,以备后续去嵌程序进行处理。

[0062]

如图5(a)、图5(b)、图5(c)所示为直通、线和反射校准件的t参数误差网络级联示意图和端口归一化电压波示意图。根据t

t

=ta*tb、t

l

=ta*t

l

*tb的矩阵恒等关系,及反射校准件两端口级联t参数矩阵与端口归一化电压波的关系,进一步分析求解得到待测件两侧误差网络的八项误差,其具体结果表达式如下:

[0063][0064][0065][0066][0067][0068][0069][0070][0071]

其中t

t

、t

l

是直通件和线校准件的t参数矩阵,t

l

为线校准件延长线的t参数矩阵,无需已知,s

r11

、s

r22

是反射件两端口处的回波损耗。有已知量是反射件两端口处的回波损耗。有已知量

[0072]

由所求八项误差确定的待测件两侧的误差网络的t参数矩阵

其中x

22y22

=e3。

[0073]

根据所求误差网络与其在待测件中的级联关系,完成对待测件t参数矩阵的去嵌入,待测件去嵌后的t参数矩阵t

de-embed

表述如下:

[0074][0075]

其中ta、tb是待测件左右焊盘和引线引入的级联t参数误差矩阵,由所求八项误差确定,t

dut

是待测件未去嵌的t参数矩阵。

[0076]

最终,将去嵌后的t参数转化为s参数输出,并绘制去嵌结果图,完成对待测件散射参数的去嵌入。

[0077]

如图2所示为待去嵌的电感待测件,它是采用砷化镓基集成电路工艺的一个平面螺旋电感,其基底上的金属层为三层金属与化合物的复合结构。其砷化镓基底1厚度为100um,接地焊盘2为80

×

75um,接地焊盘与信号焊盘间距3为50um,信号焊盘4为65

×

75um,接地柱5将接地焊盘与砷化镓基底下方信号地连通。作为通用去嵌入方法的演示,待测电感6尺寸随机,信号引线7长度随机。

[0078]

如图3所示为待测电感测量所需引入的焊盘和引线,为去嵌入所要消除的对测量结果产生影响的结构。其中砷化镓基底1厚度为100um,接地焊盘2为80

×

75um,接地焊盘与信号焊盘间距3为50um,信号焊盘4为65

×

75um,信号引线5长度为150um,宽度为10um,与待测电感线宽一致,接地柱6将接地焊盘与砷化镓基底下方信号地连通。

[0079]

如图4(a)~图4(c)所示为根据待测电感测量所需引入的焊盘和引线结构确定的校准件结构,其中图4(a)为直通校准件,砷化镓基底1厚度为100um,接地焊盘2为80

×

75um,接地焊盘与信号焊盘间距3为50um,信号焊盘4为65

×

75um,信号引线5长度为300um,宽度为10um,接地柱6将接地焊盘与砷化镓基底下方信号地连通。图4(b)为反射校准件,基底、焊盘和接地柱结构与直通件相同,其中终端开路引线7长150um,宽10um。图4(c)为线校准件,基底、焊盘和接地柱结构与直通件相同,其中连接线8长800um,宽10um。

[0080]

图5(a)为直通件级联t参数矩阵示意图,测量直通件两端散射参数矩阵,其由误差网络ta、tb级联构成;图5(b)为线校准件级联t参数矩阵示意图,测量线校准件两端散射参数矩阵,其由误差网络ta、tb和线校准件延长线t参数矩阵级联构成;图5(c)为反射校准件端口归一化电压示意图,测量得到反射校准件两端的回波损耗s

r11

、s

r22

。

[0081]

待测件及校准件结构准备完毕并获取待测件及校准件的散射参数后,将待测件及校准件的散射参数导入计算机,经由前文详述的去嵌算法程序处理完成去嵌,最终输出去嵌结果图。

[0082]

图6(a)~图6(b)为s

11

参数的去嵌结果图,其中图6(a)为s

11

实部去嵌结果图,其中图6(b)为s

11

虚部去嵌结果图。

[0083]

图7(a)~图7(b)为s

21

参数的去嵌结果图,其中图7(a)为s

21

实部去嵌结果图,其中图7(b)为s

21

虚部去嵌结果图。

[0084]

图8(a)~图8(b)为相位的去嵌结果图,其中图8(a)为s

11

相位去嵌结果图,图8(b)为s

21

相位去嵌结果图。

[0085]

图例中expected曲线为不包含引线和焊盘结构的待测电感散射参数,dut曲线为待测件未去嵌的散射参数,de-embed为去嵌后输出的散射参数。去嵌结果显示在5~30ghz频段内,去嵌误差保持在5%以内,对待测件的散射参数去嵌效果良好。

[0086]

以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本技术专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1